Устройство цифроаналогового преобразования

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной и цифровой измерительной техники и может быть использовано для преобразования цифровых величин в аналоговые. Изобретение позволяет повысить быстродействие и расширить область применения за счет преобразования обычного двоичного кода устройством, выполненным на базе избыточного измерительного кода , что обеспечивается введением цифрового коммутатора, блока определения разности кодов, второго регистра и регистра сдвига. Измеренные на этапе изготовления коды реальных весов всех разрядов цифроаналогового преобразо- -вания записываются в блок постоянной памяти и затем используются при преобразовании входного двоичного кода в рабочий избыточный измерительный код, который поступает на вход цифроаиалогового преобразователя. Повышение быстродействия обеспечивается за счет ускорения процесса преобразования входного кода в рабочий код. 1 з.п. ф-лы, 3 ил. 9

(gg 4 Н 03 М 1/66

%"

1

Ц Вйь. :

ОПИСАНИЕ ИЗОБРЕТЕНИЯ и Авчхя скому свидиальствм (21) 3806281/24-24 (22) 29.10.84 (46) 15.09.86. Бюл. 11 34

I (53) 681. 325 (088. 8) ГОСУДАРСТВЕННЬ1Й НОМИТЕТ СССР

ГЮ ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ1 (7 2) А.П. С тахо в, А.Д. Аз аров, В. П. Марценюк, В.Я. Стейскал и Н.А.Масленникова (56) Авторское свидетельство СССР

11 864548, кл. Н 03 K 13/02, 1981.

Авторское свидетельство СССР

1200422, кл. Н 03 М 1/66, 1985. (54) УСТРОЙСТВО ЦИФРОАНАЛОГОВОГО

ПРКОБРАЗОВАНИЯ (57) Изобретение относится к области вычислительной и цифровой измеритель. ной техники и может быть использовано для преобразования цифровых вели„„SU„„257 47 А 1 чин в аналоговые. Изобретение позволяет повысить быстродействие и расширить область применения за счет преобразования обычного двоичного кода устройством, выполненным на базе избыточного измерительного кода, что обеспечивается введением цифрового коммутатора, блока определения разности кодов, второго регистра и регистра сдвига. Измеренные на этапе изготовления коды реальных весов всех разрядов цифроаналогового преобразо.вания записываются в блох постоянной памяти и затем используются при преобразовании входного двоичного кода в рабочий избыточный измери=ельный код, который поступает на вход цифроаналогового преобразователя.

Повышение быстродействия обеспечивается sa счет ускорения процесса преобразования входного кода в рабочий коде 1 зепа ф лы 3 HJI

1257847

Ф 2

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые ° 5

Цель изобретения — повышение быстродействия и расширение области применения за счет преобразования двоичного кода.

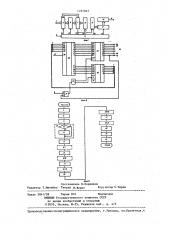

На фиг.I приведена функциональная схема устройства и цифроаналогового преобразования; на фиг.2— функпиональная схема блока управления; на фиг.3 — граф-схема алгоритма работы блока управления.

Устройство цифроаналогового преобразования (фиг.1) содержит входные шины 1 преобразуемого кода, цифровой коммутатор (ЦК) 2, управляющий вход 3, блок 4 управления (БУ ),первый и второй регистры (РГ) 5 и 6,блок 7 определения разности кодов (БОР), блок 8 постоянной памяти (БПП), регистр 9 сдвига (РГС), цифроаналоговый преобразователь (ЦАП)

10, выходную шину 11.

Блок 4 управления содержит первый выход 12, вторые выходы 13,. третий, четвертый и пятый выходы 14, 15, 16 и первый вход 17. 30

Блок 4 управления (фиг. 2) выполнен на первом и втором регистрах 18 и 19, генераторе 20 тактовых импульсов, RS-триггере 21 и постоянном запоминающем устройстве 22. 35

Цифроаналоговый преобразователь

10 выполняется на основе избыточного измерительного кода.

На этапе изготовления устройства цифроаналогового преобразования про- 40 изводится измерение реальных весов разрядов ЦАП 10 и запись кодовых эквивалентов измеренных значений в.блок, 8 постоянной памяти. В процессе преоб- разования эти коды используются для 45 коррекции преобразуемого входного кода. Повышение быстродействия устройства обеспечивается за счет ускорения процесса преобразования входного кода в рабочий код, который пода-50 ется непосредственно на ЦАП 10. Входной код устройства цифроаналогового преобразования является обычным, широко распространенным двоичным кодом, что существенно расширяет об- 55 ласть применения устройства.

Устройство работает следующим образом.

3 Начало преобразования

При У1=1 коммутируется вход 1

14 Коммутация У!

ЦК

Исходный код К, поступающий на входные шины 1, с помощью блоков 2, 6, 7, 8,. 9, 4 преобразуется в код реальных значений весов разрядов Кр.

Для этого код К через ЦК 2 записывается во второй регистр 6 и в блоке 7 определения разности кодов сравнивается с кодовыми эквивалентами реальных значений разрядов, записанных в блоке 8 постоянной памяти. Сравнение осуществляется выполнением операции вычитания над кодами, поступающими на информационные входы БОР 7, и анализом знака полученной разности. Если исходный код К больше двоичного эквивалента веса разряда N,, то разность (К-11L) получается положительйой, величина ее переписывается во второй регистр 6 и на последующем этапе сравнение происходит с этой разностью. Если входной код

К меньше двоичного эквивалента И,, то разность (K-И;) будет отрицательной и во второй ре;истр значение ее не переписывается.

Начинается сравнение с двоичного эквивалента старшего разряда и повторяется для всех разрядов .

Знак разности после каждого этапа сравнения записывается в регистр 9 сдвига 1,в случае -положительной разнос ти запишется единичное значение, иначе нулевое).

Код, образованный в РГС 9 после выполнения всех этапов сравнения, является кодом реальных значений или рабочим кодом Кр. Полученный рабочий код переписывается в первый регистр

5, управляющий включением разрядов

ЦАП 10. При этом на выходе 11 устройства появляется аналоговая величина, значение которой соответствует входному двоичному коду К.

В таблице приведены необходимые для функционирования устройства управляющие и условные сигналы.

1257847

Продолжение таблицы

1 (2

15 Синхроимпульс РТ6 У2

13 Адрес БПП 8 УЗ

У4

1О

У5

Сдвиг соУ6 держимого

РГС

1 6 Синхроимпульс РГС 9

12 Синхроимпульс РГ5

У7

Х1 = 1-разность по17 Признак знака разности ложительна формула изобретения 4О

1. Устройство цифроаналогового преобразования, содержащее первый регистр, управляющий вход которого. подключен к первому выходу блока уп- 45 равления, выходы — к соответствующим входам цифроаналогового преобразователя, выход которого является выходной шиной устройства, вторые выходы блока управления подключены к соот- 5О ветствующим адресным входам блока постоянной памяти, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия и расширения области применения за счет обеспечения преобразования двоичного кода в него введены второй регистр, блок определения разности кодов, регистр

Алгоритмы функционирования цифроаналогового преобразователя в со25 ответствии с приведенным описанием приведены на фиг.3, где вершина 1 запись исходного кода К в РГ6; вершина 2 — установка адреса на считывание из БПП 8 двоичного эквивалента старшего разряда; вершины 3,4,6,7, 9,10,12,13,15,16,18,19,21 — сравнение и запись результата в РГ6; вершины 5,8,11,14,17,20 — установка адреса на считывание из БПП 8 двоич- З ного эквивалента следующего разряда; вершина 21 — перепись рабочего кода Кр в РГ5. сдвига, цифровой коммутатор, первые информационные входы которого являются шинами преобразуемого кода, вторые информационные входы подключены к соответствующим первым выходам блока определения разности кодов, управляющий вход подключен к третьему выходу блока управления, выходы — к соответствующим информационным входам второго регистра, управляющий вход :. которого подключен к четвертому выходу блока управления, выходы подключены к соответствующим первым входам блока определения разности кодов, вторые входи которого подключены к со соответствующим выходам блока посто-. янной памяти, второй выход — подключен к первому входу блока управления н информационному входу регистра сдвига, выходы которого подключены к соответствующим информационным входам первого регистра, управляющий вход— к пятому выходу блока управления, второй вход которого является управляющим входом устройства.

2. Устройство по п. 1, о т л и—

Р ч з ю щ е е с я тем, что блок уп1 равления выполнен на первом и втором регистрах, генераторе тактовых импульсов, RS-триггере, постоянном запоминающем устройстве, выходы с первого по седьмой которого подключены к соответствующим информационным входам первого регистра, выходы с восьмого по двенадцатый подключены к соответствующим информационным входам второго регистра, входы с первого по пятый — к соответствующим выходам второго регистра, управляющий вход которого подключен к инверсному выходу генератора тактовых импульсов, управляющий вход которого подключен к выходу RS-триггера, прямой выход— к управляющему входу первого регистра, первый выход которого является третьим выходом блока управления, второй выход — четвертым выходом блока управления, выходы с третьего по пятый — вторыми выходами блока управления, шестой выход — пятым выходом блока управления, седьмой выход — первым выходом блока управления и подключен к R-входу RS-триггера, S-вход которого является вторым входом блока управления, при этом шестой вход постоянного запоминающего устройства является первым входом блока управления.

1257847

Г

1

1 фивы

Составитель В.Першиков

РедактоР Т.Митейко ТехРед И.Верес Корректор С.Черни

Заказ 504!/58 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1)3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Ужгород, ул.Проектная.4