Устройство для сопряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной технике и может быть использовано для сопряжения двух разноскоростных устройств обработки данных при одновременном поступлении синхросигналов записи и считывания. Целью изобретения является повьппение надежности устройства Устройство содержит два счетчика синхроимпульсов, комму таторы ввода-вывода информации, буферную память, группу элементов НЕ, комбинационный сумматор, элементы И, ИЛИ-НЕ, 1 ил. ю ел

. СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (50 4 0 06 Р 13 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /;.;

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (2l) 3867588/24-24 (22) 15.03.85 (46) 23.09.86. Бюл. У 35 (72) А. И. Багрич и Н.. А. Шумаков (53) 681,3(088.8)

{S6) Авторское свидетельство СССР

9 752321, кл. 6 06 Р 3/04, 1978.

Авторское свидетельство СССР

У 881722, кл. 0 06 F 3/04, 1981„ (54) УСТРОЙСТВО ДЛЯ. СОПРЯЖЕНИЯ (57) Изобретение относится к области автоматики н вычислительной тех„„SU„„3 259275 А 1 нике и может быть использовано для сопряжения двух разноскоростных устройств обработки данных при одновременном поступлении синхросигналов записи и считывания. Целью изобретения является повышение надежности устройства. Устройство содержит два счетчика синхроимпулъсов, коммутаторы ввода-вывода информации, буферную память, группу элементов НЕ, комбинационный сумматор, элементы И, ИЛИ-НЕ, 1 ил.

30 1 12592

Изобретение относится к автомати- ке и вычислительной технике и может быть использовано для сопряжения двух разноскоростных устройств обработки данных, S

Цель изобретения — повышение надежности рабочего устройства при вводе-выводе информации и одновременном поступлении синхросигналов записи и считывания. !О

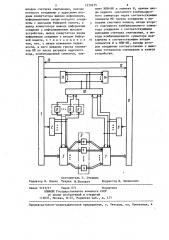

На чертеже представлена конструкция устройства.

Устройство содержит источник 1 информации, счетчик 2 записи, коммутатор 3 ввода информации, регистры 4 буферной памяти 5, счетчик 6 считывания, коммутатор 7 выводы информации, приемник 8 информации, группу элементов НЕ 9, комбинационный сумматор 10, элемент ИЛИ-НЕ 11, 20 вход 12 приемника 8, вход 13 источника 1 и элемент И 14, Устройство работает следующим образом.

Перед процессом передачи после- 25 довательности дискретных сигналов источник 1 посылает сигнал "Запрос на прием" на вход 12 приемника 8, который на данный сигнал выдает на вход 13 -источника 1 сигнал "Готов к приему". После этого источник i генерирует последовательность кодов, которые поступают на вход коммутатора 3. Одновременно каждый сигнал последовательности сопровождает, синхроимпульс записи, который поступает на вход счетчика 2, выдающий адреса для подключения входа коммутатора З.к соответствующему регистРУ 4 бУфеРной памяти 5. Адресньге rco 40 ды с выхода счетчика 2 через группу элементов HE 9 поступают также на вход первого слагаемого комбинационного сумматора 10. Таким образом, с записью первого сигнала последова- 44 тельности, т.е. с,появлением первого синхроимпульса записи на вьжоде элемента И 14. формируется сигнал "Готовность считывания информации", ко" торый разрешает считывание информации приемнику 8.

С появлен!гем на тактовом входе счетчика 6 импульсов считывания он выдает адрес на коммутатор 7, кото, рый подключает выход соответствующего регистра 4 буферной памяти 5 на вход приемника 8 синхронно с импульсами считывания. Счетчик 6 совмест75 2 но с коммутатором 7 работает таким образом, что считывание сигналов происходит аналогично их порядку записи. Адресные коды с выхода с .етчика 6 поступают также на вход вто-, рого слагаемого комбинационного сумматора 10. Таким образом, в процессе записи и считывания на выходе комбинационного сумматора получается инверсия кода, равного количеству регистров 4 памяти 5, в которых хранится еще несчитыванная информация °

Так как запись и считывание происходят с различной скоростью, то в буферной памяти 5 может не оставаться свободного регистра для записи последующего кода. Этот момент определяется элементом ИЛИ-НЕ 11 при наличии на выходе сумматора 10 нулевого кода. С выхода элемента ИЛИНЕ 11 выдается сигнал блокировки записи, который поступает на соответствующий вход источника 1 и запрещает выдачу кодов на вход коммутатора 3 и соответствующих синхроимпульсов, После считывания информации хотя бы из одного регистр.". 4, изменяется код на выходе сумматора 10 и снимается сигнал блокировки записи с выхода элемента ИЛИ-НЕ 11.

Запись будет продолжена в свободные регистры, т ° е. B регистры, информация в которых была считана.

Если считывание происходит быстрее записи, то при наличии на вьгходе сумматора 10 единичного кода, что означает отсутствие несчитанной информации в регистрах 4, элемент И 14 выдает в приемник 8 сигнал блокировки чтения, Сигнал будет сохраняться до тех пор, пока информация не будет записана хотя бы в один регистр.

Формула изобретения УсЧ ройство для сопряжения, содер" жащее буферную память, счетчики записи и считывания, коммутаторы ввода и вывода информации, причем информационный вход коммутатора ввода информации соединен с информационным входом устройства, адресные входы коммутатора ввода информации соединены с выходами счетчика записи, тактовой вход которого соединен с первым синхронизирующим входом устройства, второй синхронизирующий вход которого соединен с тактовым

Составитель Г. Стернин

РедактоР Н. Яцола ТехРед И.Попович Корректор Л. Пилипенко

Заказ 5123/47 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 входом счетчика считывания, выходы которого соединены с адресными входами коммутатора вывода информации, информационные входы которого соединены с выходами буферной памяти, а выход коммутатора вывода информации соединен с информационным выходом устройства, выход коммутатора ввода информации соединен с входом буферной памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности, в него введены группа элементов НЕ по числу разрядов адресного кода, комбинационный сумматов, эле259275 Д мент ИЛИ-НЕ и элемент И, причем входы первого слагаемого комбинационного сумматора через соответствующие элементы НЕ группы соединены с вы" ходами счетчика записи, входы второго .слагаемого комбинационного сумматора соединены с соответствующими выходами счетчика считывания, а выходы комбинационного сумматора подt0 ключены к соответствующим входам элементов И и ИПИ-НЕ, выходы которых соединены соответственно с выходами готовности считывания и записи устройства,