Устройство для решения алгебраических уравнений

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники, в частности к устройствам специализированного назначения для решения уравнений. Целью изобретения является повьшение быстродействия. Устройство содержит сумматор, комбинационный умножитель, группу D -триггеров и блок формирования сигнала. При выполнении операции в устройстве такт работы на каждом шаге решения будет минимальным и определяется блоком формирования сигналов синхронизации , определяющим наличие или отсутствие процесса в сумматоре. 3 ил. с S

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК пд 4 С 06 F 15/32, 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /;-„:

ГОСУДАРСТ8ЕНН 1Й КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3801803/24-24 (22) 15.10.84 (46) 23.09.86. Вюл. Ф 35 (71) Институт проблем моделирования в энергетике АН УССР (72) В.Ф.Евдокимов, Ю.А.Плющ, Н.Ю.Пивень, А.П.Стеканов и З.А.Джирквелишвили (53) 681.14 (088.8) (56) Авторское свидетельство СССР

Ф 428405, кл.G 06 С 7/34, 1974.

Авторское свидетельство СССР и 798861, кл. С 06 Р 15/,324, 1978. (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ (57) Изобретение относится к области цифровой вычислительной техники, . в частности к устройствам специализированного назначения для решения уравнений. Целью изобретения является повышение быстродействия. Устройство содержит сумматор, комбинационный умножитель, группу D -триггеров и блок формирования сигнала. При выполнении операции в устройстве такт работы на каждом шаге решения будет минимальным и определяется блоком формирования сигналов синхронизации, определяющим наличие или отсутствие процесса в сумматоре. 3 ип.

l?59?86

f0 !

20 х=Вх+Г относительно х:

Х

1- В

Изобретение относится к вычислительной технике и может быть использовано в устройствах специализированного назначения для решения уравнений.

Цель изобретения — повышение быстродействия.

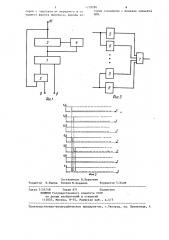

На фиг.! изображена функциональная схема устройства для решения алгебраических уравнений; на фиг.2 функциональная схема блока формироI вания сигнала синхронизации; на фиг.3 — временные диаграммы работы этого блока.

Устройство содержит сумматор 1, комбинационный матричный умножитель

2, группу Л -триггеров 2 (образующих регистр) и блок 4 формирования сигнала синхронизации, содержащий

N одновибраторов 5 с запуском от переднего фронта импульсов (ll — разрядность результата), Й одновибраторов 6 с запуском от заднего фронта импульса и элемент ИЛИ 7. Устройство имеет входы 8 значения коэффициента при неизвестном уравнения, входы 9 значения свободного члена уравнения и выходы 10.

Устройство предназначено для ре— шения уравнения. а

Входы 8 и 9 устройства предназначены для приема значений В и соответственно. Выходы 10 служат для выдачи значения искомого числа х. Умножитель 2 предназначен для умножения числа х на число В.

Сумматор 1 предназначен для суммирования полученного произведения с числом F

Устройство работает следующим образом.

При изменении значения любого разряда в одном или обоих из чисел

В и F на выходах сумматора 1 начинает изменяться соответствующий разряд числа х . При этом блок 4 вырабатывает сигнал, который запрещает перезапись изменяющегося значения х до окончания переходного процесса в сумматоре 1 в D -триггеры 3. После того, как выходы сумматора 1 примут устойчивое состоя25

ЗО

55 ние, блок 4 вырабатывает значение сигнала синхронизации, производящего перепись полученного нового значения числа х в D -триггеры 3.

Это измененное значение вызывает изменение результата на выходах умножителя 2, что, в свою очередь, изменяет какой-либо из разрядов числа х, на выходах сумматора l, и вновь блок 4 запрещает перезапись изменяющегося значения х до окончания переходного процесса в сумматоре l. Таким образом процесс установления схемы повторяется до тех пор, пока на выходах сумматора l не установится значение x„, равное значению на выходах Л -триггеров 3 °

Работа блока 4 поясняется приве— денной временной диаграммой. формул а изобретения

Устройство для решения алгебраических уравнений, содержащее сумматор, комбинационный матричный умножитель, группу Л -триггеров, н блок формирования сигнала синхронизации. выход которого соединен с входами синхронизации D -триггеров группы, информационные входы которых соединены с выходами соответствующих разрядов сумматора, входы которого соединены с входами значения свободного члена уравнения устройства и выходами комбинационного матричного умножителя, входы которого соединены с входами значения коэффициента при неизвестном уравнении устройства и выходами З -триггеров группы, входы блока формирования сигнала синхронизации соединены с выходами разрядов сумматора, выходы

D-триггеров группы являются выходами устройства, блок формирования сигнала синхронизации содержит одновибратор с запуском от переднего фронта импульса, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в блок формирования сигнала синхронизации введены (N-I) одновибраторов с запуском от переднего фронта импульса (N— разрядность результата), М одновибраторов с запуском от заднего фронта импульса и элемент ИЛИ, выход которого соединен с выходом блока формирования сигнала синхрониза— ции, каждый вход которого соединен с входами соответствующих одновибра1259286 торых соединены с входами элемента

ИЛИ. торов с запуском от переднего и от заднего фронта импульса, выходы ко1

Фиг.2 л, Лг

Составитель В.Березкин

Редактор Н.Яцола Техред М.Ходанич Корректор Т.Колб

Заказ 5124/48 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r.Óæãoðîä, ул. Проектная, 4