Запоминающее устройство с сохранением информации при отключении питания

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано пои создании запоминающих устройств. Изобретение позволяет исключить разрушение информации в запоминающем устройстве (ЗУ) как при отключении питания, так и при кратко временном его пропадании,(импульсная помеха). Сигнал блокировки вырабатывается триггером и через элемент задержки коммутирует переключатель, который блокирует подачусигнала выборки кристалла в ЗУ. Питание триггера осуществляется от резервного источника питания, что обеспечивает надежное срабатывание блокировки, игнал блокировки анализируется в блоке управления и блокирует сигналы управления ЗУ. Разблокировка триггера осуществляется внешним сигналом по програм1 е или вручную. 4 ил. сл N9 СП СО со -

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1259342 А1

LSD 4 С 11 С 2 00

ОПИСАНИЕ ИЗОБРЕТЕНИ Я

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3879862/24-24 (22) 04.04.85 (46) 23.09.86. Бюл. 9 35 (7 1) Минский конструкторско-технологический экспериментальный институт автомобильной промьппленности (72) П.К.Сырель и С.А.Гороховик (53) 681.327 (088.8) (56) Авторское свидетельство СССР

В 1083236, кл. G 11 С 29/00, 1984.

Авторское свидетельство СССР

У 842975. кл. G 11 С 29/00, 1981. (54) ЗАПОМИНАКМЦЕЕ УСТРОЙСТВО С СОХРАНЕНИЕМ ИНФОРМАЦИИ ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ (57) Изобретение относится к области вычислительной техники и может быть использовано пои создании запоминающих устройств. Изобретение позволяет исключить разрушение информации в запоминающем устройстве (ЗУ) как при отключении питания, так и при кратко временном его пропадании,(импульсная помеха). Сигнал блокировки вырабатывается триггером и через элемент saдержки коммутирует переключатель, который блокирует подачу сигнала выборки кристалла в ЗУ. Питание триггера осуществляется от резервного источника питания, что обеспечивает надежное срабатывание блокировки.

Сигнал блокировки анализируется в блоке управления и блокирует сигналы управления ЗУ. Разблокировка триггера осуществляется внешним сигналом по программе или вручную. 4 ил.

125934?

15 ъ0

Я

Изобретение относится к вычислительной технике.

Целью изобретения является повышение,надежности устройства.

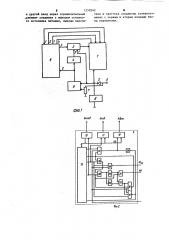

На фиг. 1 приведена функциональная схема запоминающего устройства;, на фиг. 2 — функциональна» схема блока управления; на фиг. 3 — временная диаграмма записи информации;на фиг,.4временная диаграмма чтения информации, Устройство содержит накопитель 1, элемент 2 развязки, переключатель 3, элемент 4 задержки, блок 5 управления, триггер 6, ограничительный элемент 7, резервный источник 8 питания и выход 9 основного источника питания.

Блок 5 управления (фиг. 2) содержит выходные вентили 10, регистр 11 данных, регистр 12 адреса, процессор

13, схемы 14-19 совпадения, схемы

ИЛИ 20 и 21, формирователь 22 импульсов, элемент 23 задержки и инвертор 24. Формирователь импульсов

22 построен на микросхеме К155 АГЗ.

Двунаправленный 16-ти разрядный ка.нал 25 данных адреса (КДА) соединяет между собой процессор 13, выходные вентили 10, регистр 11 данных и регистр 12 адреса.

Устройство работает следующим образом.

При номинальном напряжении на выходе 9 основного источника пита-ния, которое превьппает уровень срабатывания триггера 6, равный снижению питания íà 10-157 и устанавливаемый с помощью ограничительного элемента 7, с выхода триггера 6 на вход блока 5 управления поступает команда "Разрешение обращения" (например, логическая "1").

Одновременно сигнал с выхода триггера 6 через элемент 4 задержки управляет переключателем 3, с помощью которого сигнал "0" поступает с блока 5 управления на вход выборки кристалла накопителя 1. При этом происходит чтение (запись информаI ции, поступившей на информационный вход-выход накопителя по адресу, определяемому информацией поступившей на его адресный вход).

При снижении напряжения на выходе

9 основного источника питания ниже уровня срабатывания триггера 6 последний формирует сигнал "0", который, поступая на блок 5 управления, блокирует сигналы управления памятью, обращения к памяти и управления адресами, вырабатываемые этим блоком.

В то же время этот сигнал блокировки через элемент 4 задержки удер живает в выключенном состоянии переключатель 3, который коммутирует на вход выборки кристалла накопителя i сигнал высокого уровня "1" с выхода резервного источника 8 питания. Накопитель 1 находится в режиме минимального потребления тока в цепи питания, и обращение к нему заблокировано.

Если после срабатывания триггера

6 на управляющую шину поступает команда записи, то сигнал блокировки, поступивший на вход выборки кристалла накопителя 1, запрещает прохождение сигнала чтения/записи на вход накопителя 1, Таким образом, достигается блокировка сигналов обращения к ЗУ и переключения адресов и режи- мов работы ЗУ в момент последнего обращения, если оно было в момент отключения напряжения. Тем самым исключается возможчость появления на входе накопителя 1 укороченного сигнала чтения/записи, Разблокиронка триггера 6 производится внешним сигналом по программе или вручную с пульта подачей сигнала на второй вход триггера б (не показано) .

За счет того, что питание триггера аналогично питанию накопителя, а сигнал блокировки с выхода триггера, поступая на переключатель с задержкой, равной циклу обращения, коммутирует его таким образом, что на вход выборки кристалла накопителя поступает сигнал высокого уровня с выхода резервного источника питания и запрещает обращение к накопителю до тех пор, пока триггер не будет заблокирован внешним сигналом, удается повысить надежность устройства и снизить аппаратные затраты.

Блок 5 управления формирует управляющие сигналы в циклах записи и чтения следующим образом.

Цикл записи информации в накопитель 1 (фиг. 1)

Временная диаграмма цикла записи приведена на фиг, 3. Первоначально по команде "Выдача адреса" (ВА) процессором 13 формируется сигнал BA

12593

45 сопровождаемый сигналом сопровождение выдачи (СВ) (фиг. 2). При поступлении этих сигналов и отсутствии сигнала блокировки на выходе схемы 14 совпадения формируется сигнал записи в регистр 12 адреса.

Происходит перезапись адресной информации из внутреннего регистра процессора 13 в регистр 12 адреса, Если сработала блокировка, то она запрещает запись нового адреса в регистр 12 адреса, т.е. поступление новдй адресной информации в накопитель 1.

Сразу после сформирования сигнала записи адреса на выходе инвертора 24 формируется сигнал СП (синхронизация приема) о том, что адрес принят.

Процессор 13, получив сигнал СП, 20 снимает свой сигнал СВ. После этого процессор 13 по команде "Запись" (ЗП) формирует сигнал ЗП, который разрешает запись в регистр 11 данных, и информацию в канале 25 КДА, которую необходимо записать. Информация сопровождается сигналом СВ.

При совпадении сигналов ЗП и СВ формирователь 22 импульсов формирует импульс с длительностью, большей 30 или равной времени обращения к накопителю 1. Это необходимо для того, о чтобы сформировать сигнал СП после гарантированной записи информации в накопитель 1. Схема ИЛИ 21 формирует сигнал, разрешающий запись из регистра 11 данных в накопитель 1. Сигнал

СП по записи формируется схемой 19 совпадения и поступает на вывод СП процессора 13. При получении сигнала СП процессор 13 снимает сигналы

СВ и ЗП. Цикл записи окончен.

Цикл чтения информации из памяти (временная диаграмма фиг. 4)..Выдача адреса и запись адресной информации в регистр 12 адреса происходит аналогично с циклом записи информации. После того, как адресная информация записана в регистр 12 ад- 50 реса, процессор 13 на выводе ЧТ формирует сигнал "Чтение", который разблокирует выходные вентили 10. Сигнал ЧТ через схему ИЛИ 20 поступает на вход формирователя 22. Сигнал СВ, 55 выдаваемый процессору 13 при считывании информации,. формируется схемой

18 совпадения аналогично сигналу СП

42 4 при записи информации. Сигнал ВК (выбор кристалла) формируется схемой ИЛИ 21 сразу же после возникновения сигнала ЧТ. Задержка (F) в формировании сигнала СВ при чтении необходима для гарантированного считывания информации из накопителя 1.

Элемент 23 задержки при формировании сигналов СВ и СП компенсирует задержку в формировании импульса на формирователе 22.

Блокировка запрещает формирование сигналов СП при записи информации и

С — при ее чтении. Так как процес"ор 13 не получает этих сигналов, необходимых для асинхронного обмена, то выполнение программы останавлива-. ется и может быть возобновлено только при снятии блокировки.

Схема ИЛИ 21 позволяет оформить обращение к накопителю 1 в цикле записи импульсом, достаточным для гарантированного занесения информации в ЗУ, а в цикле чтения — по данному управляющему сигналу. Зто позволяет производить чтение и запись как в динамике от процессора 13 по программе, так и по командам в процессе отладки.

Формула изобретения

Запоминающее устройство с сохранением информации при отключении питания, содержащее накопитель, элемент развязки, переключатель, элемент задержки, триггер, резервный источник питания, выход которого подключен к первому входу накопителя, первому входу переключателя и одному из выводов элемента развязки, другой вывод которого соединен с выходом основного источника питания, выход переключателя соединен с вторым выходом накопителя, о т л и ч а ю щ е ес я тем, что, с целью повышения надежности„ в него введены блок управления и ограничительный элемент, причем выходы блока управления сое динены соответственно с третьим, четвертым, пятым входами накопителя и третьим входом переключателя, второй вход которого подключен к выходу элемента задержки, вход которого подключен к выходу триггера, один вход которого соединен с выходом резервного источника питания, 5 3259342 4 и другой вход через ограничительный теля и триггера соединены соответст.влемент соединен с выходом основно- венно с первым и вторым входамн благо источника пйтакия, выходы накопи- ка управления.

1 259342

Д алые

4 ес Данные

Составитель О. Кулаков

Редактор А.Ворович Техред М.Ходанич Корректор М.Шароши

Заказ 5128/50 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r.Óæãoðîä, ул.Проектная,4