Устройство для цифровой фильтрации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, в частности к обработке информации, и может быть использовано в устройствах приема информации , проходящей по каналу связи, в котором возможно искажение информации , т.е. есть шумы и помехи.. Цель изобретения - повьшение точности цифровой фильтрации в условиях йовьшенного содержания аномальных помех. Цель изобретения достигается за счет введения в устройство квадратора, трех умножителей, блока элементов И, трех регистров, дешифратора , элемента ИЛИ, блока вычисле- 1гая обратной величины, счетчика, блока сравнения с 2, триггера, элемента И, сдвигового регистра и синхронизатора . Устройство позволяет осуществлять цифровую фильтрацию, при этом достигается сглаживание входного сигнала в условиях аномальных, загрязненных в| 1бросами измерений с изменением на каждом 4ни1ьтрации коэффициента сглаживания. 3 ил. О) с: to СП S 1Й

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

Н A ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (2i) 3810782/24-24 (22) 10. 11.84 (46) 23.09.86. Бюл. У 35 (72) И.В.Семушин, А.А.Рогов, А.А.Иаслов, В.И.Сбоев и В.П.Полосенко (53) 681.32(088.8). (56) Авторское свидетельство СССР

9 783800ь кл. G 06 F 15/Збв 1978 °

Авторское свидетельство СССР

9 412606, кл. 6 06 F 15/36, 1974. (54) УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ФИЛЬТРАЦИИ (») Изобретение относится к области вычислительной техники, в частности к обработке информации, и может быть использовано в устройствах приема информации, проходящей по каналу связи, в котором возможно искажение ин„„SU„„1259477 А 1 ац4 Н 03 Н 21/О G 06 Р 15 353 формации, т.е. есть шумы и помехи. Цель изобретения — повышение точности цифровой фильтрации в условиях Повышенного содержания аномальных помех. Цель изобретения достигается за счет введения в.устройство .квадратора, трех умножителей, блока элементов И, трех регистров, дешифратора, элемента ИЛИ, блока вычисления обратной величины, счетчика, блока сравнения с "2", триггера, элемента И, сдвигового регистра и синхронизатора. Устройство позволяет осуществлять цифровую фильтрацию, при этом достигается сглаживание входного сиг- и нала в условиях аномальных, загрязненных выбросами измерений с изменением на каждом шаге фильтрации коэффициента сглаживания. 3 ил.

1259477

Изобретение относится к области вычислительной техники, в частности к обработке информации, и может быть использовано в устройствах приема информации, проходящей по каналу связи, в котором существует возможность искажения информации, т.е. имеют место шумы, помехи.

Целью изобретения является повышение точности цифровой фильтрации (в условиях повышенного содержания аномальных помех).

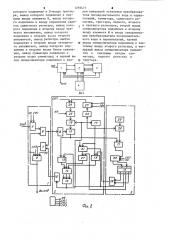

На фиг.1 изображена укрупненная блок-схема устройства для цифровой фильтрации; на фиг.2 — конкретная !

5 структурная схема устройства; на фпг.3 — временные диаграммы напряжений па синхровходах соответствующих узлов для пояснения работы устройства.

Устройство для цифровой фильтрации (фиг.1) состоит из блока 1 сглаживания, блока 2 определения коэффициента сглаживания, блока 3 анализа динамической о|шубки, синхронизатора 4.

Устройство для цифровой фильтра— ции («err . 2) содержит преобразоватетп., 5 последовательного кода в параллельный, вычитатель 6, умножитель

7, квадратор 8, сумматор 9, умножитель 10, блок 11 сравнения, блок 12 элементов И, дешифратор 13, блок 14 элементов ИЛИ, регистр 15, блок 16 вычисления обратной величины, счетчик 17, умножитель 18, блок 19 эле- . 35 ментов И, умпожитель 20, регистр 21, блок 22 сравнения с "2", триггер 23, элемент И 24, сдвиговый регистр 25, элемент ИЛИ 26, блок 27 элементов И, регистр 28 ошибки, регистр 29. 40

Устройство работает следующим образом.

До начала процесса фильтрации с синхронизатора 4 приходит одиночный импульс начальной установки. При этом 45 сумматор 9, регистр 21, триггер 23 и регистр 29, преобразователь 5 устанавливаются в нулевое состояние, регистр 15 — в единичное, в регистре

25 устанавливается обратное значение 50 удвоенной дисперсии измерений. Все остальные элементы: устройства комбинационные и не требуют начальной установки.

На каждом 1-ом шаге фильтрации с 55 приходом синхроимпульса первого последовательный код входного сигнала в преобразователе 5 преобразуется в параллельный код и хранится в нем до начала (i + 1)-го шага фильтрации.

Входной сигнал, пройдя преобразования в блоках 6,8 и 10, определяет на выходе блока 10 значение нормированного квадрата невязки до прихода синхроимпульса второго. За это время в блоках устройства проходят следующие процессы. В блоке 11 нормированный квадрат невязки сравнивается со скользящим порогом аномальности, значение которого будет на выходе блока 20 до прихода синхроимпульса второго. Если нормированный квадрат невязки больше скользящего порога аномальности, то единица с выхода блока

11 запишется в младший разряд регистра 29, в старшем разряде которого результат сравнения — на (i 1)-ом шаге. После этого блоки 13 и 26 по четырем возможным комбинациям в разрядах регистра 29 определяют одно из трех условий выбора коэффициента сглаживания: аномалий не было и нет или они продолжаются при комбинации в регистре 29 "00" или "11"; конец аномалий при комбинации "10"; начало аномалий при комбинации "01". В первом случае сигнал разрешения подается на блок 19, который через блок

14 подает на вход регистра 15 значение обратной величины i-го предварительного коэффициента сглаживания с блока 17. Во втором случае сигнал разрешения подается на блок 27, который через блок 14 подает на вход регистра 15 с регистра 21 обратную величину предварительного коэффициента сглаживания того шага фильтрации, с которого началась последняя встретившаяся непрерывная группа аномальных сигналов. В третьем случае сигнал разрешения подается на блок

12 который через блок 14 подает на вход регистра t5 со схемы 10 значение нормированного квадрата невязки, кроме того, подается сигнал на синхровход регистра 21 для записи в

nего обратной величины предварительного коэффициента сглаживания с блока 17 в момент обнаружения начала аномалий. Одно из трех возможных значений обратной величины коэффициента сглаживания в зависимости от результатов сравнения в блоке 11 íà i-ом и (i-1)-ом шаге, записывается в регистр 15 по приходу синхроимпульса второго и хранится в нем до соответствующего момента (1.+1)-го шага. С регистра 15 через блок 16 коэффицн1259477 ент сглаживания умножается в блоке -7 на невязку с блока 6. Результат умножения поступает на первый вход сумма" тора 9, на втором входе которого уже находится значение сглаженного на (i-1)-ом .шаге сигнала. Кроме того, вновь полученная обратная величина коэффициента сглаживания подготавливает некоторые элементы устройства к (i+1)-му шагу фильтрации. С регис- 1О тра 15 обратная величина коэффициента сглаживания подается на вход умножителя 18 в блоке 17 увеличивается на единицу (обратная величина предварительного коэффициента сглажива- 15 ния (i+1)-го шага) и умножается в блоке 20 на код ошибки блока 28,- формируя скользящий порог аномальности (i+1)ro шага, подаваемый на вход блока 11 сравнения. Если идет первый шаг фильтрации, то содержимое счетчика 17 станет равным двум, блок 22 в этом случае вырабатывает сигнал, ! который на входе триггера 23 ждет третьего синхроимпульса. С приходом синхроимпульса третьего на i-ом шаге содержимое регистра 29 сдвигается влево, теряя результат сравнения (i-1)-го шага; в сумматоре 9 складываются значения, стоящие на входах, ЗО результат сглаживания i-ro шага находится на выходе устройства до соответствующего момента (i+1). — 1ro шага.

Кроме того, по синхроимпульсу третьему триггер 23 устанавливается в состояние, определяемое выходом блока 22. Далее начинается (i+1)-й шаг фильтрации с приходом синхроимпульса первого, и все повторяется. Триггер

23 устанавливается в единичное сос- 40 таяние только на первом шаге по тре". тьему синхроимпульсу. Тогда как на.

1втором шаге фильтрации с приходом синхроимпульса первого через блок

24 логическая "1" поступает на сдви- 4 гающий вход регистра 25, увеличивая

его содержимое в два раза. Начиная со второго шага в регистре 25 хранится величина самой дисперсии измерений и стоит на втором входе умножи- 50 теля 18.

Формула изобретения

Устройство для цифровой фильтрации, содержащее вычитатель, выход которого подключен к первому входу первого умножителя, выход которага подключен к первому входу сумматора, выход которого является информационным выходом устройства и подключен к первому входу вычитателя, второй вход которого подключен к выходу преобразователя последовательного кода в параллельный, информационный вход которого является информационным входом устройства, регистр ошибки, блок сравнения, блок элементов ИЛИ, первый и второй входы которого под" ключены к выходам соответственно первого и второго блоков элементов

И, q т л и ч а ю щ е е с я тем,:чта, с целью повышения точности фильтрации, в него введены квадратор, второй, третий и четвертый умножители; третий блок элементов И, три регистра, дешифратор, элемент ИЛИ, блок вычисления обратной величины, счетчик, блох сравнения с "2", триггер, элемент If, сдвигавый регистр и синхронизатор, причем выход вычитателя подключен к входу квадратора, выход которого подключен к первому входу второго умножителя, выход которого подключен к первому входу первого блока элементов И и первому входу блока сравнения, выход которого подключен к информационному входу первого регистра, выход которого подключен к входу дешифратора, первый и четвертый выходы котарого подключены соответственно к первому и второму входам элемента ИЛИ, выход которого подключен к первому входу третьего блока элементов И, выход которого подключен к третьему входу блока элементов ИЛИ, выход которого подключен к информационному входу второго регистра, выход которого подключен к первому входу третьего умножителя, счетному входу счетчика и входу блока вычисления обратной величины, выход которого подключен к второму входу первого умножителя, второй выход дешифратора подключен к второму входу первого блока элементов И и тактовому входу третьего регистра, выход которого подключен к первому входу второго блока элементов И, второй вход которого подключен к третьему выйоду дешифратора, информационный выход счетчика подключен к инфорл ационному входу третьего регистра, второму входу третьего блока элементов И, первому входу четвертого умножителя и входу блока сравнения с "2", выход

В 1259477 Ь которого подключен к 0-входу тригге- дам начальной установки преобразовара, выход которого подключен к пер- теля последовательного кода в паралвому входу элемента И, выход которо- лельный, сумматора, сдвигового Рего подключен к входу управления сдви- гистра, триггера, первого, второго гом сдвигового регистра, выход кото- и третьего РегистРов, второй выход рого подключен к второму входу тре- синхронизатора подключен к второму тьего умножителя, выход которого входу элемента И и входу синхронизаподключен к второму входу второго ции преобразователя последовательумпожителя, выход регистра ошибки ного кода в параллельный, третий подключен к второму входу четверто- 1Î выход синхронизатора подключен к такго умножителя, выход которого под- товому входу второго регистра, а четключен к второму входу блока сравне- вертый выход синхронизатора подклюния, выход сумматора подключен к к тактовым входам сумвторому входу сумматора, а первый вы- матора, первого регистра ход синхронизатора подключен к вхо- 15 триггера.

1259477

Суй

ФигЗ

Составитель А.Варанов

Редактор Л.Гратилло Техред A.Êðàâ÷óê; . Корректор С.Шекмар

Заказ 5138/57 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1!3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.у кгород, ул.Проектная, 4