Преобразователь кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники. Применение его в устройствах обмена информацией между измерительными устройствами и ЭВМ позволит уменьшить общее количество оборудования за счет расширения функциональных возможностей преобразователя - обеспечения обратного преобразования из двоичного кода в код Грея. Преобразователь содержит четыре регистра, две группы элементов И, группу сумматоров по модулю два, группу элементов задержки и формирователь импульсов. Благодаря введению триггера, двух элементов И, двух элементов ЗАПРЕТ и двух элементов ИЛИ при подаче соответствующего управляв кяцего сигнала осуществляется.коммутация элементов, позволяющая получить как прямое, так и обратное преобразование . 1 ил. с @ «Л W

СОЮЗ СОЕЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

Р1 СПУБЛИК 11 4 Н 03 М 7/16

ГОСУДАРСТВЕННЬ1Й КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTWI

ОПИСАНИЕ ИЗОБРЕТЕНИ, "" -.:„ "К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21 ) 3862320/24-24 (22) 25.02.85 (46) 23,09.86. Бюл. 9 35 (72) А. П. Копылов, В. Н. Коношенко, А. С. Корнеев и Л. А. Григорьев (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 788104, кл. G 06 F 5/02, 19?8.

Авторское свидетельство СССР

Ф 824783, кл. G 06 F 5/02, 1981.

Авторское свидетельство СССР

В 1205311, кл. Н 03 М 7/16, 13.12.84. (54) ПРЕОБРАЗОВАТЕЛЬ КОДОВ (57) Изобретение относится к области вычислительной техники. Применение его в устройствах обмена информацией между измерительными устройствами и

ЭВМ позволит уменьшить общее количество оборудования за счет расширения функциональных возможностей преобразователя — обеспечения обратного преобразования из двоичного кода в код Грея. Преобразователь содержит четыре регистра, две группы элементов

И, группу сумматоров по модулю два, группу элементов задержки и формирователь импульсов. Благодаря введению триггера, двух элементов И, двух элементов ЗАПРЕТ и двух элементов ИЛИ при подаче соответствующего управля ющего сигнала осуществляется.коммутация элементов, позволяющая получить как прямое, так и обратное преобразование. 1 нл.

1259494

Устройство работает следующим образом.

На управляющий вход 21 устройства подается сигнал установки режима: ло- 45 гический "0" соответствует преобразованию чисел, представленных в коде

Грея, в двоичный код, логическая "1" соответствует преобразованию чисел, представленных в двоичном коде, в 50 код Грея.

В режиме преобразования из кода

Грея в двоичный код поданный на управляющий вход 21 сигнал логического

"0" осуществляет следующую коммутацию: ss элементы И 11 и 12 закрыты, триггер

10 в состоянии "0", элементы ЗАПРЕТ

13 и 14 открыты.

Изобретение относится к вычисли. тельной технике и может быть использовано в автоматизированных измерительных системах, в частности в устройствах обмена информацией между 5 измерительными устройствами и ЭВМ.

Цель изобретения †. расширение функциональных возможностей путем реализации обратного преобразования из двоичного кода в код Грея.

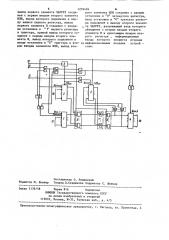

На чертеже представлена функциональная схема устройства.

Преобразователь кода Грея в двоичный код содержит регистры 1-4 с первого по четвертый, первую 5 и вторую б группы элементов И, группу 7 сумматоров по модулю два, группу 8 элементов задержки, формирователь 9 импульсов, триггер 10, первый 11 и первый 13 и второй 12 элементы И, второй 14 элемент. ЗАПРЕТ, первый 15 и второй 16 элементы ИЛИ. Информационные входы первого 1 и второго 2 регистров являются соответственно первыми 17 и вторыми 18 информационными входами устройства, вход формирователя 9 импульсов. является тактовым входом 19 устройства. Вход записи второго регистра 2, сдвигающий вход третьего. регистра 3, разрешающий 30 вход первого элемента ЗАНРЕТ 13 и первые входы первых элементов И 11 и

ИЛИ .15 объединены и подключены к входу 20 запуска устройства, запрещающие входы элементов ЗАПРЕТ 13 и 14 и вто- 35 рой вход первого элемента И 11 объединены и подключены к управляющему входу

21 устройства.. Выходы четвертого регистра 4 являются выходами 22 устройства. 40

Поступивший на вход 20 запуска сигнал "Начало преобразования" обнуляет регистры 3 и 4 и разрешает запись информации в регистры 1 и 2. В регистр 1 записывается К чисел в коде Грея, К = N/n, где N и и соответственно число разрядов регистра 1 и вводимого числа. В регистр 2 записывается N-разрядный двоичный код, содержащий "1" в разрядах 1-, (n+1)-, (2n+1)-,...,(К-l). n+1-а и "0" во всех остальных ра рядах.

На тактовый вход 19 поступают синхроимпульсы, каждый из которых обеспечивает формирование одного разряда, начиная со старшего, всех К выходных чисел. Для завершения преобразования требуется и синхроимпульсов. Синхроимпульсы поступают на формирователь

9, который формирует короткие импульсы: на первом выходе по переднему фронту входных импульсов, на втором— с задержкой 2/3 периода.

Преобразование кода Грея в двоичный производится поразрядно одновременно для всех К чисел. В первом такте с помощью регистра 2 и элементов

И первой группы 5 осуществляется выделение старших разрядов чисел из регистра 1 и их сравнение на сумматорах 7 по модулю два с соответствующими. разрядами регистра 3. Так как исходное состояние регистра 3 нулевое, то "1" на выходе каждого сумматора 7 по модулю два имеет место только при наличии 111 в старшем разряде соответствующего числа в ко; де Грея. Эти единицы записываются в соответствующие разряды регистра 4, принимающего информацию только единичными сигналами, а также через элементы 8 задержки на 1/3 периода синхроимпульсов записываются в регистр 3, После этого появляется импульс IIIIà втором выходе формирователя

9, который осуществляет сдвиг информации в регистрах 2 и 3. Этим обусловлено выделение в следующем такте следующего разряда исходных чисел, его сложение по модулю два с содержимым соответствующего разряда регистра 3, которое соответствует сумме по модулю цва предыдущих разрядов и запись результата в соответствующий разряд двоичных чисел в регистре 4.

В последующих тактах устройство работает аналогично, !

259 ,С приходом n-ro тактового импульса осуществляется преобразование младших разрядов всех К чисел, после чего цикл преобразования оказывается завершенным и выходная информация может быть считана из регистра 4.

В режиме преобразования из двоичного кода в код Грея на управляющий вход 21 подан сигнал логической "1", который закрывает элементы ЗАПРЕТ 13 10 и 14 и открывает элемент И Il. Поступивший на вход 20 запуска сигнал

"Начало преобразования" обнуляет регистры 3 и 4, осуществляет запись в регистр 2 К и-разрядных двоичных чи-. 5 сел, через элемент И 11 устанавливает регистр 1 в состояние "Все 1" и переводит триггер 10 в единичное состояние, в результате чего открывается элемент И !2. В момент поступления 20 первого тактового импульса, импульс с первого выхода формирователя 9 осуществляет через элементы И первой группы 5, сумматоры 7 по модулю два

6 и элементы 8 задержки перезапись 25 информации из регистра 2 в регистр 3 (так как регистр 1 имеет исходное значение "Все 1", а регистр 3 — "Все

0"). При этом информация оказывается также записанной в выходной регистр щ0

4. Импульс с второго выхода формирователя 9, задержанный .на 2/3 периода, осуществляет сдвиг информации в регистре 2 (при этом информация в регистре 3 не сдвигается, так как элементЗ ,ЗАПРЕТ закрыт). 9тот же импульс, пройдя через элемент И !2, обнуляет регистр 4 и производит запись.в регистр 1 двоичного числа, содержащего

"0" в 1-, (n+1)-.; (2n+I)-.. .,(K-1)» 40

1) и+ 1-м разрядах,а в остальныхразрядах — "l ". Задний фронт импульса сбрасывает в "0" триггер 10, который закрывает элемент И 12.

С .поступлением следующего, второ- 45 го тактового импульса производится сложение по модулю два исходных числа из регистра 3 со сдвинутыми числами из регистра 2. При этом младшие сдвинутые разряды обнуляются за счет 50 логического умножения с нулями в соответствующих разрядах регистра 1.

Таким образом, на выходе сумматоров

7 по модулю два в соответствии с алгоритмом преобразования чисел из двоичного кода в код Грея получены

К чисел в коде Грея, которые записываются в регистр 4 и могут быть счи494 4 таны в произвол ьный момент времени.

Обнуление регистра 4 импульсом -с второго выхода формирователя не производится, так как триггер 10 находится в нулевом состоянии и элемент

И 12 закрыт.

Формула изобретения

Преобразователь кодов, содержащий четыре регистра, две группы элементов

И, группу сумматоров по модулю два, группу элементов задержки и формирователь импульсов, вход которого является тактовым входом устройства, а первый выход соединен с первыми входами элементов И обеих групп, вторые входы элементов И первой группы подключены к соответствующим выходам первого регистра, информационные входы которого являются первыми информационными входами устройства, третьи входы элементов И первой группы соединены с соответствующими выходами второго регистра, вход записи которого объединен со сдвигающим входом третьего регистра и подключен к входу запуска устройства, сдвигающий вход второго регистра соединен . с вторым вьгходом формирователя импульсов, выходы элементов И первой группы соединены с первыми входами соответствующих сумматрров по модулю два, вторые входы которых подключены к соответствующим выходам третьего регистра, а выходы соединены с вторыми входами элементов И второй группй, выходы которых через соответствукщие элементы задержки подключены к соответствующим информационным входам третьего регистра и непосредственно— к соответствующим информационным входам четвертого регистра, выходы которого являются выходами устройства, отличающийся тем, что, с целью расширения функциональных возможностей путем реализации обратного преобразования из двоичного кода в код Грея, в него введены два элемента И, два элемента ЗАПРЕТ, два элемента ИЛИ и триггер, разрешающий вход первого элемента ЗАПРЕТ объединен с первыми входами первых элементов И и ИЛИ и подключен к входу запуска устройства, запрещающие входы элементов ЗАПРЕТ объединены с вторым входом первого элемента И и подключены к управляющему входу устройства, 5 1259494 d выход первого элемента ЗАПРЕТ соеди" рого элемента ИЛИ соединен с входом. неи с первым входом второго элемента установки в "0" четвертого регистра, KIH выход которого подключен к вхо- вход установки в "0" третьего регистду записи первого регистра, выход ра подключен к выходу второго элеменпервого элемента И соединен с входа- та ЗАПРЕТ, разрешающий вход которого ми установки в " 1 первого регистра объединен с вторым входом второго и триггера, прямой выход которого со- элемента И и сдвигающим входом втоединен с первым входом второго эле- рого регистра, информационные мента И, выход которого подключен к входы которого являются вторыми входу установки в "0" триггера и вто- 1о информационными входами устрой рым входам элементов ИЛИ, выход вто- ства.

Составитель О. Ревинский

Редактор М. Бланар Техред Л.Сердюкова Корректор С. Шекмар

Заказ 5139/58 Тираж 816 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4