Устройство частотного компандирования

Иллюстрации

Показать всеРеферат

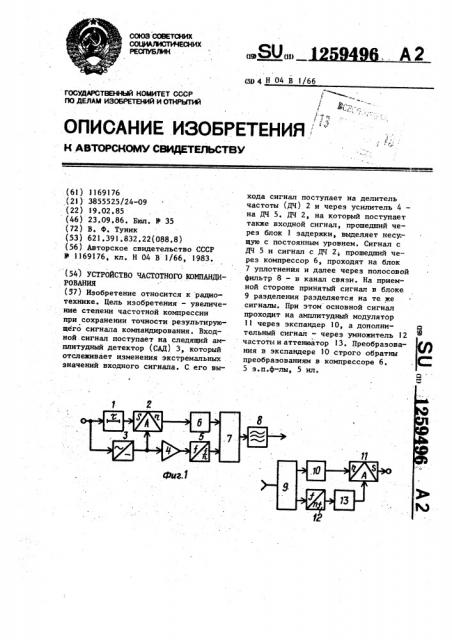

Изобретение относится к радиотехнике . Цель изобретения - увеличение степени частотной компрессии при сохранении точности результирующего сигнала компандирования Входной сигнал поступает на следящий амплитудный детектор (САД) 3, который отслеживает изменения экстремальных значений входного сигнала. С его выхода сигнал поступает на делитель частоты (ДЧ) 2 и через усилитель 4 - на ДЧ 5. ДЧ 2, на который поступает также входной сигндл, прошедший через блок 1 задержки, вьщеляет несу,- щую с постоянным уровнем. Сигнал с ДЧ 5 и сигнал с ДЧ 2 прошедший через компрессор 6, проходят на блок 7 уплотнения и далее через полосовой фильтр 8 - в канал связи. На приемной стороне принятый сигнал в блоке 9 разделения разделяется на те же сигналы. При этом основной сигнал проходит на амплитудный модулятор 11 через экспандер 10, а дополнительный сигнал - через з множитель 12 частоты и аттенюатор 13. Преобразования в экспандере 10 строго обратны преобразованиям в компрессоре 6. 5 з.п.ф-лы, 5 ил. I л ;; Фиг.1 х to

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН ае а»

А2

@р 4 Н 04 В !!66

ОПИСАНИЕ ИЗОБРЕТЕНИЯ "

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ"!

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) 1169176 (2!) 3855525/24-09 (22) 19.02.85 (46) 23.09.86. Бюл. У 35 (72) В. Ф. Туник (53) 621.391.832.22(088.8) (56) Авторское свидетельство СССР

У 1169!76, кл. Н 04 В 1/66, 1983. (54) УСТРОЙСТВО ЧАСТОТНОГО ЮМПАНДИРОВАНИЯ (97) Изобретение относится к радиотехнике. Цель изобретения — увеличение степени частотной компрессии при сохранении точности результирующего сигнала компандирования. Входной.сигнап поступает на следящий амплитудный детектор (САД) 3, который отслеживает изменения экстремальных значений входного сигнала. С. его выхода сигнал поступает на делитель частоты (ДЧ) 2 и через усилитель 4— на ДЧ 5. ДЧ 2, на который поступает также входной сигнал, прошедший через блок 1 задержки, выделяет несущую с постоянным уровнем. Сигнал с

ДЧ 5 и сигнал с ДЧ 2, прошедший через компрессор 6, проходят на блок

7 уплотнения и далее через полосовой фильтр 8 — в канал связи. На приемной стороне принятый сигнал в блоке

9 разделения разделяется на те же сигналы. Нри этом основной сигнал проходит на амплитудный модулятор

1! через зкспандер 10 а дополнительный сигнал — через умножитель 12 частоты и аттенюатор 13. Преобразования в экспандере 10 строго обратны преобразованиям в компрессоре 6.

5 з.п.ф-лы, 5 ил.

1259496

Изобретение относится к радиотехнике и связи, может быть использовано в узкополосных системах связи и является усовершенствованием изобретения по авт. св. 9 !169176.

Цель изобретения — увеличение степени частотной компрессии при сохранении точности результирующего сигнала компандирования.

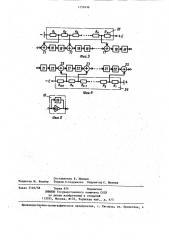

На фиг. 1 представлена структурная электрическая схема устройства частотного компандирования, на фиг. 2— структурная электрическая схема следящего амплитудного детектора; на фиг. 3 - структурная электрическая схема делителя частоты; на фиг. 4структурная электрическая схема умножителя частоты1 на фиг. 5 — структурная электрическая схема блока обратйого нелинейного преобразования.

Устройство частотного компандирования содержит блок 1 задержки, делитель 2 частоты, следящий амплитудt ный детектор 3, дополнительный усилитель 4, дополнительный делитель 5 частоты, компрессор 6 с первым делителем частоты на входе, блок 7 уплотнения, полосовой фильтр 8, блок 9 разделения, экспандер 10 с первым умножителем частоФы на выходе амплиУ тудный модулятор 11, дополнительный умножитель 12 частоты, дополнительный аттенюатор 13, Следящий амплитудный детектор содержит пиковый детектор

l4, ключ 15, блок 16 выделения максимума сигнала. Делитель 2 частоты

:содержит К сумматоров 17, К блоков

18 обратного нелинейного преобразования, К инверторов 19, делитель 20 напряжения. Умножитель частоты содержит К формирователей 21 модуля сигнала, К блоков 22 прямого нелинейного преобразования, К сумматоров 23 и делитель 24 напряжения. Блок 18 обратного нелинейного преобразования содержит операционный усилитель 25 и блок 26 прямого нелинейного преобразования. Блоки прямого нелинейного преобразования состоят из квадраторов (не показаны).

Устройство частотного компандиро.вания работает следующим образом.

Входной сигнал поступает на делитель 2 через блок 1, который компенсирует задержку сигнала, поступающего на вход делителя 2 через следящий . амплитудный детектор 3.

10 !

Выходное напряжение амплитудного детектора 3 отслеживает изменения экстремальных значений входного сигнала, выделяемых пиковым детектором

14. При этом блок 16 выделяет экстремумы входного сигнала и вырабатывает короткий импульс, замыкающий ключ 15 на время действия импульса, в результате чего выходное напряжение делителя 2 уменьшается до нуля.

После прекращения действия импульса ключ 15 размыкается, и происходит за" поминание и хранение значения нового экстремума. Так выделяется огибающая, которая действует на дополнительный делитель 5 через дополнительный усилитель 4, превращающий ее в сигнал с сокращенным спектром.

На выходе делителя 2 при этом получается несущая с постоянным уровнем, ввиду чего в первом делителе частоты компрессора 6 уровни смещения исходного сигнала для каждого инвертора

19 образуются просто при помощи ис-. точника постоянного напряжения дели- теля 20 и сумматора .17, а при помощи блока 18 достигается дополнительное сокращение спектра в первом канале, что позволяет значительно уменьшить число других каналов преобразования, в которых производится сокращений ши1t tl рины хвоста этого спектра. Получен.ные таким образом сигналы всех каналов вместе с дополнительным сигналом на выходе блока 7 формируются в единый компрессированный сигнал, передаваемый через полосовой фильтр 8 в канал связи.

В блоке 9 принятый сигнал разделяется на те же сигналы каналов комппрессора 6 и дополнительный сигнал.

Преобразования. в экспандере 10 строго обратны преобразованиям в компрессоре 6, в частности обязательна обратщмость нелинейных преобразований в блоках 18 и 22, обеспечиваемая использованием в блоке 18 блока 26 в цепи обратной связи операционного усилителя 25.

Аналогично дополнительный умножитель 12 посредством. цепей из формирователей 21, блоков 22, сумматоров. 23 и делителя выполняет операции, обратные тем, которые производит дополниl тельный делитель 5, При этом резисторы делителей 20 и 24 выполнены на резисторах одного номинала. На выходе дополнительного умножителя 12 восста1259496 навливается огибающая сигнала, а на выходе экспандера 10 — несущая, которая на выходе амплитудного модулятора

11 восстанавливается в исходный сигнал. 5

Формула изобретения

1. Устройство частотного компандирования по авт. св. У 1169176, о т- 10 л и ч а ю щ е е с я - тем, что, с целью увеличения степени частотной компрессии при сохранении точности результирующего сигнала компандирования, в компрессор введены последо- 5 вательно соединенные блок задержки и делитель частоты, а такыре последовательна соединенные следящий амплитудный детектор, дополнительный усилитель и дополнительный делитель час- 20 тоты, выход которого соединен с дополнительным входом блока . уплотнения при этом вход блока задержки объединен с входом следящего амплитудного детектора, выход которого соединен с входом "делителя делителя частоты, выход которого соединен с входом первого делителя частоты, а в экспандер . введены последовательно соединенные дополнительный умножитель, дополни- 3Q тельный аттенюатор и амплитудный мо1 дулятор, второй вход которого соединен с выходом первого умножителя частоты, при этом вход дополнительного умножителя частоты соединен с дополнительным выходом блока разделения.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я. тем, что следящий амплитудный детектор содержит последовательно соединенные пиковый детектор и ключ, второй вход которого через блок выделения максимума сигнапа соединен с входом пикового детектора, вход которого является входом следящего амплитудного детектора, выходом которого является выход ключа.

3. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что делитель частоты содержит К последовательно соединенных цепей, каждая иэ которых состоит из последовательно соединенных сумматора, блока обратного нелинейного преобразования и инвертора, а также делитель напряжения, подключенный к источнику напряжения, причем

К выходов делителя напряжения соединены с вторыми входами сумматоров соответствующих К цепей, причем первый вход сумматора первой цепи является входом делит ля частоты, выходом ко- торого является выход инвертора К-й цепи.

4. Устройство по п. 1, о т.л ич а ю щ е е с я тем, что умножитель частоты содержит К последователь но соединенных цепей, каждая иэ которых состоит из последовательно соединенных формирователя модуля сигнала, блока прямого нелинейного преобразования и сумматора, а также делитель напряжения, подключенный к источнику напряжения, К выходов которого подключены к вторым входам сумматоров соответствующих К цепей, причем вход. формирователя модуля сигнала первой цепи является входом умножителя частоты, выходом которого является выход сумматора К-й цепи.

5. Устройство по п. 4, о т л и ч а ю щ е е с я тем, что блок прямого нелинейного преобразования состоит иэ М последовательно соединенных квадраторов.

6. Устройство по пч. 3 и 5, о т— л и ч а ю щ е е с я тем, что блок обратного нелинейного преобразования состоит из операционного усилителя, в обратную связь которого включен блок прямого нелинейного преобразования.

1259496

Фиа3! R>»g I4 R» ( 3

Составитель В. Шевцов

Редактор M. Бланар Техред Л>Сердюкова . Корректор С. Шекмар

Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по.делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5140/58

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4