Регенератор цифровых сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике электросвязи. Обеспечивается возможиость выделения цйфров сс каналов со статистическим уплотнением. Устр-во содержит корректирующий усилитель 1, два пороговых блока 2 и 3, блок выделения хронирующего сигнала 4, приемник синхросигнала 5 и злемент ИЛИ 6. Дли достижения цели в устр-во введены блок разделения сигналов 7, дешифратор 8 номера канала, канальные ключи 9, блоки 10 приоритета, сумматор 11, блок сравнения 12, блок 13формирования номера канала, блок 14объединения сигналов, блок 15 переключений , три блока задержки 16, 17 и 18, блок 19 замены информации, коммутатор 20, элемент ШШ 21, блок управления 22 и формирователь 23 линейного сигнала, с помощью которых из входного квазитроичного сигнала в коде с переменным чередованием йолярности токовых посылок вьщеляются цифровые каналы со статистическим уплотнением. 1 ил. (Л С

ССЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (gg 4 Н 04 Х 3/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ с с

41

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР .

Г10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3801529/24-09 (22) 10.10.84 (46) 23.09.86. Бюл. У 35 (72) В. А. Клишин, А. А. Лелис, И. В.. Морозов и А, В. Соболев (53) 621 ° 395.724.002(088.8j (56) Авторское свидетельство СССР

В 758541, кл. H 04 7 3/08, 1978. (54) PEFEHEPATOP ЦИФРОВЫХ СИГНАЛОВ (57) Изобретение относится к технике электросвязи. Обеспечивается aosMoxаоста выделения цифровых каналов со статистическим уплотнением. Устр-во содержит корректирующий усилитель 1, два пороговых блока 2 и 3, блок выделения хронирующего сигнала 4, приемник синхросигнала 5 и элемент

ÄÄSUÄÄ A1

ИЛИ 6. Для достижения цели в устр-во введены блок разделения сигналов 7, дешифратор 8 номера канала, канальные ключи 9, блоки 10 приоритета, сумматор 11, блок сравнения 12, блок

13 формирования номера канала, блок

14 объединения сигналов, блок 15 пе" реключений, три блока задержки 16, 17 и 18, блок 19 замены информации, коммутатор 20, элемент И1Н4 21, блок управления 22 и формирователь 23 линейного сигнала, с помощью которых из входного квазитроичного сигнала в коде с переменным чередованием полярности токовых посыпок выделяются цифровые каналы со статистическим уплотнением. 1 ил, 1 12595

02

2 входы канальных ключей 9, а с второго — информацию о его номере на дешйфратор 8 номера канала.

На вторые входы канальных ключей

9 поступает управляющая команда с дешифратора 8 номера канала, которая разрешает прохождение информационных символов на один из блоков 10 приоритета, если данный канал не выделяется, и дает команду на вывод информации с канального ключа, если передаваемый по линии канал выделяется (присвоим выделяемому каналу номер )

Сумматор 11 объединяет сигналы, поступающие с блоков 10 приоритетов каналов (исключая i канал), и выдает на первый вход блока 12 сравнения, на второй вход которого поступает информация через соответствующий блок

10 приоритета о состоянии i-ro кана. ла. Информация о состоянии i-го канала поступает также на блок 14 объединения сигналов, где происходит объединение информации о состоянии канала и о его номере, сформированном в блоке 13 формирования номера канала. Блок 12 сравнения определяет (с учетом приоритета) какой из каналов наиболее активен: вводимый нли передаваемый по линии связи, и дает команду на блок 15 переключений1 на прохождение информации о состоянии наиболее активного канала. Информация о состоянии наиболее. активного канала поступает на третий вход блока 19 замены информации.

20

ЗО

55

Изобретение относится к технике электросвязи и может использоваться в цифровых системах связи для осуществления процесса регенерации.

Цель изобретения — обеспечение возможности выделения цифровых каналов со статистическим уплотнением.

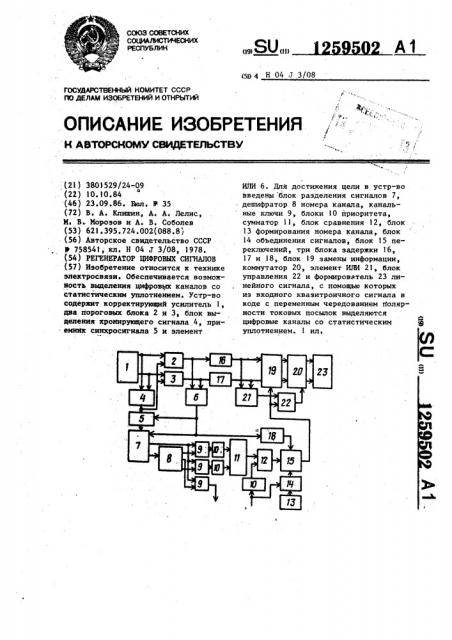

На чертеже представлена структурная электрическая схема предлагаемого генератора.

Генератор цифровых сигналов содержит корректирующий усилитель 1, первый 2 и второй 3 пороговые блоки: блок 4 выделения хронирующего сигнала, приемник 5 синхросигнала, первый элемент ИЛИ 6, блок 7 разделения сигналов, дешифратор 8 номера канала, канальные ключи 9, блоки !О приоритета, сумматор ll блок 12 сравнения, блок 13 формирования номера канала, блок 14 объединения сигналов, блок

15 переключений, первый 16, второй

17 и третий 18 блоки задержки, блок

19 замены информации, коммутатор 20, второй элемент ИЛИ 21, блок 22 управления, формирователь 23 линейного сигнала.

Регенератор цифровых сигналов работает .следующим образом.

На вход регенератора поступает квазитроичный сигнал в коде с переменным чередованием полярности токовых посылок (код ANl) из линии прямого направления. Этот сигнал соответствует сигналу, формируемому в каналообразующем оборудовании цифровых систем передачи путем объединения адреса наиболее активного канала и информации о его состоянии с последующим преобразованием в квазитроичный сигнал. С первого выхода корректирующего усилителя 1 поступают сигналы положительной полярности, а с второго — отрицательной. Отрегенерированные первым 2 и вторым 3 пороговыми блоками сигналы обьединеняются первым элементом ИЛИ 6 и образуют исходный двоичный сигнал, который поступает на приемник 5 синхросигнала, блок 7 разделения сигналов и через третий блок

18 задержки на блок 15 переключений.

Приемник 5 синхросигнала определяет место информационных символов о со-. стоянии каналов и адреса каналов в поступающей двоичной последовательности, а блок 7 разделения разделяет их и передает с первого выхода информацию о состоянии канала на первые

На первый и второй входы блока

19 замены информации через первый )6 и второй 17 блоки задержки поступают сигналы о регенерируемых посылках положительной и отрицательной полярности. Ь блоке 19 замены информации производится замена информации в линии прямого направления на сигнал, поступающий с блока 15 переключений.

Если сигнал после блока 19 замены информации превращают непосредственно в квазитроичный, т.е. присваивают положительную полярность токовым посылкам первого выхода блока 19 замены информации, а отрицательную полярность — токовым посылкам второго вы» хода, то в регулирующем кваэитроичном сигнале имеет место нарушение закона преобразования в виде двух последовательных посылок одной полярности. Передача такого сигнала недопустима, и з обретения

Формула с

Составитель А. Москевич

Редактор M. Бланар ТехредЛ.Сердюкова Корректор А. Знмокосов

Тираж 624 . Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Заказ 5140/58

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4, 3 1259

Чтобы избежать этого в регенера-! гор введены коммутатор 20, блок

22 управления и второй элемент

ИЛИ 21, Блок .22 управления переводится из одного состояния в другое, если символ вводимого сигнала (поступающий с блока 15 переключений) и сигнала подлежащего замене (поступающий с второго элемента ИЛИ 21) на вводимый ие совпадает. В коммутаторе 10

20 производится трансляция сигналов е первого входа на первый выход и с второго входа на второй выход в случае отсутствия команды с блока 22 управления и происходит трансляция 15 первого входа на второй выход и второго входа на первый выход в случае поступления такой команды. За счет этого достигается сохранение закона преобразования и сигнал с выхода 20 формирователя 23 линейного сигнала поступает к потребителю информации.

Регенератор цифровых сигналов, содержащий корректирующий усилитель, выходы которого подключены к входам блока выделения хронирукищего сигнала, выход которого соединен с первым 30 входом приемника синхросигнала, и к первым входам пороговых блоков, вто-. рые входы и выходы которых соединены соответственно с выходом блока вццеления хронирующего сигнала и с входами первого элемента ИЛИ, выход которого подключен к второму входу приемника синхросигнала, а также блок замены информации, выходы которого подключены к информационным вхо- 40 дам коммутатора, управляющий вход и выходы которого соединены соответст. венно с выходом блока управления и с входами формирователя линейного сиг502 4 нала, о т л и ч а ю щ н и с я тем„ что, с целью обеспечения возмоЖности выделения цифровых каналов со статистическим уплотнением, в него введены три блока задержки, канальные ключи, блок разделения сигналов, блок сравнения, второй элемент ИЛИ, блоки приоритета, дешифратор номера канала, сумматор и последовательно .соединенные блок формирования номера канала, блок объединения сигналов и блок переключений, выход которого подключен к первому входу блока управления, второй вход которого соединен с выходом второго элемента

ИЛИ, и к управляющему входу блока замены информации, сигнальные входы которого соединены с входами второго элемента ИЛИ и с выходами первого и второго блоков задержки, входы которых соединены с входами первого элемента ИЛИ, выход которого подключен к входу третьего блока задержки, выход которого соединен с вторым входом блока переключений, и к первому входу блока разделения сигналов, второй вход и первый выход которого соединены соответственно с выходом приемника синхросигнала и с входом дешифратора номера канала, выходы которого подключены к первым входам канальных ключей, вторые входы которых соединены с вторым выходом блока разделения сигналов, при этом выходы соответствующих канальных ключей через одни блоки приоритета подключены к входам сумматора, выход которого соединен с первым входом блока сравнения, второй вход и выход которого соединены соответственно с выходом другого блока приоритета, вход которого подключен к второму входу блока объединения сигналов, и с третьим входом блока переключений.