Программно-управляющее линейное устройство автоматических телефонных станций

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - увеличение скорости управления. Устройство coдepжит N линейных адаптеров (ЛА) 1 ,...,1 , оперативно-запоминающий блок (ОЯБ) 2, г-р 3 тактовых импульсов, формирователь 4 кода адресов , дешифратор 5 адресов. Вновь введена программируемая логическая матрица ПЛМ 6. Алгоритм работы устройства записан в ШШ 6. Устойчивое состояние алгоритма и соответственно ПЛМ 6 и ОЗБ 2 сохраняется до появления ожидаемого изменения на выходах ЛА I ,..., 1 . Каждой ячейке ОЗБ 2 соответствует свой ЛА 1; . Адрес инициирования ячейки и ЛА 1- появляется на выходе формирователя 4 и дешифратора 5 одновременно для ОЗБ 2 и ЛА 1j. ПЛМ 6 отслеживает запрограммированный алгоритм. Соответствующие команды с ПЛМ 6 поступают на соответствукидие входы ЛА}4И тактовыми § импульсами записи записываются в них. В соответствии с зтой управляющей информацией телефонные каналы обслуживаются в соответствии с алгоритмом установления соединения, и независимо друг от друга ПЛМ 6 может обслуживать свыше 256 ЛА. I ил. 1 IgP Oi т I

СОЮЗ СОВЕТСНИХ

COLLHAËÈÑTÈ×ÅCHÈХ

РЕСПУБЛИК

„„SU„„1259512 (51) 4 H 04 М 3/02

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ у t»,,:у»

ОПИСАНИЕ ИЗОБРЕТЕНИЙ =

Н АBTOPCMOMY СВИДЕТЕЛЬСТВУ (2)) 3837779/24-09 (22) 07.01,85 (46) 23,09.86. Бюл. ))р 35 (72) В.ГеДедоборщ, M.À.Æàðêîí и В.О.Сергеев (53) 621.395.345(088,8) (56) Скляров В.А..Синтез автоматов на матричных БИС. — Минск, : Наука и техника, 1984, с. 24, рис. 2.1.

Эскизно-технический проект АМТС типа Кварц. — М.: ЦНИИС, 1976, 1-У))2. (54) )ТРОГРА) МНО-УТ)РАВЛЯ)ОЩЕЕ ЛИНЕЙНО) . УГТРОЙСТВО АВТОМАТИЧЕСКИХ ТЕЛЕФОНН))Х СТАНЦИЙ (57) Изобретение относится к электросвязи. Цель изобретения — увеличение скорости управления. Устройство содержит М линейных адаптеров

1 N (ЛА) 1,...,1, оперативно-запоминающий блок (ОЗБ) 2, r-p 3 тактовых импульсов, формирователь 4 кода адресов, дешифратор 5 адресов. Вновь введена программируемая логическая матрица ПЛМ 6. Алгоритм работы устройства записан в KIN 6 ° Устойчивое состояние алгоритма и соответственно

)I IM 6 и ОЗБ ? сохраняется до появления ожидаемого изменения на выходах й»

ЛА 1,...,1 . Каждой ячейке ОЗБ 2 . соответствует свой ЛА 1; . Адрес инициирования ячейки и ЛА 1; появляется на выходе формирователя 4 и дешифратора 5 одновременно для ОЗБ 2 и

ЛА 1, ПЛМ 6 отслеживает запрограммированный алгоритм. Соответствующие команды с ПЛМ б поступают на соответствующие входы ЛА 1,и тактовыми ф импульсами записи записываются в них., В соответствии с этой управляющей информацией талано«мне «аналм обелу- аеме

0 живаются в соответствии с алгоритмом установления соединения, и неэа- а висимо друг от друга ПЛМ 6 может обслуживать свыше 256 ЛА. 1 ил.

° иВ

1259512 2 импульсов, поступающих по тактовому входу, осуществляют отслеживание запрограммированного В программируемой логической матрице 6 алгоритма. Со5 ответствующие команды с выхода программируемой логической матрицы 6 поступают на соответствующие входы линейного адаптера 1,, и тактовыми импульсами записи записываются в

1О них.

В соответствии с этой управляющей информацией, поступающей на входы линейного адаптера 1., и снимаемой с выходов линейного адаптера 1;, телефонные каналы обслуживаются в соответствии с алгоритмом установления соединения и независимо один от дру" гого,. Таким образом, обеспечивается взаимодействие с центральной управ2б ляющей частью автоматической телефонной станции.

ЗОФормула изобретения

Изобретение относится к электросвязи, а именно к телефонным коммутационным системам, Цель изобретения — увеличение скорости управления.

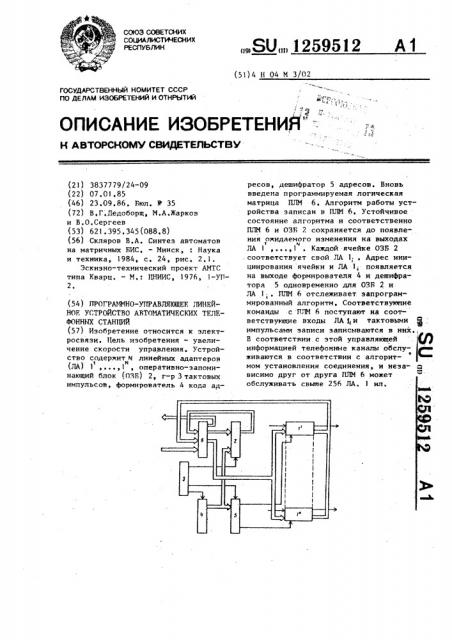

На чертеже представлена структурная электрическая схема программноуправляющего линейного устройства автоматических телефонных станций.

Устройство содержит И линейных

1 адаптеров 1,...,1", оперативно-saпоминающий блок 2, генератор 3 тактовых импульсов, формирователь 4 кода адресов, дешифратор 5 адресов и программируемую логическую матрицу 6, Устройство работает следующим образом.

Тактовые импульсы генератора 3 тактовых импульсов разбиты íà N последовательно расположенных групп, где И - число линейных адаптеров

1 . ..1 . Каждая группа образует конечйое число импульсов, предназначенных для обеспечения микроцикла перехода между двумя устойчивыми состояниями автомата, построенного .иа программируемой логической матрице 6..Каждому микроциклу соответствует свой адрес, являющийся также адресом соответствукицих ячеек оперативно-запоминающего блока 2 и соотг ветствующих линейных адаптеров 1

О б б у 1 4

Алгоритмы работы программа предлагаемого устройства записана в программируемой логической матрице

6. Устойчивое состояние алгоритма и, соответственно, программируемой логической матрицы 6, и оперативно-запоминающего блока 2 сохраняется до появления ожидаемого изменения на выходах линейных адаптеров 1 ...,,1 поступающего на соответствующие входи программируемой логической матрицы 6. Поскольку каждой ячейке оперативно-запоминающего блока 2 соответствует свой линейный адаптер tl,, то адрес инициирования ячейки и соответствующего линейного адаптера

1; ноявляетсй на выходе формирователя 4 кода адресов и дешифратора

5 адресов одновременно для. оперативно"запоминающего блока 2 и этого желинейного адаптера 1;, а программируемая логическая матрица 6, являющаяся просто перекодировщиком входного кода в выходной, совместно с оперативно-запоминающим блоком 2 под действием соответствующих тактовых

Быстродействие интегральных схем с учетом точности обработки сигналов, 25 соответствующей 1 мс, позволяет обслуживать программируемой логической матрицей 6 свыше 256 линейных адаптеров.

Программно-управляющее линейное устройство автоматических телефонных станций, содержащее Н линейных адаптеров, оперативно-запоминающий блок, 35 генератор тактовых импульсов, формирователь кода адресов и дешифратор адресов, причем к входам н выходам

Й линейных адаптеров подключены соответственно разговорные тракты приема и передачи телефонных линий, о тл н ч а ю щ е е с я тем, что, с целью увеличения скорости управления, в него введена программируемая ло45 гическая матрицаt причем первый вто рой и третий выходы генератора тактовых импульсов соединены с тактовыми входами оперативно-запоминающего блока, формирователя кода и дешифратора адресов, выходы формирователя кода адресов соединены с адресными входами оперативно-запоминающего блока и входами дешифратора адресов, N выходов которого соединены с тактовыми входами соответствующих N ли55 нейных адаптеров, у|травляющие входы которых подключены к первым информационным выходам программируемой логической матрицы, вторые информацион3 1259512 4 нме выходы программируемой логичес- цнонные выходы линейных адаПтеров кой матрицы соединены с информацион- обьединены и подключены к вторым вхо" иьачи входами оперативно-запоминающе- дам программируемой логической матриго блока, информационные выходы Ко цы, третьи информационные входы и, торого соединены с первыми информа- g третьи информационные выходы которой ционными входами программируемой ло- являются управляющими входами и выхогической матрицы, при этом информа- . дами устройства.

Составитель В,Пушкин

Редактор N.Бланар ехред И.Попович . Корректор C.черни

Заказ 5141/59 Тирах 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Узгород, ул. Проектная, 4