Устройство для вихретокового контроля

Иллюстрации

Показать всеРеферат

Изобретение относится к средствам неразрушающего контроля материалов и изделий и.может быть использовано для дефектоскопии и дефектометрии металлов в любой отрасли промышленности . Цель изобретения - повышение точности контроля за счет отстройки от влияния несовершенства изготовления катушек матричного преобразователя и влияния на результаты электрофизических параметров изделия. Устройство содержит последовательно соединенные генератор 1 , вихретоковый матричный преобразователь 2, коммутатор 3, ключ 4, ус шитель 5, детектор 6, АЦП 7, блок 19 памяти и видеоконтрольный блок 20, последовательно соединенные перемножитель 8, линию 9 задержки, дифференциальный усилитель 10, связанный в свою очередь с ключом 4. В состав устройства входят также подключенные к генератору 1 последовательно соединенные фазометр 11, АЦП 12, первый блок 18 памяти, связанный первым выходом через ЦАП 14 с линией 9, а вторым - через ЦАП 13 с перемножителем . Режим работы устройства, режим компенсации преобразователей матрицы и режим измерения устанавливают при помощи переключателя 17 режимов. Устройство позволяет автоматически скомпенсировать каждый преобразователь матрицы в отдельности и анализировать сигнал только от дефекта. 2 ил. i (Л

СОЮЗ СОВЕТСНИХ

COUHAЛИСТИЧЕСНИХ

РЕСПУБЛИН д в 4 С 01 N 27/90

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ ЮЯыи@уйюывв р

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3883824/25-28 (22) 15.04. 85 (46) 30. 09. 86. Бюл. К - 36 (71) Научно-исследовательский институт интроскопии (72) С.Ю.Иванов, В.А.Коровяков и Ю.К.Федосенко (53) 620.179.14(088.8) (56) Авторское свидетельство СССР

Ф 862060, кл. G 0 1 N 27/90, 1979. (54) УСТРОЙСТВО ДЛЯ ВИХРЕТОКОВОГО

КОНТРОЛЯ (57) Изобретение относится к средствам неразрушающего контроля материалов и изделий и может быть использовано для дефектоскопии и дефектометрии металлов в любой отрасли промышленности. Цель изобретения — повышение точности контроля за счет отстройки от влияния несовершенства изготовления катушек матричного преобразователя и влияния на результаты электвофизических параметров изделия.

„„SU„, 1260834 A1

Устройство содержит последовательно соединенные генератор 1, вихретоковый матричный преобразователь 2, коммутатор 3, ключ 4, усилитель 5, детектор 6, АЦП 7, блок 19 памяти и видеоконтрольный блок 20, последовательно соединенные перемножитель 8, линию 9 задержки, дифференциальный усилитель 10, связанный в свою очередь с ключом 4. В состав устройства входят также подключенные к генератору 1 последовательно соединенные фазометр 11, АЦП 12, первый блок 18 памяти, связанный первым выходом через ЦАП 14 с линией 9, а вторым — через ЦАП 13 с перемножителем. Режим работы устройства, режим компенсации преобразователей матрицы и режим измерения устанавливают при помощи переключателя 17 режимов.

Устройство позволяет автоматически скомпенсировать каждый преобразователь матрицы в отдельности и анализировать сигнал только от дефекта. 2 ил.

12

Изобретение QTHocHT(:ÿ к средствам неразрушающего контроля материалов и изделий и может быть использовано для дефектоскапии и дефектометрии металлов в любой отрасли промышлен60834 2

I1AII !3, вторым (информационным) выхоB7 opoI о ЦАП 14, второй блок 19 памяти, подключенный вторым (адресным) входом к выходу счетчика 16 импульсов, третьим (управляющим) входом — к переключателю 17 режимов, первым (информационным) входом — к выходу второго АЦП 7, видеоконтрольный блок (ВКБ) 20, подключенный к выходу второго блока 19 памяти.

Матричный преобразователь (фиг.2) выполнен в виде матрицы пхп преобразователей трансформаторного типа.

Возбуждающая и измерительная обмотки каждого иэ и преобразователей расположены на ферритовом стержне.

Возбуждающие обмотки преобразователей включены последовательно, концы измерительных обмоток объединены в строки и столбцы.

Устройство работает в двух режимах: режиме компенсации и режиме измерения.

В режиме компенсации матричный преобразователь 2 устанавливают на бездефектный участок контролируемого иэделия. Переключатель 17 режимов

I0

l5

25 переводят в состояние, соответствующее режиму компенсации, при этом переключатель 17 режимов формирует сигнал, под управлением которого ключ 4 замыкает первый вход с первым выходом, счетчик 16 обнуляется, первый блок 18 памяти работает в режиме записи информации с первого и второго АЦП ? и 12. Под управлением счетчика 16 импульсов, на вход которого подается тактовая частота с генера30

40 тора l5 импульсов, коммутатор 3 подключает строку матричного преобразователя 2 к первому входу ключа 4, а столбец — к общей шине матрицы, тем самым происходит выбор преобра45 зователя. С первого выхода ключа 4 напряжение с преобразователя матрицы 2 подается на усилитель 5, амплитудный детектор 6 и второй АЦП 7, где происходит преобразование ана—

50 логового сигнала в цифровой вид.

В ячейке памяти блока 18 памяти происходит запоминание цифрового кода амплитуды сигнала, поступающего с АЦП 7, адрес которой выбирается

55 счетчиком 16 импульсов.

Одновременно напряжение с генератора 1 подается на первый вход фа- . зометра 11, йа второй вход которого ности.

Цель изобретения — повышение точности контроля за счет атстройки от влияния несовершенства изготовления катушек преобразователя и от влияния на результат электрофизических параметров изделия.

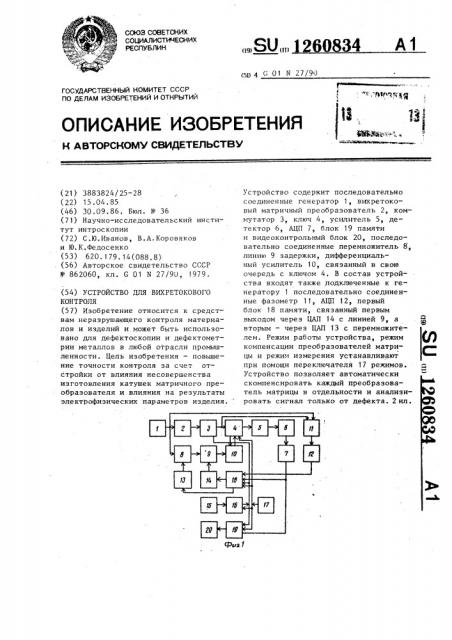

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 — конструкция матричного преобразователя.

Устройство содержит последователь но соединенные генератор 1 синусаидального тока, вихретоковый матрич ный преобразователь 2, коммутатор 3, ключ 4, усилитель 5, амплитудный детектор 6, второй аналогоцифровой преобразователь (АЦП) 7, последовательно соединенные перемножитель 8, вторым входом соединенный с генератором 1, линию 9 задержки, управляемую напряжением, дифференциальный усилитель 10, подключенный выходом к второму входу ключа 4, а вторым входом — к второму выходу ключа 4, последовательно соединенные фазаметр 11, подключенный первым входом к выходу генератора 1, а вторым входом — к первому выходу коммутатора 3, первый АЦП 12, а также первый цифроаналоговый преобразователь (ЦАП) 13, подключенный выходом к второму входу перемножителя 8, второй ЦАП 14, подключенный выходом к второму управляющему входу линии 9 задержки, последовательно соединенные генератор 15 импульсов и счетчик 16 импульсов, подключенный выходом к второму (управляющему) входу коммутатора, переключатель 17 режимов, подключенный к третьему (управляющему) входу ключа 4 и второму (управляющему) входу счетчика 16 импульсов, первый блок 18 памяти, подключенный первым (йнформационным) входом к выходу первого аналого-цифрового преобразователя l2, вторым (информационным) входом — к выходу второго АЦП ?, третьим (адресным) входом — к выходу счетчика 16 импульсов, четвертым (управляющим) входом — к переключателю 17 режимов, первым (информационным) выходом — к входу первого

1260834

3 подается напряжение с преобразователя матрицы матричного преобразователя 2, на выходе фазометра 11 получаем напряжение, пропорциональное сдвигу фаз между опорным напряжением (напряжение генератора 1) и напряжением с преобразователя матрицы.

АЦП 12 приводит аналоговое напряжение с выхода фазометра 11 в цифровой вид, которое запоминается в ячейке памяти блока 18 памяти. После этого, при поступлении на вход счетчика 16 следующего тактового импульса с тактового генератора 15 коммутатор 3 выбирает другой преобразователь мат- <5 рицы, а напряжения в цифровом виде, пропорциональные амплитуде и фазе сигнала с этого преобразователя, выше описанным способом запоминаются в следующей ячейке памяти блока 18 2О памяти. И так далее пока не снимутся и запомнятся коды фазы и амплитуды с последнего преобразователя матрицы матричного преобразователя 2. На этом режим компенсации закончен. 25

В режиме измерений преобразователь 2 устанавливают на контролируемый участок объекта контроля. Переключатель 17 режимов переводят в состояние, соответствующее режиму измерений, при этом переключатель 17 режимов формирует сигнап, под управлением которого ключ 4 замыкает первый вход с вторым выходом, а второй вход— с первым выходом, счетчик 16 обнуля35 ется, первый блок 18 памяти работает в режиме выдачи информации на первый и второй ЦАП 13 и 14, а второй блок 19 памяти — в режиме записи информации с АЦП 7. Под управлением счетчика 1.6 коммутатор 3 выбирает первый преобразователь матрицы, напряжение с которого подается через ключ 4 на второй вход дифференциального усилителя 10.

Из ячейки памяти блока 18 памяти, соответствующей первому преобразователю матричного преобразователя 2, извлекаются коды амплитуды и фазы компенсирующего напряжения и подаются соответственно на первый и второй

ЦАП 13 и 14, на выходе первого ЦАП 13 формируется напряжение, пропорциональное амплитуде компенсирующего напряжения первого преобразователя мат- 5> рицы, подаваемое на первый вход перемножителя 8, на второй вход которого подается напряжение генератора 1. На выходе перемножителя 8 получается напряжение синусоидальной формы с амплитудой, равной амплитуде напря:кения с первого преобразователя в режиме компенсации. Это напряжение подается на первый вход линии 9 задержки, на второй вход которой подано напряжение с выхода ЦАП 14, пропорциональное фазе напряжения с первого преобразователя матрицы в режиме компенсации. На выходе линии 9 задержки, управляемой напряжением, получают синусоидальное напряжение, амплитуда и фаза которого равны амплитуде и фазе напряжения с первого преобразователя матричного преобразователя 2 в режиме компенсации. Это напряжение подается на первый вход дифференциального усилителя 10. При отсутствии дефекта под первым преобразователем на выходе дифференциального усилителя 10 получают минимальное напряжение, определяемое точностью компенсации, при наличии дефекта на выходе дифференциального усилителя 10 присутствует разбаланс, который через ключ 4, усилитель 5 и детектор 6 подается на АЦП 7, где переводится в цифровой вид, после чего запоминается в ячейке памяти блока 19 памяти, с выхода которого подается на видеоконтрольный блок 20 в виде точки яркость, пропорциональная напряжению разбаланса.

Аналогичные операции происходят при выборе всех остальных преобразователей матрицы, при этом на экране блока 20 получают картину распределения дефектов на контролируемом участке.

Формула изобретения

Устройство для вихретокового контроля содержащее последовательно соединен/ ные генератор синусоидального тока, вихретоковый матричный преобразователь и коммутатор, последовательно соединенные усилитель и амплитудный детектор, и видеоконтрольный блок, о т л и ч а ю щ е е с я тем, чта, с целью повышения точности контроля, оно снабжено включенным между выходом коммутатора и входом усилителя ключом, последовательна соединенными фазометром, первый и второй входы которого подключены соответственно к выходам генератора синусоидального тока и коммутатора, первым аналого12

h коимуяако у (СЯМ®Ь!)

Риг.z

/1 гЕнералору

СИНИСОИдИПЬ НОГ О

mrna

Составитель И.Рекунова

Техред Л.Сердюкова Корректор М.Шароши

Редактор Л.Повхан

Заказ 5223/44

Тираж 778 Подписное

В1IHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Ужгород, ул.Проектная, 4

5 цифровым преобра.з<:виталем, первым блоком памяти, первым цифр<>аналоговым преобразователем, пер<множителем, второй вход KoTupol< полклк <ен к выходу генератора синусоилального тока, линией задержки и дифференциальным усилителем, выход и второй вход которого подключены соответственно к вторым входу и выходу ключа, вторым цифроаналоговым преобразователем, включенным между вторым выходом первого блока памяти и вторым входом линии задержки, подключенными к выхо— ду амплитудного детектора последовательно соединенными вторым аналого6п83,4 Ь цифровым преобразователем и вторым б <оком памяти, выход к< торого подключен к входу видеокантрольного блока, последовательно соединенными генератором тактовых импульсов и счетчиком импульсов, выход которого соединен с вторыми входами коммутатора, первого и второго блоков памяти, и переключателем режимов, выход которого

t0 подключен к второму входу счетчика импульсов и третьим входам ключа, -первого и второго блоков памяти, а

I четвертый вход первого блока памяти подключен к выходу второго аналого15 цифрового преобразователя.