Универсальный логический модуль

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повьппение контролепригодности модуля. Универсальный логический модуль содержит информационные и настроечные входы, Элемент И-НЕ, элементы РАВНОЗНАЧНОСТЬ и сумматор по модулю два. Модуль работает в двух режимах. В рабочем режиме на настроечный вход, соединенный с первым входом элемента И-НЕ, подается сигнал низкого уровня. Тог-, да в зависимости от сигналов на других настроечньгх входах на выходе {модуля реализуется любая булева функция двух переменных. В режиме контроля на первый вход элемента И-НЕ подается сигнал высокого уровня. Тогда при подаче на остальные входы модуля соответствуклцего тестового набора на выходе будет наблюдаться меандр с периодом 6Т (t - время задёржки сигнал на одном элементе). Отсутствие меандра указывает на наличие в модуле неисправности. 1 ил. 1 табл. i (Л го О) о 00 ю

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (504 G F 0

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3867592/24-24 (22) 12.03.85 (46) 30.09.86. Вюл. 9 36 (72) С.Н.Изотов, В.И.Костеневич, В.А.Мищенко, Л.Б.Авгуль и M.М.Татур (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Ф 915073, кл.С 06 F 7/00, 1980.

Авторское свидетельство СССР

11 1084781, кл. G 06 F 7/00, 1981. (54) УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ (57) Изобретение относится к области . автоматики и вычислительной техники.

Цель изобретения — повьппение контролепригодности модуля. Универсальный логический модуль содержит информационные и настроечные входы, элемент И-НЕ, элементы РАВНОЗНАЧНОСТЬ

„„SU„„1260939 А 1 и сумматор по модулю два. Модуль работает в двух режимах. В рабочем режиме на настроечный вход, соединенный с первым входом элемента И-HF., подается сигнал низкого уровня. Тог-. да в зависимости от сигналов на других настроечных входах на выходе модуля реализуется любая булеза функция двух переменных. В режиме контроля на первый вход элемента И-НЕ подается сигнал высокого уровня.

Тогда при подаче на остальные входы модуля соответствующего тестового набора на выходе будет наблюдаться меандр с периодом 6T (? — время задержки сигнала на одном элементе).

Ю

Отсутствие меандра указывает на наличие в модуле неисправности. 1 ил.

1 табл.!

260939

В таблице приведен тип реализуемой функции в зависимости от комбинации сигналов на настроечных входах

Т

Тип реализуе- Комбинации сигналов мой функции на настроечных входах

2 3 4 5

0 0

0 О

0 1

1 0

1 0

1 1

1 1

0 0

0 О

0 1

0 х,х х,х

О

О х х

50

K XVX X

t Я г

0 х,Чх

55 х,нх х

Изобретение относится к автоматике и вычислительной технике.

Цель изобретения — повышение контролепригодности модуля.

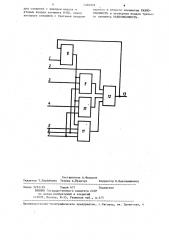

На чертеже представлена функцио- 5 нальная схема универсального логического модуля.

Модуль содержит настроечные входы

1 5, информационные входы 6 и 7, элемент 8 И-HE элементы 9-11 РАВНОЗНАЧНОСТЬ, сумматор 12 по модулю два, выход 13.

Модуль функционирует следующим образом.

Если сигнал на выходе элемента

8 И-НЕ равен единице, т.е. сигнал

И,= 0 а на информационные входы 6 и 7 соответственно подать переменные х, х, то при простом алфавите настройки (0,1} в зависимости от сигHGJIQB НасТроНКН Иг,И>, И, И на входах 2-5 на выходе 13 реализуется любая булева функция переменных

<таблица).

25 — ---------- — -т

Тип реализуемой функции

Комбинации сигналов на настроечных входах

2 3 4 5

0 1 х чх г

1 0

Х1

1 0 1

1 1 О хУх

xxvxx1

1 1 х,х

В режиме контроля, если сигнал

И, = f,è на настроечные и информационные входы 2-7 соответственно подать сигналы (011111) или (100000), то при правилbHoM функционировании модуля на выходе 13 будет наблюдаться меандр с периодом 6 . При неправильном функционировании меандра на выходе 13 не будет.

Формула изобретения

Универсальный логический модуль, содержащий первый, второй и третий элементы РАВНОЗНАЧНОСТЬ, причем первый и второй настроечные входы модуля соединены с первыми входами первого и второго элементов РАВНОЗНАЧНОСТЬ соответственно, о т л и ч а юшийся тем, что, с целью повышения контролепригодности, в него введены сумматор по модулю два и элемент И-НЕ, причем первый информационный вход модуля соединен с первым входом третьего элемента

РАВНОЗНАЧНОСТЬ и вторым входом первого элемента РАВНОЗНАЧНОСТЬ, второй информационный вход модуля соедиНен с вторыми входами второго и третьего элементов РАВНОЗНАЧНОСТЬ, третий, . четвертый и пятый настроечные входы модуля соединены соответственно с третьим входом третьего элемента

РАВНОЗНАЧНОСТЬ, первым входом элемента И-НЕ и первым входом суммато. ра по модулю два, второй, третий и четвертый входы которого соединены с выходами первого, второго и третьего элементов РАВНОЗНАЧНОСТЬ соответственно, выход сумматора по модулю

1260939

Составитель А.Федоров

Редактор Т.Парфенова Техред А.Кравчук Корректор M.Ìàêñèìèøèíåö

Заказ 5232/49 Тираж 6? t Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1)3035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.уж ор д, у . р

У г о л. П оектная, 4 два соединен с выходом модуля и вторым входом элемента И-НЕ, выход которого соединен с третьими входами первого и второго элементов РАВНОЗНАЧНОСТЬ и четвертым входом третьего элемента РАВНОЗНАЧНОСТЬ.