Устройство для деления двоичных чисел на три

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники. Цель изобретения - функциональное упрощение устройства. Устройство для деления двоичных чисел на три содержит регистр делимого, дешифратор, п-2 блоков формирования разрядов частного, каждый из которых содержит элементы НЕ, элементы И и элементы ИЛИ. Сущность изобретения заключается в том, что в каждом блоке формирования разрядов частного входная ин-- формация, поступающая на первый и второй входы блока, являющаяся остатками от деления старших разрядов, анализируется в прямом виде, а необходимые инверсии обеспечиваются после первой ступени анализа. Устройство для деления двоичных чисел на три может использоваться в специализированных вычислительных устройствах . 1 ил. С (Л NP СП о со |

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (58 4 G Об F 7 52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ЭТНРЫТИЙ (21) 3868787/24-24 (22) 11..03.85 (46) 30.09.86.Бюл. У 36 (72) В.А.Грачев, А;В.Гречухин, В.В.Королев и В.П.Семенов (53) 681. 325 (088. 8) (56) Авторское свидетельство СССР

Ф 506853, кл. G 06 F 7/52, 19?4.

Авторское свидетельство СССР

Р .1062690, кл. G 06 F 7/52, 1982. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ

ЧИСЕЛ HA ТРИ (57) Изобретение относится к области цифровой вычислительной техники.

Цель изобретения — функциональное упрощение устройства. Устройство для деления двоичных чисел на три соÄÄSUÄÄ 1260947 А 1 держит регистр делимого дешифратор н-2 блоков формирования разрядов частного, каждый из которых содержит элементы НЕ, элементы И и элементы

ИЛИ. Сущность изобретения заключает.ся в том, что в каждом блоке формирования разрядов частного входная информация, поступающая на первый и второй входы блока, являющаяся остатками от деления старших разрядов, анализируется в прямом виде, а необходимые инверсии обеспечиваются после первой ступени анализа. Устройство для деления двоичных чисел на три может использоваться в специализированных вычислительных устройствах. 1 ил.

1260947

Изобретение относится к цифровой вычислительной технике и может быть использовано в специализированных устройствах.

Целью изобретения является упро- 5 щение устройства.

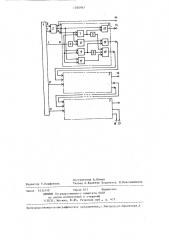

На чертеже представлена схема устройства для деления двоичных чисел на три.

Устройство содержит регистр 1 делимого, дешифратор 2, (n — 2) блоков

3 формирования разрядов частного, каждый из которых содержит элементы

HE 4-6, элементы И 7-10, элементы

ИЛИ 11 — 13. Выходы и-го и (п — 1) разрядов регистра 1 подключены соответственно к первому и второму входам дешифратора 2, первый выход которого соединен с (п-1-ой) выходной шиной 14 частотного, а второй и третий выходы подключены соответственно к первому и второму входам блока 3 формирования (n-2)-го разряда частного, первый выход каждого блока 3 подключен к соответствующей выходной шине 14 частного, по вторым и третьим выходам блоки 3 соединены между собой последовательно, второй и третий выходы блока 3 формирования первого разряда частного соединены с выходными шинами 15 и 16 ос татка. Выход каждого разряда регистра 1 от (n-2)-го разряда до первого разряда соединены с третьим входом соответствующего блока, 35

В каждом блоке 3 первый вход через элемент ИЛИ 12 подключен к первому выходу блока и к входам элементов И 9 и ИЛИ 11, второй вход под- 40 ключен к входам элементов И 7 и 8, третий вход подключен к входам элементов И 7, 9 и ИЛИ 11 непосредственно, а к входу элемента И 8 — через элемент HE 4, выход элемента И 7 45 подключен к входу элемента ИЛИ 12 непосредственно, а к входу элемента

И 10 — через элемент НЕ 5, выход элемента И 8 подключен к входу элемента ИЛИ 13, выход элемента

И 9 подключен ко входу элемента ИЛИ 13 непосредственно, а к входу элемента И 10 — через элемент

HE 6, выход элемента ИЛИ ll подключен к входу элемента И 10. Выход эле- 5 мента ИЛИ 13 является вторым выходом блока 3, а выход элемента И 10 является третьим выходом блока 3. Устройство работает следующим образом.

Делимое записывается в регистр 1.

Два старших разряда регистра 1 анализируются дешифратором 2, на первом выходе которого формируется единица при наличии единицы на выходах обоих старших разрядов регистра 1. На втором выходе формируется единица при наличии единицы только на выходе и-го разряда регистра 1. На третьем выходе формируется единица при наличии единицы на выходе (n-1) -го разряда регистра 1. Первый выход дешифратора 2 является (n-1)-ым разрядом частного, второй и третий выходы дешифратора 2 являются выходами, на которых формируются остатки "10" и "01". соответственно, полученные при делении информации, поступающей с выходов двух старших разрядов регистра 1.

В блоке 3 формирования (n-2)-го разряда частного анализируется информация, поступающая со второго и третьего выходов дешифратора 2, являющаяся остатками от деления двух старших разрядов регистра 1, и поступающая с выхода (n-2)-го разряда регистра 1.

На первом выходе этого блока формируется единица при наличии единицы на следующих его входах: на первом и третьем или на первом, или на втором и третьем. На втором выходе этого блока формируется единица при наличии единицы на следующих его входах: на первом и третьем или только на втором. На третьем выходе этого блока формируется единица при на— личин единицы на следующих его входах: только на первом или только на третьем, Первый выход этого блока 3 является (n-2)-ым разрядом частного, второй и третий выходы являются выходами остатков "10" и "01" соответственно, полученных при делении трехразрядного числа., поступающего на его входы.

В блоке 3 формирования (п-3)-го разряда частного анализируется ин1 формация, поступающая со второго и третьего выходов блока 3 формирования (n-2) разряда частного, являющаяся остатками от деления трех старших разрядов регистра 1 и поступающая с выхода (п-3)-го разряда регистра 1. Работа этого блока 3 формирования (п-3)-го разряда частного

1260947 и всех последующих блоков 3 формирования частного аналогична рассмотренному, Формула и з о б р е т е н и я 5

Устройство для деления двоичных чисел на три, содержащее регистр делимого, дешифратор и и-2 блоков формирования разрядов частного, каждый из которых содержит три элемента НЕ, три элемента ИЛИ и четыре элемента

И, причем выходы n-ro и (n-1)-го разрядов регистра делимого подключены соответственно к первому и второму входам дешифратора, первый выход которого соединен с (n-1)-й выходной шиной частного устройства, а второй и третий выходы подключены соответственно к первому и второму входам (n-2)-ro блока формирования разрядов частного, первый выход каждого блока формирования разрядов частного подключен к соответствующей выходной шине частного устройства, а второй и третий выходы k-го блока формирования разрядов частного (k=2, n"2) подключены соответственно к первому и второму входам (k-P)-ro блока формирования разрядов частного, вто- 30 рой и третий выходы первого блока формирования разрядов частного соединены с выходными шинами остатка устройства, выход 1-ro разряда регистра делимого (7=1,...,n-2) соединен с третьим входом I-го блока формирования разрядов частного, причем в каждом блоке формирования разрядов частного вход первого элемента НЕ соединен с третьим входом блока формиро- 4р вания разрядов частного, выходы первого и второго элементов ИЛИ соединены соответственно с первым и вторым выходами блока формирования разрядов частного, первый и второй входы первого элемента И соединены с вторым и третьим входами блока формирования разрядов частного соответственно, первый и второй входы второго элемента И соединены с вторым входом. блока формирования разрядов частного, выходом первого элемента НЕ соответственно, первый и второй входы третьего.элемента И соединены с первым и третьим выходами блока формирования разрядов частного соответственно, первый вход первого элемента ИЛИ соединен с выходом первого элемента И, первый и второй входы второго элемента ИЛИ соединены с выходами второго и третьего элементов И соответственно, первый и второй входы четвертого элемента И соединены с выходами второго и третьего элементов НЕ соответственно, о т л и ч а ю щ е— е с я тем, что, с целью упрошения устройства, в каждом блоке формирования разрядов частного первый вход блока формирования разрядов частного соединен с вторым входом первого элемента ИЛИ и с первым входом третьего элемента ИЛИ, третий вход блока формирования разрядов частного подключен к второму входу третьего элемента ИЛИ, выход первого элемента И подключен к входу первого элемента

НЕ, выход третьего элемента И подключен к входу второго элемента НЕ, выход третьего элемента ИЛИ подключен к третьему входу четвертого элемента И.

1260947

ff 1J

Составитель А. Клюев

Техред А.Кравчук Корректор M.Максимишинец

Редактор Т.Парфенова

5232/49 Тираж 671 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ

Производственно-полиграфическое предприятие,-..Ужгород,ул.Проектная,4