Устройство для адресации памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах на основе микроЭВМ . для увеличения подключаемого объема памяти. Целью изобретения является расширение функциональных возможностей. Устройство содержит регистр адреса, сумматор, регистр индекса, коммутатор , дешифратор режима, триггер и элемент ИЛИ. Данная совокупность признаков позволяет достичь цели изобретения. 4 ил,

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (gg 4 G 06 F 9/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3884640/24-24 (22) 15.04.85 (46) 30.09.86. Бюл. М - 36 (72) А.И. Ляхов, В.Д. Моисеев, В.В. Разумов, Э.П. Сенчук и Э.В. Щенов (53) 681.32(088.8) (56) Авторское свидетельство СССР

У 999054, кл. G 06 Р 9/36, 1981 ° .

Авторское свидетельство СССР

В 1068939, кл. G 06 F 9/36, 1982.

„.SU,», 1260955 А 1 (54) УСТРОИСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ (57) Изобретение относится к вычис- лительной технике и может быть использовано в вычислительных системах на основе микроЭВМ,. для увеличения подключаемого объема памяти.

Целью изобретения является расширение функциональных возможностей.

Устройство содержит регистр адреса, сумматор, регистр индекса, коммутатор, дешифратор режима, триггер и элемент ИЛИ. Данная совокупность признаков позволяет достичь цели изобретения, 4 ил, 1260955

1О

20

30

Изобретение относится к вычисли- . тельной технике и может быть использовано.в вычислительных системах на основе микроЭВМ для увеличения подключаемого объема памяти.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения подключения к микроЭВМ дополнительного объема памяти данных беэ изменения ее адресной сетки.

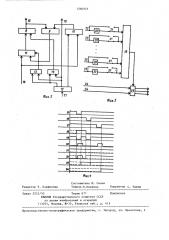

На фиг. 1 показана схема включения устройства для адрессации памяти в составе микроЭВМ; на фиг. 2структурная схема устройства адресации памяти, на фиг. 3 — структурная схема дешифратора режима; на фиг. 4временные диаграммы, поясняющие работу устройства, Схема включения содержит процессор 1, адресный 2, информационный 3 и управляющий 4 вход-выход процессора, устройство 5 для адресации памяти, запоминающие устройства (ЗУ) 6 (основное и дополнительное), вход 7 записи-считывания блоков памяти.

Устройство для адресации памяти микроЭВМ содержит регистр 8 адреса, сумматор 9, регистр 10 индекса, коммутатор 11, дешифратор 12 режима, триггер 13, элемент ИЛИ 14, адресный вьмод 15 устройства, информационный вход 16, вход 17 режима работы устройства, выход 18 управления записью-считыванием устройства.

Дешифратор режима содержит схему

19 совпадения, элементы НЕ 20, перемычку 21, вход 22 старших разрядов адреса, дешифратор 23,вход .24 младших разрядов адреса. На временной диаграмме представлены сигналы, вырабатываемые дешифратором 12 режима (25-27, соответствующие первому,второму и третьему выходам дешифратора

12), риггером 13 (28), схемой ИЛИ 14 (29), поступающие на информационные входы коммутатора со входа 16 (30) и выхода сумматора 9 (31), сигналы на информационном входе регистра адреса 8 (32) и на выходе этого реги.стра (33); а также сигналы на выходе регистра индекса 10 (34) .

Функция дешифратора 12 режима, включенного в состав устройства, заключается в вьщелении из совокуп-„ ности адресов, передаваемых по адресным шинам микроЭВМ, трех адресов, отведенньм данному устройству адресации и задающих режимы работы устройства, т.е. в вьщелении своих адресов.

На управляющий вход 7 основного ЗУ постоянно подается разрешающее напряжение ° Разрешение или запрет работы дополнительных ЗУ 6 осуществляется с устройства для адресации памяти 5 через этот же управляющий вход 7, С этого же устройства запается адрес обращения к дополнительному ЗУ.

Устройство для адресации памяти работает следующим образом.

Из адресов, передаваемых микроЭВМ по адресным входам-выходам 2, дешифра тор 12 вьщеляет три адреса (кода режима). Первый из них соответствует режиму занесения начального адреса массива чисел, размещенного в дополнительном ЗУ 6, в регистр 8 адреса числа, второй режиму обращения (на запись или чтение) к дополнительному

ЗУ 6, третий — режиму занесения индекса в регистр 10 индекса. При появлении этих адресов на адресных входах-выходах 2 возникают выходные сигналы на первом, втором и третьем выходах дешифратора 12 соответственно.

В режиме занесения информации в регистр адреса 8 по переднему фронту сигнала с первого вьмода дешифратора 12 триггер 13 устанавливается в положение, соответствующее разрешению прохождения через коммутатор 11 информации с информационного входа

16 на информационные входы регистра

8 адреса. По заднему фронту этого сигнала, поступающего через элемент

ИЛИ 14 на синхровход регистра адреса 8, информация заносится в регистр адреса 8.

В режиме занесения информации в индексный регистр 10 по заднему фронту сигнала с третьего выхода дешифратора 12, поступающего на синхровход регистра индекса 10, заносится информация, установленная на информационном входе 16. Содержимым индексного регистра определяется шаг, с которым будет без участия программы меняться содержимое регистра 8 адреса при каждом обращении к дополнительному ЗУ.

На выходе сумматора постоянно находится число, являющееся суммой содержимого регистра адреса 8 и регистра адреса .8 и регистра 10 индекса.

1260955

В режиме обращения к дополнительному ЗУ сигнал со второго выхода дешифратора 12 поступает на выход 18 и далее на вход 7 дополнительного

ЗУ 6. Передним фронтом этого сигнала триггер 13 устанавливается в положение, соответствующее прохождению информации с выхода сумматора 9 через коммутатор 11 на информационныйуход регистра адреса 8. Дополнитель10 ное ЗУ 6 воспринимает адрес, установленный на регистре адреса 8, управляющие сигналы, поступающие из микроЭВМ по входам-выходам 4, осуществля15 ет запись или чтение информации по входам-выходам 3. Задним фронтом сигнала со второго выхода дешифратора

12, поступающего на синхровход регистра 8 адреса числа через элемент

ИЛИ 14, производится установка но20 вого адреса обращения с информационного входа регистра. После этого устройство готово к обращению за следующим числом.

Частным случаем работы устройства может быть режим последовательного считывания или записи массива. При такой работе в индексный регистр заносится единица, содержимое регистра адреса числа увеличивается при

30 каждом обращении на единицу.

Формула изобретения

Устройство для адресации памяти, содержащее регистр адреса, сумматор, регистр индекса и коммутатор, причем выход регистра адреса подключен к адресному выходу устройства и к первому входу сумматора, второй вход и выход которого подключены соответственно к выходу регистра индекса и к первому информационному входу коммутатора, выход которого подключен к информационному входу регистра адреса, о т л и ч а ю щ е ес.я тем, что, с целью расширения функциональных возможностей за счет адресации расширенного адресного пространства при ограниченной разрядности адресного слова, в него введены элемент ИЛИ, триггер и дешифратор режима, причем информационный вход устройства подключен к информационному входу регистра индекса и к второму информационному входу коммутатора,.управляющий вход которого подключен к выходу триггера,. выходы установки в "1" и в "О" которого подключены соответственно к первому и второму выходам дешифратора режима и к первому и второму входам элемента ИЛИ, третий выход дешифратора режима подключен к синхровходу регистра индекса, выход элемента ИЛИ подключен к синхровходу регистра адреса, второй выход дешифратора режима подключен к выходу управления записью-считыванием устройства, вход дешифратора режима подключен к входу режима работы устройства.

1260955

Составитель И. Силин

Техред Л.Олейник

Корректор С ° Черни

Редактор Т. Парфенова

Закаэ 5233/50 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Уж ор д, у . р

r о л. П оектная 4