Устройство для определения старшего значащего разряда

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам приема и передачи информации . Изобретение является дополнительным к известному устройству для определения старшего значащего разряда по авт. св. СССР № 1164707, предназначенному для одновременной шифрации единиц и нулей в п-разрядном двоичном коде. Целью изобретения является расширение функциональных возможностей устройства за счет определения количества единицы в п-разрядном коде. Устройство для определения старшего значащего разряда содержит элемент ИЛИ, элемент НЕ, блоки выделения старшего разряда, группы элементов ИЛИ, группы элементов И и шифраторы. Введение в устройство дополнительного элемента И с соответствующими связами и использование дополнительных выходов позволяет получить информацию о количестве единиц в п-разрядном двоичном коде, 2 ил. с « (Л О) о СП ю

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) 5 А2 (50 4 G 06 F 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СОИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1164707 (21) 3891182/24-24 (22) 20.03.85 (46) 30.09.86. Бюл. № 36 (75) Ю.С.Тархов (53) 681.325(088.8) (56) Авторское свидетельство СССР № 1164707, кл. G 06 Р 9/46, 1984. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СТАРШЕГО ЗНАЧАЩЕГО РАЗРЯДА (57) Изобретение относится к вычислительной технике, в частности к устройствам приема и передачи информа-. ции. Изобретение является дополнительным к известному устройству для определения старшего значащего разряда по авт. св. СССР ¹ 1164707, предназначенному для одновременной шифрации единиц и нулей в п-разрядном двоичном коде. Целью изобретения является расширение функциональных возможностей устройства за счет определения количества единицы в и-разрядном коде.

Устройство для определения старшего значащего разряда содержит элемент

ИЛИ, элемент НЕ, блоки выделения старшего разряда, группы элементов ИЛИ, группы элементов И и шифраторы. Введение в устройство дополнительного элемента И с соответствующими свяэами и использование дополнительных выходов позволяет получить информацию о с количестве единиц в и-разрядном дво- у ,ичном коде, 2 ил.

1260957

Изобретение относится к вычислительной технике, может быть использовано в цифровых вычислительных устройствах, а также в устройствах приема и передачи информации и является усовершенствованием известного устройства, описанного в авт. св, Ф 1164707.

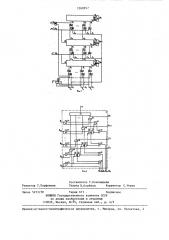

Целью изобретения является расширение функциональных возможностей за 10 счет определения количества единиц в и-разрядном двоичном коде, На фиг. 1 приведена структурная схема устройства; на фиг.2 — структурная схема блока выделения старше- «5

ro разряда.

Устройство содержит элемент ИЛИ 1, элемент НЕ 2, блоки 3, — 3„ выделения старшего разряда, группы элементов

ИЛИ 4, группы элементов И 5, сигналь- 20 ный выход 6 устройства, прямые и инверсные разряды 7 входного тока, шифраторы 8 — 8„, выходы 9 элементов ИЛИ

4, выходы 10 — 10„, 11, 1?, — 12„ бло— ков 3, выходы 13 устройства.

Блок 3 (фиг.2) содержит элементы

НЕ 14, элементы И-HE 15, элементы И

1Ü, элементы HE 17, элементы И 18, элемент ИЛИ-НЕ 19.

Дополнительные элементы, введенные g в устройство: элемент И 20 и выходы

21 устройства.

Устройство работает следующим образом.

Прямь.е и .«нверсные выходы разрядов анализируемого двоичного кода А подаются на входы 7 устройства.

Возможно три случая: во всех разрядах кода записаны нули, во всех разразрядах кода записаны единицы и ко- 40 личество разрядов, в которые записаны единицы, меньше и.

В первом случае на выходе элемента

ИЛИ 1 нулевой потенциал. Элемент И 20 закрыт нулевым потенциалом прямого выхода n-ro разряда анализируемого кода.

На вторых входах элементов И 5 первой группы разрешающий потенциал„

Инверсный аяализируемый код А через открытые элементы И 5, элементы ИЛИ

4 поступает на входы 9 блока виделения старшего разряда 3. В блоке 3 выделяется старший значащий разряд. Сигнал, равный единице, будет на выходе

10,, так как на всех входах 9 присутствуют единицы, а на всех остальных выходах 10 должен быть О.

На выходах 13 шифратора 8„ двоичный код, соответствующий номеру старшего разряда (в данном случае ...001), С выходов 11 анализируемый код А с исключаенной старшей единицей поступает на следующий блок выделения старшего разряда 3, через элементы

ИЛИ 4 втброй группы. Нулевой сигнал на выходе 12 блока выделения старшего разряда 3 будет в случае, еслй количество единиц на входах 9 данного блока более одной.

Следовательно, в данном случае на выходе 12 блока 3 . нулевой сигнал, а на элементах И 5 второй группы запрещающий потенциал. В следующем блоке вьщеления старшего разряда Зя-g выделяется старший значащий разряд, из остатка анализируемого кода определяется условие — количество единиц больше одной или меньше, исключается старший значащий разряд. Сигнал единицы на выходе 10«, а на выходе 12— ноль. На выходе шифратора 8„ « двоичный код номера разряда (...010). Далее схема работает аналогично.

На выходах шифраторов 8« — 8„ находятся последовательно расположенные двоичные коды номеров разрядов анализируемого кода, находящихся в нуле (...001, ...010, ...011, ...111), На выходах 12 блоков 3 — 3„ для данного случая нули.

Таким образом, на всех выходах 21 нулевой потенциал, что соответствует отсутствию единиц в анализируемом коде А.

Во втором случае, когда во всех разрядах анализируемого кода записаны единицы, на выходе элемента ИЛИ 1 единичный потенциал, а на вторых входах элементов И 5 первой группы — запрещающий. Прямой код А через элементы ИЛИ поступает на входы блока выделения старшего разряда 3 . Дальнейшая работа устройства аналогична описанной в первом случае. На выходах шифраторов 8 - 8„ последовательно расположенйые двоичные коды номеров разрядов анализируемого кода, находящихся в единице (.. ° 001, ...010, ° ..011, ...111) .

Единичный сигнал на выходе "и"

21,, так как единица с прямого выхода и-го разряда поступает на первый вход, а пройдя через блоки вьщеления старшего разряда 3 - 3„ — на второй вход элемента И 20. На остальных выходах

1260957

21 нули, так как на всех выходах 12, блоков 3 — 3„ (для данного случая) нулевой потенциал.

В третьем случае, когда в К разрядов анализируемого кода записаны еди- 5 ницы, на выходе элемента ИЛИ 1 единичный потенциал, на вторых входах элементов И первой группы — запрещающий потенциал.

Прямой анализируемый код А через элементы ИЛИ поступает на вход блока

3„„, В блоке 3„ выделяется старший значащий разряд, в котором записана единица. С выходов 11 передается на сле- 15 дующий блок 3„, анализируемый код

А с исключенной старшей единицей.

Единичный сигнал на выходе 10, номер которого соответствует номеру разряда, в который была записана старшая единИца, а на выходе шифратора 8 — соответствующий ему двоичный код. На выходах 10 К-ro блока вьщеления старшего разряда 3„ единичный сигнал, соответствующий номеру разряда, в ко- 5 торый была записана последняя единица, а на выходе шифратора 8 — соотк ветствующий ему двоичный код.

На выходе 12 блока 3„ единичный потенциал, так как на входы этого„ блока поступил код, в котором единица записана только в одном разряде, на вторых входах элементов И 5 разрешающий потенциал.

На входы блока 3„, через открытые элементы И 5,. элементы ИЛИ 4 поступает инверсный анализируемый код.

Единичный сигнал на выходе 10, номер которого соответствует номеру стаРше-4О

jro разряда кода А, в котором записан, . ноль, а на выходе шифратора 8„, соответствующий ему двоичный код. Далее схема работает аналогично описанной в первом случае ° На выходах шиф45 ратора 8 - 8„ последовательно расположенные двоичные коды номеров разрядов, в которых записаны единицы, а на выходах 8„., — 8, - номера разрядов, находящихся в нуле. На выходе элемента И 20 (для данного случая)

50 ноль, так как на первом и втором входах возможно только противоположное значение сигналов. Единичный сигнал с выхода 12 блока 3g поступает на выход К, что соответствует наличию К

I t 1! 55 единиц в анализнруемом коде А. На всех остальных выходах 21 нули.

Блок выделения старшего разряда.3 работает следующим образом.

Анализируемый код поступает на входы, Элементы И-НЕ 15, НЕ 17 и элементы И 16 служат для выделения старшего значащего разряда, поступившего на входы. Схема распределяет потенциалы таким образом, что единицы старшего разряда, распространяясь на значащие младшие разряды, запрещает прохождение сигналов значащих цифр на выходы 10 младших разрядов блока независимо от того, какое число записано в пределах разрядности. Сигнал, равный единице, на том выходе 10, номер которого соответствует входу, на котором присутствует старшая единица, на всех остальных выходах 10 должен быть "0", независимо от состояний остальных входов.

Когда-число единиц в анализируемом коде больше одной, сигнал, равнй нулю, находится на выходе элемента ИЛИНЕ и выходе 12 ° Единица старшего разряда кода, распространяясь по цепочке элементов И-НЕ 15 и элементов НЕ 17, дает разрешение на одни входы элементов И 18, другие входы которых подключены к входам блока младших разрядов. Единица любого младшего разряда через элемент И 18, элемент ИЛИ-НЕ 19 поступает на выход 12, а на выходы

11 — разряды анализируемого кода с исключенной старшей единицей.

Формула изобретения

Устройство для определения старшего значащего разряда по авт. св.

У 1164707, отличающееся тем, что, с целью расширения функциональных возможностей за счет определения количества единиц в п-разрядном двоичном коде, в него введен дополнительный элемент И, причем первый его вход соединен с выходом n-ro элемента

ИЛИ и-й группы, а второй вход — с втовторым входом и-го элемента ИЛИ первой. группы, выход дополнительного элемента И и выход элемента ИЛИ-НЕ

i-го блока вьщеления старшего разряда (i = 2, ..., n) являются дополнительными выходами наличия единиц в анализируемом коде устройства.

1260957

Составитель Г.Пономарева

Техред П.Олейник Корректор С.Черни

Редактор Т,Парфенова

Заказ 5233/50 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. ужгород, ул. Проектная, 4