Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано для согласования по скорости передачи при вводе данных от источников многоканальной измерительной информации в систему сбора и обработки информации. Сущность изобретения состоит в повышении информационной емкости устройства за счет обеспечения возможности уменьшать текущую избыточность данных некоторых измерительных каналов. Адресная часть (номер канала) каждой информационной посылки сравнивается с аналогичной частью предыдущей посылки и, в случае их равенства, производится обращение к дополнительному блоку памяти по адресу, равному адресной части информационной посылки. При чтении из дополнительного блока памяти нулевого бита данных производится запись параметра в основной блок памяти без модификации адреса обращения. 3 ил. ГС 05

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (Ь1) 4 G 06 F1300

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМЪ СВИДЕТЕЛЬСТВУ

Ю

Cb

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3868173/24-24 (22) 15.03.85 (46) 30.09.86. Бюл. № 36 (72) В. С. Лупиков и В. Г. Зинин (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 822293, кл. G 11 С 9/00, 1081.

Авторское свидетельство СССР № 1163359, кл. G 11 С 9/00, 1984. (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение может быть использовано для согласования по скорости передачи при вводе данных от источников многоканальной измерительной информации в сисSU» 1261010 А1 тему сбора и обработки информации. Сущность изобретения состоит в повышении информационной емкости устройства за счет обеспечения возможности уменьшать текущую избыточность данных некоторых измерительных каналов. Адресная часть (номер канала) каждой информационной посылки сравнивается с аналогичной частью предыдущей посылки и, в случае их равенства, производится обращение к дополнительному блоку памяти по адресу, равному адресной части информационной посылки. При чтении из дополнительного блока памяти нулевого бита данных производится запись парамет. ра в основной блок памяти без модификации адреса обращения. 3 ил.!

261010

Изобретение относится к Выч исл ител }ной технике и может быть использовано lipH построении буферных запоминающих устройств (БЗУ) в системах сборы и ооработки измерительной информации.

Цель изобретения — повышение информационной емкости устройства.

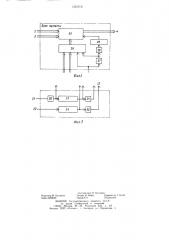

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 -- приведена структурная схема блока памяти; Н3 фиг. 3 — структурная схема блока синхронизации.

Буферное запоминающее устройство содержит блок 1 памяти с информационными входами 2 первой группы, 3 второй .-руппь;. и информационными выходами 4, первый счетчик 5 адреса, второй счетчик 6 адреса, реверсивный счетчик 7, элемент ИЛИ--HE 8. первый 9, второй 10 Выходы управления, iiepвый 11, второй 12 элементы И, три«гер 13, первый 14, второй 15 регистры, блок синхронизации 16, элемент НЕ. 17, элемент ИЛИ

18, дополнительный блок 19 памяти, блок

20 сравнения, второй 21> третий 22 входы управления, третий выход 23 управления. первый вход 24 управления.

Блок 1 памяти содержит накопитель 25, элементы И вЂ” ИЛИ 26, элемент HE 27,:)лемент 28 задержки и формирователь 29 импульсов.

Блок 16 синхронизации содержит первый 30, второй 31, третий 32 элементы задержки, первый 33 и второй 34 формирователии и м пульсов.

В качестве дополнительного блока 1 ;) памяти может использоваться постоянн(к. запоминающее устройство, в ячейках которого по адресам, однозначно соответствую«цим адресной части информационных и нъ«лок, записаны нулевые биты для тех кана лов, данные от которых допускают сокр".щения текущей избыточности, и единичнь!е биты для тех каналов, данные ol которых не допускают сокращения текуц,ей избыто:.— ности.

Устройство работает следующим образом, Перед началом работы сигналом на Bxo— де 24 счетчики 5 — 7 устанавливаются в нулевое состояние.

В режиме записи информация 1!2 Вход устройства поступает в виде слов, содержагцих адресный признак (г!Омер канала), KOторый присутствует на входах 3 устройства, и параметр, который присутствует на Вхс дах 2 устройства в сопровож. }(нии синхросигнала записи на входе 2 устройства.

По переднему фронту сигнала } а входе 21 устройства номер канала записыва >Тся в регистр 14, а предыдущее содержимое регистра !4 переписывается В регистр Ь.

Производится чтение бита информации из блока 19 памяти, записанного по адресу, р33I!0vó содержимому регистра 15> которое поTxrl2eT;2 ин(рормационный в од триггера

13. Г}!}!хроси! На„«, задержанный на элементе

30 задерхкки блока 16 синхронизации, устаЭ !

«3вл и вае-. В соответствующее состоя н ие три!.гер 3. 0;}}IE)Bppменно блок 20 сравнения сравнивает содержимое регHCTpoB !4 и !5. (.Одержи)!Ое первого счет !ика 5 адреса и

ppBepcHBi«oi.о с ет !ика 7 увеличнваегся на

ЕДИ! ИЦУ За }НИМ фРОНтОМ СигиаЛа На тРЕ Q тье:i выходе г)дока 16 синхронизации, т.е. (инхросигналом:«аниси, прошедшим последоВатег!ьно эг!е! CHI 30 за 1ержки и формирователь 33 в следующих случаях: при высоком

>„",)овн(CHI H2. !3 I 3 Вы хо;}е элем HT2 ИЛИ

1-1 Б 8, т.е. lip!« состоянии «Буфер пуст»;

IlpH разли I}j;))j содержимом регистрОВ 14 и !

5, т.е. Нри низком ровне сигнала на Вьь(оде блока 20;равнения;;!ри равном содержимом регистров !4 и !5 и высоком уровне cHIнала триггера 3.

Выделение эти; сг!) чаев производится элеыентаыи И ! и !2 и элеме«г:ом ИЛИ 18. (;иг}!27! I-d выходе формирователя 33. проходя элсмеHT 3 33.« D)KKH, постыl!2PT Hd вход у правления блока памяти и подключает через элемент Н!. 27 к а,}ресным входаы накопителя 25 iepps элех«е}!ты И вЂ” ИЛИ

26 разрядные зыхо Ill перво«с !ет ика 5

3 }Рt Cа,:.! Еl Ко ГОРОМ С(!)ОP !> «и Рова li T(.K), }ЦИ и адрес за IHcH. 1!о этому адресу запись«вается информация, присутствующая на водах

2 и 3 устройства, 3 HdKollHT ль 25 гкгналом на вьixo,jc элемен !а Н1 27, задержанным

I>2 э(«еыенге 28 задержки и сфор)!ирован}«ы)! формирова I(хl(.)I 2)9 .)}«Иись lloc.lе )х K)IE}H. }!H фОРы аци )1131>lx !10c > !ок l3 О 10к ИамЯти lipÎ

35 1:Вводится акал )i Hчно. 3;!нксь н Ь3;) проводится при ни)коы уровне сигнала на ВтоРо выходе ) УIIPBB)IPI«HH Ус«РОЙства, T.e.

llpH нулевом:«:.«3чсни и стар ц:его разряда реверсивного счет,«к!! 7 разря.- ность счет«ика 7 а сди} Hl::у пр(нын:ает разрядность

40 (ч(T HKOB о H ()) . 11}>!CОКИ Й х pOBE HI> CH I!«3 13

l I 2 B bI X 0 ÄP 1 0 С I p O H CÒ В 3 С B H 2 PTP. I ь Е Т В у E . T 0 состоянии «Бх(!)ер jalioлнен».

П р и :; тени !. и н ф 0 р м 2 н и и ; i }j x p o c H I l! 2 л пения Hd в. Оде 22 устройства н(ктупает Hd

Вход формир(»)атсля 34 блока 16 скн .poljljзации, который llo иере;..нему фр ) «ту сигна. l2 ())ОР МИР>> Е .Т ИМ П У.1ЬС, !!О KOТС )О Ы У v103 Кфицируется сс (ержкыое Втооого с «етчика 6 и 1ppc3 «дооавляется (ди!шца и реверсив1!Ого сче- ика 7 (выч«-тается единица) . ПроизводиTся чте;IHC иl,ôopxi2ции из HBKоните ля 25, к 3. ö:(сны в: ()даы котс()ого н )TÎ

Время IIO >I K. I IOBP HI! че!) Сз злеXIPIITI>i И --И, 1 И

26 В«,!х(:дные разрядные сигналы BTîpîãî ("«е тчика 6 адр(cd. (}! г:! 3,1 на . p(т ьсм Bb!) o1Е 23 ) crpOHc EBa. т е. 3!де)жан!ый }!3 3 ie—

>J ,!енте 32 задержки с!«! }!Нл формирона) еля

34, я Вляется и ы II) л ьсом сО!! 2ОВОждения с:«ита иной информации. -1i cHHP последу K)1261010 щих информационных посылок из БЗУ производится аналогично. Чтение данных из устройства возможно при низком уровне сигнала на первом выходе 9 управления устройства, высокий уровень сигнала на выходе элемента ИЛИ вЂ 8 свидетельствует о состоянии «Буфер пуст».

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, информ ационные входы первой и второй групп которого являются информационными входами устройства, информационными выходами которого являются информационные выходы блока па- мяти, адресные входы первой и второй групп которого соединены с выходами первого и второго счетчиков адреса, реверсивный счетчик, выходы которого подключены к входам элемента ИЛИ вЂ” НЕ, выход которого и один из выходов реверсивного счетчика являются 20 соответственно первым и вторым управляющими выходами устройства, первый элемент

И, выход которого соединен с первыми входами первого счетчика адреса и реверсивного счетчика, второй элемент И, триггер, выход которого соединен с первым входом второго элемента И, вторые входы счетчиков адреса соединены с третьим входом реверсивного счетчика и являются первым управляющим входом устройства, отличающееся тем, что, с целью повышения информационной емкости устройства, оно содержит первый и второй регистры, блок сравнения, блок синхронизации, элемент НЕ, элемент

ИЛИ, дополнительный блок памяти, входы которого соединены с выходами второго регистра и входами первой группы блока сравнения, входы второй группы которого подключены к выходам первого регистра и информационным входам второго регистра, управляющие входы регистров соединены с первым входом блока синхронизации и являются вторым управляющим входом устройства, третьим управляющим входом которого является второй вход блока синхронизации, первый выход которого является третьим управляющим выходом устройства, второй, третий, четвертый, пятый выходы блока синхронизации соединены соответственно с первым входом триггера, первым входом первого элемента И, первым входом второго счетчика адреса и вторым входом реверсивного счетчика, управляющим входом блока памяти, информационные входы второй группы которого подключены к информационным входам первого регистра, выход блока сравнения соединен с вторым входом второго элемента И, входом элемента НЕ, выходы элемента ИЛИ вЂ” HE, второго элемента И, элемента НЕ соединены с входами элемента

ИЛИ, выход которого подключен к второму входу первого элемента И, выход дополнительного блока памяти соединен с вторым входом триггера.

126!010

21 — Г Ф

Составитель О. Кулаков

Редактор M. Циткина Техред И. Верес Корректор T. Колб

Заказ 5238/53 Тираж 67! Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, r. Ужгород, ул. Проектная, 4