Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к аналоговым запоминающим устройствам, и может быть использовано при построении аналого-цифровых преобразователей. Цель изобретения повышение точности устройства - достигается введением стабилизатора тока, дополнительного усилителя и дополнительного источника напряжения смещения. Предложенное устройство содержит усилители и ключи, выполненные на биполярных транзисторах , пассивные элементы на резисторах , ограничительный диод, стабилизатор тока, источники напряжения смещения, накопительный элемент на конденсаторе, щины питания, щину стробирующих импульсов и щину напряжения ограничения. Коллектор транзистора первого усилителя является выходом устройства и соединен с одной обкладкой конденсатора и с эмиттером транзистора первого ключа. Коллектор транзистора первого ключа соединен с первой щиной питания и входом стабилизатора тока, выход которого соединен с эмиттером транзистора второго усилителя с базой транзистора первого ключа, с анодом ограничительного диода и с коллектором транзистора второго ключа. Эмиттер транзистора второго ключа соединен с эмиттером транзистора первого усилителя и с коллектором транзистора третьего усилителя. База транзистора второго усилителя является входом устройства и соединена через первый резистор с второй обкладкой конденсатора, с коллектором транзистора третьего усилителя и через второй резистор с входом второго источника напряжения смещения, с коллектором транзистора второго усилителя и второй щиной питания . База транзистора третьего усилителя соединена с выходом второго источника напряжения смещения, база транзистора первого усилителя соединена с выходом первого источника напряжения смещения, база транзистора второго ключа соединена с щиной стробирующих импульсов, катод ограничительного диода соединен с щиной напряжения ограничения. 1 ил. (/) Ю О5

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (,ь1) 4 G 11 С 27 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3885245/24-24 (22) 17.04.85 (46) 30.09.86. Бюл. № 36 (72) Ю. В. Левочкин и Л. Н. Матвеева (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР № 656108, кл. G 11 С 27/00, 1979.

Авторское свидетельство СССР № 653685, кл. G 11 С 27/00, 1979. (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, в частности к аналоговым запоминающим устройствам, и может быть использовано при построении аналого-цифровых преобразователей. Цель изобретения повышение точности устройства — достигается введением стабилизатора тока, дополнительного усилителя и дополнительного источника напряжения смещения. Предложенное устройство содержит усилители и ключи, выполненные на биполярных транзисторах, пассивные элементы на резисторах, ограничительный диод, стабилизатор тока, источники напряжения смещения, накопительный элемент на конденсаторе, шины питания, шину стробирующих импульсов и шину напряжения ограничения. Коллектор транзистора первого усилителя является вы„„SU„„1261013 А1 ходом устройства и соединен с одной обкладкой конденсатора и с эмиттером транзистора первого ключа. Коллектор транзистора первого ключа соединен с первой шиной питания и входом стабилизатора тока, выход которого соединен с эмиттером транзистора второго усилителя с базой транзистора первого ключа, с анодом ограничительного диода и с коллектором транзистора второго ключа.

Эмиттер транзистора второго ключа соединен с эмиттером транзистора первого усилителя и с коллектором транзистора третьего усилителя. База транзистора второго усилителя является входом устройства и соединена через первый резистор с второй обкладкой конденсатора, с коллектором транзистора третьего усилителя и через второй резистор с входом второго источника напряжения смещения, с коллектором транзистора второго усилителя и второй шиной питания. База транзистора третьего усилителя соединена с выходом второго источника напряжения смещения, база транзистора первого усилителя соединена с выходом первого источника напряжения смещения, база транзистора второго ключа соединена с шиной стробирующих импульсов, катод ограничительного диода соединен с шиной напряжения ограничения. 1 ил., 2610 3

Изобретение относится к вычислительной технике, в частности к технике аналоговых запоминающих устройств, и может быть использовано при построении аналогоцифровых преобразователей.

Целью изобретения является повышение

« точности устройства.

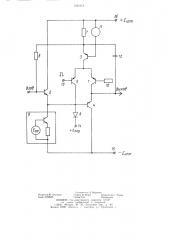

На чертеже приведена функциональная схема предложенного устройства.

Устройство содержит усилители, выполненные на транзисторах 1, 2 и 3, ключи на транзисторах 4 и 5, пассивные элементы на резисторах 6 и 7, ограничительный диод 8, стабилизатор 9 тока, источники 10 и 11 напряжения смещения, наког ительный элемент на конденсаторе 12, шину 13 стробирующих импульсов, шину 14 напряжения ограничения, шины 15 и 16 питания.

Аналоговое запоминающее устройство работает в двух режимах: в режиме выборки происходит образование выборочных значений сигнала на конденсаторе 12, а в режиме )0 хранения образованное выборочное значение сигнала на конденсаторе 12 поддерживается постоянным и используется для работы внешних устройств.

В режиме хранения потенциал на базе транзистора 5 ниже потенциала источника

10 смещения, поэтому транзистор 5 открыл, а транзистор 1 закрыт. Величина токов через стабилизатор 9 и транзистор 3 выбрана таким образом, что ток через транзистор 3 больше тока стабилизатора 9. Потенциал шины 14 больше максимальной амплитуды входного сигнала или равен ему. За счет этого ток транзистора 3 протекает через транзистор 5, стабилизатор 9 и диод 8 и закрывает транзисторы 2 и 4. Конденсатор 12 оказывается отключенным транзисторами

4и l.

В режиме образования выборочного значения сигнала положительный импульс с ц!ины 13 стробирующих импульсов приводит к переключению транзисторов 1 и 5. в результате чего транзистор 5 закрывается, а транзистор 1 открывается. При этом транзисторы 2 и 4 открываются.

Подбирая токи через стабилизатор 9 и резистор 7, сохраняя при этом условие, что ток через резистор 7 должен быть несколько больше тока стабилизатора 9, можно добиться нулевого потенциала на выходе устройства. Эти два условия легко выполнить при использовании в первом транзисторе с входной характеристикой, расположенной

5G на оси напряжений дальше от нулевой точки.

Если при этом в момент выборк): на входе устройства присутствует отри цат»1ьныи сигнал, то конденсатор 12 заряжается током по следующей цепи: шина 16 питания— резистор 7 — конденсатор !2 -- Tpaiia!t «c тор 4 — — шина 5 питания.

Так как сопротивление открытого транзистора 4 со стороны эмиттера Очень мило

Т0 ток заряда конденсатора 12 определяется величиной резистора 7 и величиной на1!pHжения Ha tiIYi lax 16 Y !5. Hc IHHHkta BTol0

На !адЬНОГО ТОКО С IIOXI 0IÖÜÞ резИСТОра I может быть выбраны сколь угодно большой, но в пределах безопасного значения для транзисторов, работающих в импульсном режиме. В начальный момент времени на транзисторе 7 создается значительное па;!ение напряжения, которое приводит к запиранию транзисторов 1 и 3. !

Iu мере заряда конденсатора 12 ток заряда уменьшается. тра!1зисторы 1 и 3 открываются и через них Ha"инаст протекать ток.

При достижении потенциалом на выходе устройства значения, равного входному, ток через конденсатор 2 прекращается и через транзисторы 1 и 3 течет зес. ТоК стабилизатора 9. Следует заметить, что асть тока, текущего через резисtop 7, ответвляется в резистор 6 и далее на источник входного сиги ала, !)г и чем вел и чины этого ответвляюпегocH в резистор 6 тока незначительна и

МЕНЯСТСЯ В З3ВИСИМОСТИ ОГ 3МПЛИТУДЫ И ItOлярности входного сигнала. Это необходимо длн поддержания бессдвиговой !ередачи входного сиг:-1ала на выход устройства.

При уменьшении входного сигнала увеi1Hчивается напряжение в транзисторе 2 и происходит уBEличение коэффицие:1та усиления .Ф, а это, в свою очередь, при постоянном токе эмиттера приводит к уменьшению

—:îêà базы ы уменьшеннго падения напряжений 11а,. Кроме того, уменьшение тэка базы транзисторы 2 может произойти из-:33 неидепа рам(тров с (3()H:1изатора 9, именно при, лен пении потенциала на эмит тере транзистора 2 ток через стабилизатор

9 несколькэ умс 1ьц)итси.

0ДHOBP()iV0HH0 HPH У V 0 I! k H(IC .!I HH BXO;1)tOI 0 (и Гнала умень1:.12ется ttaflpH&EHH2 1 ),= на ! ранзистор 4, (TO привOJHT K X: ".Hk t(IBHHIO .8, увеличеник) тока базы и увеличению L(),этого транзистора. Все это приводит к смеltkEник) ассолютього значения выходного сигнала по Отноц! ени!о к входному.

С другой стороны, при отрицательном входном cHI íà ic нес) олько увел! )Иваетсн

Ton., огветьляюш1;йся B резистор 6, и соответственно уменьшается ток через транзистор 4. Это !рив )iHT к уменьшению тока базь; транзистора - . и к уменьuJCI!HII) его напряжения 1.!2 IIO,,бирая вели 1ину резистора 6, можно доб!Ггbcи (:динаковых (н; величине измене):Hii iia: рян(ений UG тэанзистор(гн 2 и 4 I:pè и)»е:10!!Н) х tixo, kíûx .-.Нгналов, 1.с. доби(ься бе(сдвигоной 1(ередачи входно (> сиГ:-!(!л<1 ki вь(ход cтрi)йствd нэH вс(.х

ЗН 3 (ЕIIH)IX (I М Н IИ 1 У J Bi ВХОДНОГО СИ: lid. I d.

I I pH OC ) Ilk(C 1 в. I(ii! И выборки CH CH3.13 ll(.Гожительной (н) IHp!Io((или к«гдa aм1)литуд3 входного сиги а 13 fipl.: !юследней ныб()рке бэ;.ее !1Ог!О.китсл)на, чем t): ðc) t:,12610!3

3 душей выборке) устройство работает следующим образом.

Форм ула изобретения

В начальный момент времени после подачи стробируюшего импульса на шину

13 напряжение на конденсаторе 12 меньше, чем на входе устройства, при этом транзистор 4 закрыт. Ток с шины 16 через резистор

7 замыкается через переход эмиттер-база транзистора 3 и источник 11 напряжения смещения. Источником этого тока является источник 11, а ограничителем тока является резистор 7. Таким образом, через базу транзистора 3 протекает ток. величиной

Е м — 0 бз1ь би.—

Под действием тока транзистор 3 открыт, также открыт и транзистор 1. Конденсатор

12 при этом разряжается через транзисторы

1 и 3 током, равным H 1б,, т.е. начальная величина тока разряда конденсатора 12 в

Я раз больше, чем постоянная величина тока с шины 16. По мере разряда конденсатора

12 потенциал на. его обкладке, соединенной с выходом устройства, повышается. Потенциал повышается до тех пор, пока транзистор 4 не откроется. При открывании транзистора 4 ток через резистор 7, который до этого ответвлялся только в базу транзистора 3, идет через коллектор транзистора 3, транзистор I и транзистор 4. При этом резко уменьшается ток базы транзистора 3 ток перезаряда конденсатора 12. Разряд конденсатора 12 прекращается, когда напряжение на его обкладке, соединенной с выходом устройства, будет равно входному напряжению.

Таким образом, как и при выборке отрицательных значений входного сигнала, выборка положительных значений сигнала производится путем перезаряда конденсатора 12 током, значительно превышающим постоянный ток с шины 16. Благодаря этому можно увеличить емкость конденсатора 12, что позволяет снизить погрешность «пролезание» строб-импульса на выход устройства через емкость Св, транзистора 4.

Аналоговое запоминающее устройство, содержащее первый усилитель на первом транзисторе, коллектор которого является выходом устройства, база первого транзистора соединена с выходом первого источника напряжения смещения, накопительный элемент на конденсаторе, одна из обкладок которого соединена с коллектором первого

10 транзистора, первый ключ на втором транзисторе, коллектор которого соединен с первой шиной питания, второй усилитель на третьем транзисторе, база которого является входом устройства и соединена с одним из выводов первого пассивного элемента на первом резисторе, коллектор третьего транзистора соединен с одним из выводов второго пассивного элемента на втором резисторе и с второй шиной питания, второй ключ на четвертом транзисторе коллектор которого

20 соединен с эмиттером третьего транзистора, с базой. второго транзистора и с анодом ограничительного диода, катод которого соединен с шиной напряжения ограничения, база четвертого транзистора соединена с шиной стробируюших импульсов, эмиттер четвертого транзистора соединен с эмиттером первого транзистора, отличающееся тем, что, с целью повышения точности устройства, в него введены третий усилитель на пятом трачзисторе, второй источник напряжения

Ç0 смещения и стабилизатор тока, вход которого соединен с первой шиной питания, выход стабилизатора тока соединен с эмиттером третьего транзистора, второй вывод первого резистора соединен с вторым выводом второго резистора, с другой обкладкой конденсатора и с эмиттером пятого транзистора, коллектор которого соединен с эмиттерами четвертого и первого транзисторов, база пятого транзистора соединена с выходом второго источника на40 пряжения смешения, вход которого соединен с второй шиной питания, эмиттер второго транзистора соединен с коллектором первого транзистора. (оставитель А. Воронин

Редактор М. Диткина Техред И. Верес Корректор С ч1ерни

Заказ 5238/53 Тираж 543 Подписное

ВНИИПИ ГO< j,а1)ственного когиитета СССР по делаги изобретений и открытий

113035, Москва, Ж 35, Рачшская наб., и 4Я

Филиал ППП «Пате!- |3, г Ужгород. ул Проектная,