Устройство для контроля блоков оперативной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для контроля блоков оперативной памяти. Целью изобретения является повышение надежности устройства . Устройство содержит генератор импульсов , формирователь эталонных сигналов, счетчики с первого по пятый, коммутаторы, блок сравнения и блок управления, задающий программы контроля тестами «Бегущие О и 1 или «Бегущие 1 и О. Устройство позволяет контролировать как ячейки памяти , относящиеся к одной БИС памяти, так и время выборки каждой БИС памяти, для чего в устройство введены четвертый и пятый счетчики, формирующие адрес БИС памяти , и второй коммутатор. 2 ил. IC о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3893305/24-24 (22) 25.04.85 (46) 30.09.86. Бюл. № 36 (72) В. П. Андреев, А. Н. Иванов и В. М. Романов (53) 681.327(088.8) (56) Авторское свидетельство СССР № 1003150, кл. G 11 С 29/00, 1981.

Авторское свидетельство СССР № 902077, кл. G 11 G 29/00, 1980. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ОПЕРАТИВНОЙ ПАМЯТИ

„„Я0„„1261014 А1 (57) Изобретение относится к вычислительной технике и предназначено для контроля блоков оперативной памяти. Целью изобретения является повышение надежности устройства. Устройство содержит генератор импульсов, формирователь эталонных сигналов, счетчики с первого по пятый, коммутаторы, блок сравнения и блок управления, задающий программы контроля тестами «Бегущие

0 и 1» или «Бегущие 1 и О». Устройство позволяет контролировать как ячейки памяти, относящиеся к одной БИС памяти, так и время выборки каждой БИС памяти, для чего в устройство введены четвертый и пятый счетчики, формирующие адрес БИС памяти, и второй коммутатор. 2 ил.

126)014 )

Изобретение относится к Вычисли (елькой технике и предназначено для контроля блоков оперативной памяти.

Целью изобретения является новы:пеH>г.=надежности устройства.

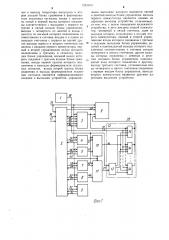

На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2 — функциональная схема блок» ун— ра вле ни я.

Устройство содержит (фиг. 1) ген ip»Top

1 импульсов, блок 2 управления, формирователь 3 эталонных сигналов, счетчики 4 --8 с первого по пятый, блок 9 сравнения, первый

10 и второй 11 коммутаторы. На фиг, Изооражен контролируемый блок 12 оперативной памяти с входящими в него дешифратором

13 и БИС 14 памяти.

На фиг. 1 обозначены вход 15 (1»чал!Июй установки, вход 16 пуска, вход 17 ост»1!ова устройства, выход 18 генератора !, выходы

19 и 20, вход 21, выходы 22 -24, вход 25, выход 26, вход 27, выход 28, вход 29, Выход

30, вход 31, выход 32, входы 33 и 34 блока 2 управления, информационный 35, адресные

36 и 37 выходы устройства, информационные входы 38 устройства, выходы 39 и 40 блока

2 управления, выходы 41---44 счетчиков 1> 5, 7 и 8 соответственно.

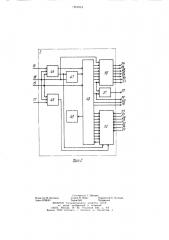

Блок 2 управления содержит ((pHI . 2) триггеры 45 и 46, элемент И 4, элсме-: г индикации 48, микропрограммный автомат (МПА) 49, формирователь 50 кмпу.ц сных сигналов управления, элемент И.г1И вЂ” НЕ 51, формирователь 52 сигнала выполнения условия перехода. На фиг. 2 показаны также инверсный и прямой выходы триггера 15. прямой выход триггера 46, вход М!1А 49. вход элемента индикации 48, Выходы сигналов управления MILA 49, выходы сиi Ilалов;:с ловий перехода MILA 49, Вход сиги»13 Выполнения условия перехода,IIA 49. ) состав блока 9 сравнения входят светодиоды, служащие для индикации резул;>татов срав нения.

Устройство работает следуюшим образам.

Установка устройства в исходное состояние осуществляется сигналом начальной установки по входу 15, который обнуляет с !ечики 4 — 8, а также устанавливает в нулевое состояние все триггеры блока 2, форм !рон,:-теля 3 и блока 9. Для запуска устр<эйс(в» по входу 16 подают сигнал запуска, и <)н начинает формировать сигналы, обеспечи вающие контроль блока оперативной памя ти тестами «Бегающие 0 и !», и «Бе! аюц ие

1 и 0». Так, в режиме записи в блок;- 2 формируloTcH cHOH»albl p33pLI«(c«IH>I Выб01> H и записи, поступающие соответственно вход 22 (сигнал разрешения выборки) и на вход 23 (сигнал записи-считывания). Формирователь 3 в этом режиме Вырабатыв; ет фоновое Ф (равное 0 или 1) клк тестовое число (равное 1 или О), которое поступает

Бхо Ihl ):) б."Ока ) 2. (3>«>(б )p <«>0««ового << -) или тестового 7 чксла асуп;сс-.вляется 0 сиг

H3, lV fl 3 В ХО,(<> 9, IIOCTV 13 Юп(см ь HH (рОрмк роват(.>(В 3; В«>! (<)д3

БИС. )4 фоэмируетс» с-((тчико.(4 кли 5. Код

:..Ii>cc3 с I>Ixo ц)(3 с етчиков 4 и 5 через комму"i атО! 10:IOO< у)(аст «. 3 БхОды 36, т.е.

l3 адресные Входы БИС 4. Выбор кода адреса с0 с !етчика -, клк <" етчика 4 осу!цестзляется сигналом Hd Бь(ходе 40. Адрес БИ)С

14 В блоке 12 формкруетсH -четчиком 7 и IH

8 1 ь бор кода ад<)с<3 со счетчика 7 кли 8 T»I<же;;"с>, цествляется сигналом на выходе с(. Сиг(!»л разрешения Быб01) ки с Выхода 22 посту (1 ает и 3 Входы комх(мтаторо«) 10 и !. KoT адреса H счетчике 6 и:<меняется всегда = :

Р»ЗНОСТИ КОДОВ »ДР=C» ld ВЫХОЗ(ах СЧЕТЧИКОВ

4! к 5 кли разности к< Дов адреса на Выходах счетчиков 7 и 8, т.с. Б счет (кке 6 отслежи2О в»ется выполнение услов«!я,, скг!(ал на Выходе 33 или на Выходе 34) пер хода ус,ройстВ» из одного: OcToHHHH I3;jpv(0(. (напри. !(. i), из сОстОя ни я cH:i i;! Ва ни я HVля (polio

Бого числа — Б сосT()HHI;с считывания тестового числа, равl формирователь 3 В э.гoM режиме 31 рабатыва$)0!(<)BO =i Ф Hi.»H IeCTOBO" Т t(HCло„ которое .!Остунает н» Входы блока н, на ,(!», ги(> Входы к(. TOpo! 0 с Б«»х<>дсгв,. 8 <>.!0Hi2 ! 2 поступал с . »1»HH:.)3 числа. На "!!равляюз(ий В<од блок; 9 I Oc (»ет с:!- ;H) )2 39

CH: (3Л, Р»З«)ЕШ» h) ЩИ и i Pавн(НИ- ЭТ3. Oi(НОга и считанно)0 !Нссл. !)езультагы cpaвнения и«<дкци рук)тся э. (e le:(т»..лк кн,(икацкH блока 9, Адрес ЛЗ В БИ)<.. 4 !i адрес самой

Б)1 -с. 14 форл! и,), < т(и В этОм режиме так же, 4!) K!10 Bhl ltl,l,.! Hi >(жк м» за (!Иск. CHHхранизация работы,(< Tpoй(.", Ва осуществля-=":ся импульсами тактoHOH час -„ -Thi с выхода !

8 .енератор» I.;Iл» О(-:-»нова; тройстБ»

:"од»ется cHI н»л: !» «3 ьхо. (17.

Ф<)(!З(,>.(С и300<>втЕИи.<<

У.гронство Л..(Я ко троля блоков операТКБНОй 1(3)КЯ ги, С<;Д(-:-Ржашсс бЛОК >, IIP»BËÅ> (> к я., 1 е>>е02тОр >) м i V.! Бсаг). (pорм к рОВd гель Т»;И !, (!ЫХ СКГНИ.>02, >.,< К СРВВНЕНКН,СЧЕТЧИкк ".. pi!oi(tiñ т>!c :.(й i 1;ео )ый к<;э(мутdп>р, i(:кч»х! .>CT;> !1 )><О (!! . - « » <> (Ы ><)pì lip .)Ва"е ">Я . -iiialOflflhiХ СИ Н »ЛО(> (» («Ч С>Т <(И КОН. !)ЕРВЫЕ ВХОi i>i i.! 0 H 3, ! I) ; Б л (> н 1 я и б. 0 к 2 c p 3 I н е н и я я d<>5 .-ЯЮ > СЯ ВХОДОМ (> акадi кои,:. . . 1:<>((КИ > СТl <>Hie Б2 БКО Iа ми llv и >:": < .1(03 < . .РHd, ((:..;.:Влснк ., Четн<.:). Tf>(II Б .: .(.:.0-0ро! О (;<)дкл:.а

1261014 чен к выходу генератора импульсов и вторым входам блока сравнения и формирователя эталонных сигналов, входы с третьего по пятый и первый выход которого соединены соответственно с выходами с первого по третий и пятый входом блока управления, выходы с четвертого по шестой и входы с шестого по восьмой которого пбдключены соответственно к счетным входам и к одним из выходов счетчиков с первого по третий другие выходы первого и второго счетчиков соединены с входами первого коммутатора, первый и второй управляющие входы которого подключены к третьему и седьмому выходам блока управления, восьмой выход которого соединен с третьим входом блока сравнения, входы первой группы которого подключены к выходам формирователя эталонных сигналов, входы второй группы блока сравнения и выходы формирователя эталонных сигналов являются информационными входами и выходами устройства, управляюшими выходами которого являются третий и девятый выходы блока управления, выходы первого коммутатора являются одними из адресных выходоь устройства, or,ø÷àþùååся тем, что, с целью повышения надежности устройства, в него введены второй коммутатор, четвертый и пятый счетчики, один из выходов которых подключены к входам второго коммутатора, первый и второй управляющие входы которого соединены с третьим и седьмым выходами блока управления, десятый и одиннадцатый выходы которого подключены соответственно к счетным входам четвертого и пятого счетчиков, другие выходы которых соединены с девятым и десятым входами блока управления, одиннадцатый вход которого подключен к другому выходу третьего счетчика, установочные вхо. ды четвертого и пятого счетчиков соединены с первым входом блока управления, выходы второго коммутатора являются другими адресными выходами устройства..уг

gn

Составитель Т. Зайцава

Редактор М. Циткина Тсхред И. Верес Корректор O. Луговая

Заказ 5238/53 Тираж 543 Подписное

ВН ИМЭПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4