Умножитель напряжения на мдп-транзисторах

Иллюстрации

Показать всеРеферат

Умножитель напряжения на МДП- транзисторах может быть использован при разработке источников электропитания интегральных схем. Цель изобретения - повышение функциональных возможностей путем повьшения коэффициента умножения, нагрузочной способности и упрогдение управления. Умножитель содержит п последовательно включенных каскадов умножения, состоящих из первых зарядных транзисторов (ЗТ) 1-1. и вторых ЗТ 2,-2 , Л л 1 Истоки 3X1 образуют входные выводы каскадов 3 -3 и через первые зарядные конденсаторы (ЗК) соединены с прямым входом блока управления (БУ) 5, вторые ЗК 7.,-7 - с инверсным входом управления 8. Введение форсирующих транзисторов 9, 10 и их включение позволяет заряжать форсирующие емкости 11 , 12. в момент напряжения низкого уровня на выходных шинах прямого и инверсного сигналов БУ 5 и препятствуют разряду этих емкостей в момент напряжения высокого уровня на выходных шинах прямого и инверсного сигналов БУ 5. Повышение напряжения на затворах ЗТ1 и ЗТ2 в момент подачи фазного напряжения на выходную шину прямого сигнала БУ 5 либо на выходную шину инверсного сигнала БУ 5 обеспечивает умножение напряжения. Устройство позволяет использовать проектирование схемы с одним источником питания. 1 ил. с 9 КчЭ Од

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (ply 4 Н 02 М 3/155

-=j

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

15 31 1 б Р Эг

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

RO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3758821/24-07 (22) 28.06.84 (46) 30.09.86. Бюл. У 36 (72) В.П. Сидоренко, Н.И. Хцынский, А.M. Прокопенко и В.А. Тальнова (53) 621.314.1(088.8) (56) IEEE Journal of Solid St, Cir.

Vol SC-18 1983, Р 5, Oct р. 532.

А,16 kbit. Smark 5V-Only EEPROM

with Redundancy.-IEEE Journal of

Solid St. Cir. Vol. SC-18, 1983, У 5, Oct., р. 539.

EEPROM adapts easily to in system

changes.-Electronic Design.1983, August, 18, 189. (54 ) УМНОЖИТЕЛЬ. НАПРЯЖЕНИЯ HA МДПТРАНЗИСТОРАХ (57) Умножитель напряжения на МДПтранзисторах может быть использован при разработке источников электропитания интегральных схем. Цель изобретения — повышение функциональных возможностей путем повьппения коэффициента умножения, нагруэочной способности и упрощение управления. Умножитель содержит и последовательно

„„SU„„ I 261064 А 1 включенных каскадов умножения, состоящих из первых зарядных транзисторов (ЗТ) 1 -1 и вторых ЗТ 2, -2

1 h 1 Ф\-1 °

Истоки ЗТ!„ образуют входные выводы каскадов 3 -3 и через первые заряди ные конденсаторы (ЗК) 4 -4 соедии иены с прямым входом блока управления (БУ) 5, вторые ЗК 7, -7„ — с инверсным входом управления 8. Введение форсирующих транзисторов 9 п

10, и их включение позволяет заряжать форсирующие емкости ll, 12„ в момент напряжения низкого уровня на выходных шинах прямого и инверсного сигналов БУ 5 и препятствуют разряду этих емкостей в момент напряжения высокого уровня на выходных шинах прямого и инверсного сигналов БУ 5. Повьппение напряжения на затворах ЗТ1 и ЗТ2 в момент подачи фаэного напряжения на выходную шину прямого сигнала БУ 5 либо на выходную шину инверсного сигнала БУ 5 обеспечивает умножение напряжения.

Устройство позволяет использовать проектирование схемы с одним источником питания. 1 ил.

Ж-У 1Г7-1 Юр 2 П 1 6 л 2а Q

3 г

1261064

Изобретение относится к электротехнике и может быть использовано при разработке источников электропитания интегральных схем, Цель изобретения — повышение функциональных возможностей путем повышения коэффициента умчожения, I нагрузочкой способности и упрощение управления.

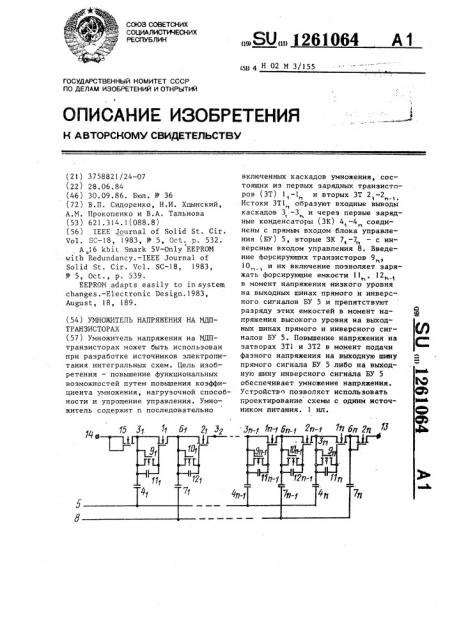

На чертеже показана принципиальная схема умножителя.

Умножитель содержит и последовательно включенных каскадов умножения, состоящих из первых 1 -1 и вторых

1 г

2„-2 зарядных транзисторов, при этом истоки первых из них образуют входные выводы каскадов 3, — 3„ и через первые зарядные конденсаторы 4,-4„ соединены с прямым входом 5 управления„ стоки первых и истоки вторых зарядных транзисторов объединены (точки 6,—

6 ) и через вторые зарядные конденсаторы 7, -7 соединены с инверсным ч входом 8 управления, причем истоки зарядных транзисторов, кроме второго зарядного транзистора п-го каскада„ соединены с затвором и истоком соответственно первых 9,-9„ и вторых

10„-10„ „ форсирующих транзисторов, между стоком и истоком каждого из которых подключены соответственно первые !1,, -11 „ и вторые 12„-12„, форсирующие конденсаторы, а истоки форсирующих транзисторов соединены с соответствующими затворами зарядных транзисторов, сток второго за- . рядного транзистора образует выход

13 каскада. Между входным выводом

14 умножителя и входом первого каскада включен первый нагруэочный транзистор 15, исток и затвор которого подключены к входному выводу.

Сток второго зарядного транзистора и-го каскада образует выходной вывод.

Умножитель напряжения на МДП-транзисторах работает следующим образом.

° На вход 14 подается напряжение питания, на входе 5 управления — напряжение низкого уровня, а на входе

8 управления — высокого. Первый нагрузочный транзистор 15 открывается, и первый зарядный конденсатор 4 первого каскада умножения заряжается до напряжения U. при этом на входе 1 первого каскада 3, будет напряжение

U. =U

1 ПЙ1 ПОР . -Р1 которое через

1

40 открытый первый форсирующий транзистор 9, передается на затвор первого зарядного транзистора II и происходит заряд первой форсирующей емкости

l1,.

Напряжение на входе первого каскада U, U„- U„ ð,p,, форсирующая емкость 11, заряжена, но напряжение недостаточно для открывания первого зарядного транзистора 1, .

На вход управления 5 поступает напряжение высокого уровня, а на вход 8 — низкого уровня. На входе

3, напряжение становится равным

U =U +П, (где U — напряжение сигнала высокого уровня), и через форсирующую емкость Il теперь к затвору первого зарядного транзистора 1, прикладывается напряжение, достаточное для открывания первого зарядного транзистора 1, и передачи напряжения с входа 3, в точку 6,. При этом происходит заряд второго зарядного конденсатора 7, В точке 6,. будет

Р напряжение U =U„+U, через открытый форсирующий транзистор 10, напряжение U передается на затвор второго зарядного транзистора 2,, происходит заряд второго форсирующего конденсатора 12,, но напряжение недостаточно о для открывания второго зарядного транзистора 2

С приходом на вход 8 напряжения высокого уровня второй зарядный транзистор открывается, и напряжение точки 61„ равное U =U +U, передается на выход каскада 13, становится

paBHbM из =Уа+ 1р, или U3 =U, +2Uv, и и

U =U« -U +2U и заряжает первую зарядную емкость следующего каскада.

Таким образом, напряжение с входа

14, т.е. U„„, пройдя первый каскад умножения, увепичивается, т.е. на выходе 3 напряжение равно U (причем U 11„„ ) и т.д., после и каскадов умножения на выходе 6„ „ будет напряжение П„ > заряжается зарядный конденсатор 4„, и через открытый форсирующий транзистор 9 происходит заряд форсирующей емкости ll„ с приходом на вход 5 напряжения высокого уровня. Через открытые 1„ и

2„ зарядные транзисторы и-го каскада напряжение на выходе 13 передается на выход умножителя напряжения, в момент, когда на входе 8 присутствует напряжение высокого уровня, на

1 61064

Формула изобретения

Составитель И. Никитин

Редактор Л. Веселовская Техред Л.Олейник

Корректор А. Тяско.

Заказ 5241/55 Тираж 631

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 выходе умножителя напряжения происходит подкачка заряда, т.е. U +U Рн

Применение изобретения позволяет комгенсировать влияние напряжения смещения подложки, 5

Умножитель напряжения на ИДП-транзисторах, содержащий первый нагрузоч- 1б ный транзистор, исток которого подключен к выходному выводу, а сток— к входу умножителя напряжения, состоящему из п последовательно включенных каскадов умножения напряжения, каждый из которых состоит из первого и второго зарядных транзисторов, при этом исток первого из них образует входной вывод каскада и через первый зарядный конденсатор соединен с прямым входом управления, сток первого и исток второго объединены и через второй зарядный конденсатор подключены к инверсному входу. управления

t а сток - второго образует выходной вывод каскада, причем исток каждого иэ зарядных транзисторов, кроме второго зарядного транзистора п-го каскада, соединен с истоком форсирующего транзистора, а затвор — со стоком последнего, о т л и ч а io щ и йс я тем, что, с целью упрощения управления и расширения функциональных возможностей путем повышения коэффициента умножения каждого каскада и нагрузочной способности, в него введены форсирующие конденсаторы, включенные между истоком и стоком форсирующих транзисторов, причем затворы первого нагрузочного транзистора, всех форсирующих транзисторов и второго зарядного транзистора n-ro каскада подключены соответственно к своим истокам, а сток последнего образует выходной вывод устройс rва.