Цифровой накопитель (его варианты)

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в частотопрёобразующих узлах аппаратуры времени и эталонных частот измерительной и вычислительной техники. Цель изобретения - повьшение точности за счет стабилизации фазы. В изобретении представлены два варианта вьтолнения устройства. Устройство по первому варианту содержит сумматоры 1 и 3, мультиплексоры 2 и-10, регистры 4, 5 и 6, вход 7 устройства, вход 8 цифрового накопителя, тактовый вход 9 устрой - ства, выход 11 устройства и злемент ; 12 задержки. В устройстве по второму варианту введен делитель 13 частоты с управляемым коэффициентом деления , совмещакяций функщш мультиплексора 10 и элемента 12 задержки. С использованием элемента задержки и мультиплексора 10 либо делителя частоты 13 с управляемым коэффициентом деления фазовые ошибки на выходе 11 накопителя становятся существенно меньше первоначальных ошибок, характерных для импульсов переноса сумматора 3. Таким образом, методическая погрешность устройства, обусловленная дискретностью накопителя, оказывается компенсированной. Резуль тирующая стабильность фазы выходных импульсов определяется стабильностью задержки. 2 с.п. ф-лы. 2 ил. I с 7 о 13

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SV» 1261111

А2 сЮ 4 Н 03 К 23 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ФЬа!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 1162040 (21) 3807769/24-21 (22) 05. 11.84 (46) 30.09.86. Бюл. Ф 36 (72) В.С. Станков и С.Я. Шишов (53) 621.374.32(088.8) (56) Авторское свидетельство СССР

1162040, кл. Н 03 К 23/00, 1983. (54) ЦИФРОВОЙ НАКОПИТЕЛЬ (ЕГО ВАРИАНТЫ). (57) Изобретение может быть использовано в частотопреобразующих узлах аппаратуры времени и эталонных частот измерительной и вычислительной техники. Цель изобретения — повышение точности эа счет стабилизации фазы. В изобретении представлены два варианта выполнения устройства.

Устройство по первому варианту со" держит сумматоры 1 и 3, мультиплексоры 2 и .10, регистры 4, 5 и 6:, вход 7 устройства, вход 8 цифрового накопителя, тактовый вход 9 устрой ства, выход 11 устройства и элемент

12 задержки. В устройстве по второму

I варианту введен делитель 13 частоты с управляемым коэффициентом деления, совмещающий функции мультиплексора 10 и элемента 12 задержки. С использованием элемента задержки и мультиплексора 10 либо делителя частоты 13 с управляемым коэффициентом деления фазовые ошибки на выходе 11 накопителя становятся существенно меньше первоначальных ошибок, характерных для импульсов переноса сумматора 3. Таким образом, методическая погрешность устройства, обусловленная дискретностью накопителя, оказывается компенсированной. Резуль тирующая стабильность фазы выходных импульсов определяется стабильностью задержки. 2 с.п. ф-лы. 2 ил.

1261111

Изобретение (его варианты) относится к импульсной технике и может быть использовано в частотопреобразующих узлах аппаратуры времени и эталонных частот измерительной и вычислительной техники, в устроиствах синхронизации систем передачи данных, преимущественно при наиболее высоких требованиях к стабильности фазы выходных импульсов.

Цель изобретения (его вариантов) — повышение точности путем стабилизации фазы.

Поставленная цель достигается в обоих вариантах путем учета остатка в первом регистре, свидетельству

Ющего о наличии временной погрешности.

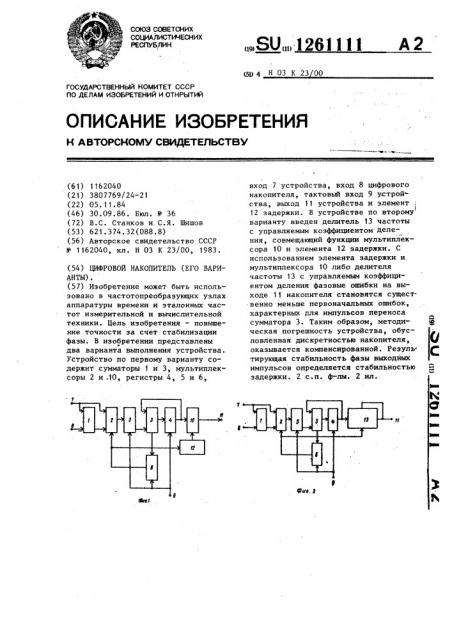

На фиг. 1 показана структурная схема цифрового накопителя согласно первому варианту, на фиг. 2 — структурная схема цифрового накопителя согласно второму варианту.

Цифровой накопитель (фиг. 1) содержит первый сумматор 1, мультиплексор 2, второй сумматор 3, пер вый 4, второй 5 и третий 6 регистры.

Первый вход 7 устройства соединен с первыми входами первого сумматора

1 и с первыми информационными входами мультиплексора 2, вторые информационные входы которого соединены с выходами первого сумматора 1, вторые входы которого соединены с вторыми входами 8 цифрового накопителя. Выходы мультиплексора 2 соединены с входами второго регистра 5, выходы которого соединены с первыми входами второго сумматора 3, выходы которого соединены с входами первого регистра 4, выходы которого соединены с вторыми входами второго сумматора 3,. выход переноса которого соединен с входом третьего регистра 6. Выход последнего соединен с адресным входом мультиплексора 2, а тактовый вход 9 устройства соединен с тактовыми входами регистров 4-6. Выход дополнительного мультиплексора 10 является выходом 11 устройства, адресные входы дополнительного мульти-.. плексора 10 соединены с выходами первого регистра 4, информационные входы дополнительного мультиплексора 10 соединены с выходами элемента 12 задержки, вход которого соединен с выходом третьего регистра 6,.

I0

t5

Цифровой накопитель (фиг. 2) содержит первый сумматор 1, мультиплексор 2, второй сумматор 3, первый 4, второй 5 и третий 6 регистры.

Первый вход 7 устройства соединен с первыми входами первого сумматора

1 и с первыми информационными входами мультиплексора 2, вторые информационные входы которого соединены с выходами первого сумматора 1, вторые входы которого соединены с вторыми входами 8 цифрового накопителя.

Выходы мультиплексора 2 соединены с входами второго регистра 5, выходы которого соединены с первыми входами второго сумматора 3, выходы которого соединены с входами первого регистра 4, выходы которого соединены с вторыми входами второго сумматора 3. Выход переноса последнего соединен с входом третьего регистра

6, выход которого соединен с адресным входом мультиплексора 2, а так— товый вход 9 устройства соединен с тактовыми входами регистров 4-6..

Выход делителя 13 частоты с управляемым коэффициентом деления является выходом 11 цифрового накопителя и соединен с входом сброса делителя

13 частоты с управляемым коэффициентом деления, информационные входы и тактовый вход которого соединены соответственно с выходами первого

4 и третьего 6 регистров.

Устройство согласно первому варианту работает следующим образом.

Сумматор 1 суммирует входной код

К, поступающий с входа 7 с входным кодом М управления емкостью, поступающим с входа 8. На выходе сумматора 1 образуется код К+М. Таким образом, на первые и вторые информационные входы мультиплексора 2 непрерывно поступают соответственно код К и код К+И.

Пока сигнал переноса сумматора 3 равен нулю, на управляющий вход мультиплексора в каждый такт работы накопителя поступает нулевой сигнал и на выход мультиплексора пропускается код К, который по тактовым импульсам записывается в регистр 5.

Код К суммируется в сумматоре 3 с выходным кодом регистра 4, код суммы подается на вход регистра 4 и следующим тактовым импульсом записы-. вается в регистр 4. Когда в одном из тактов работы накопитель пере1261111 полняется, т. е. значение суммы на выходе сумматора 3 достигает или превышает величину емкости R накопителя, в сумматоре 3 образуется остаток, а на выходе 1 1 — сигнал 5 переноса, равный логической "1". В следующий такт работы накопителя в регистр 6 записывается единица переноса, в регистр 5 — код К, в регистр 4 — остаток сумматора 3, на 10 выход мультиплексора 2 пропускается код K+M, на выходе сумматора получается код K+L,à сигнал переноса на выходе 11 становится равным логическому 01 . В следующем такте ра- 15 боты накопителя в регистр 6 записывается ноль с выхода переноса сумматора 3, в регистр 5 — код K+M, в регистр 4 — код K1+L, на выход мультиплексора 2 вновь пропускается 20 код К, на выходе сумматора получается код 2K+M+L, и начинается новый цикл работы накопителя, в котором емкость равна R-M. Остаток L в регистре 4 (остаток с выхода суммато- 25 ра 3 в момент его переполнения) в общем случае не равен нулю. Отличие

L от нуля указывает на то, что импульс на выходе регистра 6 (импульс переполнения накопителя) формируется с некоторой временной погрешностью лежащей в интервале от 0 до Т (где Т вЂ” период тактового сигнала), которая является следствием дискрет-! ного накопления кода К.

Поскольку занесение числа К в сумматор 3 происходит импульсами с периодом Т, то любая доля числа К=Т соответствует такой же доле времени Т . Если числа К и M выразить с использованием одних и тех же единиц времени, а квант задержки выбрать равным весу младшего разряда этих чисел, то остаток L всегда соответствует интегральному запаздыванию 45 импульса переполнения относительно соответствующего по номеру импульса идеальной последовательности. Выходные импульсы переполнения с регистра 6 поступают на вход многоотводного элемента 12 задержки. В результате задержки положение импульсов на выходе мультиплексора 10 оказывается более близким к идеальной импульсной последовательности.

Функции элемента задержки 12 и мультиплексора 10 могут быть совмещены в делителе 13 частоты с управляемым коэффициентом деления (см. фиг 2). Тактовые импульсы с частотой Q/Т проходят на вход делителя 13 лишь при поступлении на него очередного импульса с регистра

6. Коэффициент деления определяется кодом, поступающим с регистра 4.

При коде 00,...,0 коэффициент деления максимален, при коде 11,..., 1 коэффициент деления равен единице.

Импульсы, прошедшие на выход делителя 13, поступают на вход установки нуля делителя. Таким образом, до прихода следующего импульса с выхода регистра 6 делитель снова оказывается отключенным.

В результате применения элемента

12 задержки совместно с мультиплексором 10 или делигеля 13 частоты, с управляемым коэффициентом деления фазовые ошибки на выходе 11 накопи-. теля становятся меньше первоначальных ошибок, характерных для импульсов переноса сумматора 3. Таким образом, методическая погрешность устройства, обусловленная дискретностью накопителя, оказывается компенсированной, а результирующая стабильность фазы выходных импульсов определяется стабильностью задержки. формула изобретения

1. Цифровой накопитель, по авт. св. N 1162040, о т л и ч а юшийся тем, что, с целью повышения точности за счет стабилизации фазы выходных импульсов, в него дополнительно введены элемент задержки и дополнительный мультиплексор, выход которого является выходом устройства, адресные входы дополнительного мультиплексора соединены с выходами первого регистра, информационные входы дополнительного мультиплексора соединены с выходами элемента задержки, вход которого соединен с выходом третьего регистра.

2. Цифровой накопитель по авт.св. У 1162б40, о т л и ч а юшийся тем, что, с целью повышения точности за счет стабилизации фазы выходных импульсов, в него дополнительно введен делитель частоты с управляемым коэффициентом деления, выход которого является выходом цифрового накопителя и соединен с входом сброса делителя частоты

1261111

Составитель О.Скворцов

Техред И.Попович

Редактор С.Лисина

Корректор Е.Сирохман

Тираж 816 .Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5245/58

Производственно-полиграфическое предприятие, г. ужгород, ул. Проектная,4 с управляемыми коэффициентами деления, информационные входы и тактовый вход которого соединены соответственно с выходами первого и третьего регистров.