Датчик телеграфного кода

Иллюстрации

Показать всеРеферат

Изобретение .относится к технике связи. Расширяется диапазон формируемых кодовых комбинаций. Датчик содержит блок ввода сигналов 1, формирователь пусковых сигналов 2, мультиплексор 3, коммутатор (К) 4, блок установки команд (БУК) 5, два блока совпадения 6 и 9, адресный блок (АВ) 7, элемент запрета 8, оперативный запоминающий блок 10 и формирователь кода 11. Цель достигается введением К 4 АБ 7, блока совпадения 9 мультиплексора 3, преобразующего параллельный код в последовательный, и БУК 5, отрабатьшающего полный цикл.команд при осуществлении считывания и записи разрядов кода знака для выбранного столбца. Отличием датчика является также выполнение К 4, БУК 5 и АБ 7, даны иллюстрации примеров их выполнения. 3 з.п. ф-лы, 4 ил. о S О) ND KJ

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК дц 4 Н 04 L 15/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H Д BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2 1) 3884030/24-09 (22) 12.04.85 (46) 30.09.86. Бюл. ¹ 36 (72) А.А. Семенов, М.И. Катин, А.И. Пенязь и Л.С. Гендельман (53) 621.394.61(088.8) (56) Авторское свидетельство СССР

¹ 1001496, кл. Н 04 L 15/04, 1981. (54) ДАТЧИК ТЕЛЕГРАФНОГО КОДА. (57) Изобретение .относится к технике связи. Расширяется диапазон формируемых кодовых комбинаций. Датчик содержит блок ввода сигналов 1, формирователь пусковых сигналов 2, мультиглексор 3, коммутатор (К) 4, блок

„„SU„, 1261127 А1 установки команд (БУК) 5, два блока совпадения 6 и 9, адресный блок (АБ) 7, элемент запрета 8, оперативный запоминающий блок 10 и формирователь кода 11. Цель достигается введением К 4 АБ 7, блока совпадения

9 мультиплексора 3, преобразующего параллельный код в последовательный, и БУК 5, отрабатывающего полный цикл .команд при осуществлении считывания и записи разрядов кода знака для выбранного столбца. Отличием датчика является также выполнение

К 4, БУК 5 и АБ 7, даны иллюстрации примеров их выполнения. 3 э.п. ф-лы, 4 ил.

1261127

Изобретение относится к технике связи и может использоваться для построения датчиков телеграфных кодов, в частности датчиков кода Морзе.

Цель изобретения — расширение диапазона формируемых кодовых комбинаций.

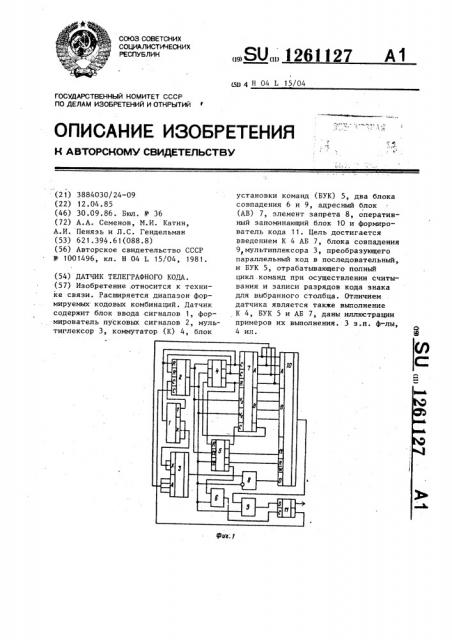

На фиг. 1 представлена структурная электрическая схема предлагаемого датчика, на фиг. 2 — коммутатор, вариант выполнения на фиг. 3— блок установки команд, вариант выполнения," на фиг. 4 — адресный блок, вариант выполнения.

Датчик телеграфного кода содержит (фиг. 1) блок 1 ввода сигналов, формирователь 2 пусковых сигналов, мультиплексор 3, коммутатор 4, блок

5 установки команд, первый блок 6 совпадения, адресный блок 7, элемент

8 запрета, второй блок 9 совпадения, оперативный запоминающий блок 10, формирователь 11 кода. Коммутатор 4 содержит (фиг. 2) два блока 12 и 13 совпадения, два элемента 14 и 15 задержки и собирательный блок 16.

Блок 5 установки команд содержит (фиг. 3) три собирательных элемента

17-19, генератор 20 и распределитель 21. Адресный бяок 7 содержит (фиг. 4) три счетчика 22-24, элемент

25 совпадения и мультиплексор 26.

Датчик телеграфного кода работает следующим образом.

Блок 1 ввода сигналов на первом выходе (фиг. 1) вырабатывает сиг- . нал Пуск записи, который поступает на третий вход пуска записи формирователя 2 пусковых сигналов ° Одновременно с этим на других выходах блока 1 ввода сигналов появляется двоичный промежуточный код в параллельной форме, который соответствует введенному знаку. Этот код поступает на сигнальные входы мультиплексора 3 (преобразователя параллельного кода в последовательный) и фиксируется на нем в течение всего времени записи. Время записи определяется формирователем 2 пусковых сигналов. На первом выходе формирователя 2 пусковых сигналов появляется сигнал "Установка записи", который держится на нем в течение времени, которое необходимо для записи кода из блока 1 ввода сигналов в оперативный запоминающий блок 10.

При этом сигнал "Установка записи"

f0

35 с второго выхода формирователя 2 пусковых сигналов параллельно поступает на первый вход коммутатора 4, блок 12 совпадения, четвертый вход управления записью адресного блока

7 (счетчик 2?) и второй вход установки записи блока 5 установки команд, собирательный элемент 17.

В исходном состоянии на первой группе выходов адресного блока 7 (счетчик 22) имеется код адреса записи первого разряда строки (фиг. 4) устанавливающийся по цепи сброса в момент включения датчика и поступающий параллельно на адресный вход строк оперативного запоминающего блока (ОЗУ)10 и на управляющие входы мультиплексора 3. Чультиплексор 3, преобразующий параллельный код в последовательный, пропускает в этом случае на свой выход только первый разряд параллельного кода, который поступает на его входы от блока 1 ввода сигналов. Одновременно блок

5 установки команд (фиг. 3) вырабатывает на своем третьем выходе, на выходе собирательного элемента

19 сигнал команды "Запись", а на втором выходе, на выходе собиратель. ного элемента 18, — сигнал команды

"Выбор кристалла". В момент формиро вания сигнала команды "Выбор кристалла осуществляется запись первого элемента параллельного кода знака в ОЗУ 10 по установленному адресу, т.е. в первую ячейку первой строки первого столбца.

На второй группе выходов адресного блока 7 на выходе мультиплексора

26 имеется код записи адреса первого столбца. Этот код на второй группе выходов адресного блока 7 держится в течение всего времени записи первого знака, вводимого в ОЗУ 10 в поле первой строки. После записи первого разряда кода знака в ОЗУ 10 на первом выходе блока 5 установки команд формируется сигнал, который поступает на установочный шестой вход, адресного блока 7 (тактовый вход счетчика 22). По этому сигналу на выходах адресного блока 7 появляется новый код адреса второй строки. Этот код обеспечивает прохождение в ОЗУ 10 через мультиплексор 3 второго разряда кода знака так же, как указывалось. На информационный

1261127

15

20 вход ОЗУ 10 элементы кода знака поступают через элемент 8 запрета.

Код адреса записи выбранного столбца остается неизменным,а блок

5 установки команд, как указывалось, отрабатывает полный цикл команд, задаваемый генератором 20 (фиг. 3) для записи второго разряда кода знака. Этот процесс продолжается до тех пор, пока не записываются все строчные разряды кода знака для выбранного столбца записи. После записи каждого разряда кода знака счетчик 22 адресного блока 7 и распределитель 21 блока 5 установки команд приводятся в исходное состояние по сигналу третьего выхода коммутатора 4 выходу собирательного блока 16 (фиг. 2). По окончании за— писи всех разрядов кода первого вводимого знака в адресном блоке ? счетчик 23 сигналом с первого выхода коммутатора 4 с выхода элемента

14 задержки устанавливается в состояние, при котором на второй группе выходов адресного блока 7 устанавливается адрес второго столбца записи. Этим же сигналом приводится в исходное состояние цепь пуска записи формирователя 2 блока 1. 30

Сигнал с третьего выхода коммутатора 4 соответствует установке адреса (и+1) строки адресного блока 7, т.е. полному окончанию записи вводимого кода знака. В результате уста- З5 новки адреса (и+1) строки на девятом выходе адресного блока 7 появляется сигнал, который поступает на третий вход коммутатора 4. Этот сигнал, пройдя блоки 12 и 13 совпадения, два элемента 14 и 15 задержки и собирательный блок 16 с его первого выхода коммутатора 4 устанавливает новый адрес столбца записи (в данном случае — второй) и.приво- 45 дит сигналом со своего третьего выхода и исходное состояние счетчик

22 адресного блока 7 и таким образом подготавливает ОЗУ 10 к примеру первого разряда кода нового знака. 50

При поступлении из блока 1 ввода сигналов кода второго знака указанный процесс записи новой строки кода повторяется. В момент записи сигналы с выхода блока ОЗУ 10 отсутствуют,55 так как второй блок 9 совпадения заперт. Этот процесс может длиться до полного заполнения ОЗУ 10. Форми-1 рователь 11 кода тем временем формирует на первом выходе знак кода, введенный ранее.

Процесс считывания знака из ОЗУ 10 производится следующим образом.

После окончания формирования предыдущего знака на выходе датчика с второго выхода формирователя 11 появляется сигнал Пуск считывания", который подается на четвертый вход формирователя 2 пусковых сигналов.

В случае одновременного прихода сигналов Пуск записи" и "Пуск считывания" формирователь 2 пусковых сигналов запоминает оба эти сигнала и обеспечивает приоритет сигнала

"Пуск считывания" во избежание нарушения интервала между знаками, которые выдаются формирователем 11 кода.

Сигнал "Установка считывания" с второго выхода формирователя 2 пусковых сигналов параллельно поступает на второй вход коммутатора 4, пятый вход адресного блока 7, третий вход блока 5 установки команд, вторые входы первого и второго блоков 6 и 9 совпадения и элемента

8 запрета.

В исходном состоянии на второй группе выходов адресного блока 7 имеется код адреса считывания первой строки записанного ранее первого знака. Этот код адреса считывания первой строки первого знака, ранее записанного в ОЗУ 10, поступает параллельно на его адресный вход строк. Выход мультиплексора 3 при этом блокируется элементом 8 запрета. Одновременно блок 5 установки команд вырабатывает на своем третьем. выходе сигнал команды "Считывание", а на втором выходе сигнал команды

"Выбор кристалла", команда "Выбор кристалла" обеспечивает момент считывания информации из ячейки памяти по установленному адресу. На второй группе выходов адресного блока 7 имеется код считывания адресов первого столбца. Этот код на выходе

1 адресного блока 7 держится в течение всего времени считывания кода ранее записанного первого знака.

Итак, в начальной стадии считывания на выходе ОЗУ 10 появляется считываемый сигнал, соответствующий первому разряду первой строки считывания. Кодовые сигналы, поступающие с выхода ОЗУ 10, в соответствии

12611 27 с порядком считывания разрядов кода через второй блок 9 совпадения последовательно передадутся н формирователь 11 кода. Ввод знаков в формирователь 11 кода синхронизируется сигналами с четвертого выхода блока 5 установки команд через первый блок 6 совпадения. После считывания первого разряда кода знака из ОЗУ 10 на первом выходе блока 5 формируется сигнал, который поступает на установочный (шестой) вход адресного блока 7 (первый вход счетчика 22). По этому сигналу на выходах адресного блока 7 на выходах счетчика 22 и мультиплексора 26 появляется код адреса второго разряда первой считываемой строки. Этот код обеспечивает выход из ОЗУ 10 второго разряда кода знака.

Код адреса выбранного столбца считывания остается неизменным, а блок 5 установки команд одновременно отрабатывает цикл команд для считывания второго разряда кода знака. Этот процесс продолжается до тех пор, пока не считываются все строчные разряды кода знака для выбранного столбца считывания. После считывания каждого разряда кода знака счетчик 22 адресного блока 7 и блок 5 установки команд приводятся в исходное состояние как и при уже уКазанном процессе записи.

По окончании считывания всех разрядов кода первого считываемого из ОЗУ 10 знака на втором входе адресного блока 7 появляется сигнал с второго выхода коммутатора ч. При этом на второй группе выходов адресного блока 7 устанавливается адрес второго столбца считывания. Таким образом, ОЗУ 10 подготавливатся для считывания второго знака. При поступлении от формирователя 11 кода очередного сигнала пуска считывания, который появляется после окончания формирования предыдущего знака, указанный процесс считывания повторяется. В момент считывания сигналы с выхода ОЗУ 10 поступают на информационный вход формирователя 11 кода.

Формирователь 11 в свою очередь формирует необходимый код (например, код Морзе или MTK 2 в зависимости от конкретного исполнения ОЗУ 10),который с его выхода поступает в манипуля— ционную линию передающего устройства.

1О

f5

Формула изобретения

1. Датчик телеграфного кода, содержащий блок ввода сигналов, вход и сигнальный выход которого соединены соответственно с первым и третьим входами формирователя пусковых сигналов, четвертый вход и первый выход которого соединены соответственно с выходом формирователя кода и с вторым входом первого блока совпадения, а также оперативный запоминающий блок и элемент запрета, отличающийся тем, что, с целью расширения диапазона формируемых кодовых комбинаций, в него введены коммутатор, адресный блок, блок установки команд, мультиплексор и второй блок совпадения, первый вход и выход которого соединены соответственно с выходом оперативного запоминающего блока и с первым входом формирователя кода, к второму входу которого подключены выход первого блока совпадения, второй вход которого соединен с вторым входом второго блока совпадения, с вторым входом элемента запрета, к первому входу которого подключен выход мультиплексора, с третьим входом блока установки команд, с пятым входом адресного блока, сигнальные выходы которого подключены к адресным входам оперативного запоминающего блока, и с вторым входом коммутатора, к первому входу которого подключен второй выход формирователя пусковых сигналов, первый вход которого соединен с первым входом адресного блока, соответствующие сигнальные выходы которого подключены к управляющим входам мультиплексора, и с первым выходом коммутатора, второй выход которого подключен к второму входу адресного блока, третий вход которого соединен с третьим выходом коммутатора, к третьему входу которого подключены синхронизационный выход адресного блока, и с первым входом блока установки команд, второй вход которого соединен с вторым выходом формирователя пусковых сигналов и с четвертым входом адресно1 T го блока, к шестому входу которого подключен первый выход блока установки команд, второй и третий выходы которого соединены с командными входами оперативного запоминающе1261127 го блока, к информационному входу которого. подключен выход элемента запрета, четвертый выход блока установки команд подключен к первому входу первого блока совпадения, при этом кодовые выходы блока ввода сигналов соединены с информационны— ми входами мультиплексора.

2. Датчик по и. 1, о т л и— ч а ю шийся тем, что коммутатор содержит два элемента задержки, два блока совпадения и собирательный блок, к входам которого подключены выходы элементов задержки, к входам которых подключены выходы блоков совпадения, вторые входы которых объединены, при этом первые входы первого и второго блоков совпадения являются соответственно первым и вторым входами коммутатора, третьим входом, первым, вторым и третьим выходами которого являются соответственно второй вход первого блока совпадения, выход первого элемента задержки, выход второго элемента задержки и выход собиратель. ного блока °

3. Датчик по п. 1, о т л и ч а— ю шийся тем, что блок установки команд содержит распределитель, три собирательных элемента и генератор, выход которого подключен к третьему входу распределителя, второй вход которого соединен с выходом первого собирательного элемента, при этом первыи вход распределите ля и входы первого собирательного элемента являются соответственно первым, вторым и третьим входами

5 блока установки команд, первым, вторым, третьим и четвертым выходами которого являются соответственного один выход распределителя, выходы второго и третьего собирательных элементов, к входам которых подключены другие выходы распределителя, и соответствующий вход второго собирательного элемента.

4. Датчик по п. 1, о т л и— ч а ю щ и Й с я тем, что адресный блок содержит три счетчика, элемент совпадения и мультиплексор, к одним входам которого подключены выходы второго и третьего счетчиков, пеРвые входы которых объединены, а входы элемента совпадения соединены с вторым входом и с соответствующими выходами первого счетчика, при этом второй вход второго счетчика, второй вход третьего счетчика, первый вход первого счетчика, другие входы мультиплексора и второй вход первого счетчика являются соответственно первым, вторым, третьим, четвертым, пятым и шестым входами адресного блока, сигнальными выходами которого являются выходы первого счетчика и выходы мультиплексора, причем выход элемента совпадения является

35 синхронизационным BblxopoM адресного блока.

l 26! l 27

Составитель A. Москевич

Текред И.Попович

Редактор С.Лисина

Корректор А.Знмокосов

Заказ 5246/58

Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4