Приемник фазоманипулированных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике бвязи. Повышается достоверность приеМа при рэлеевских замиранияхо Устр-во содержит блок фазовой автоподстройки частоты (ФАПЧ) I, два блока автоматической регулировки усиления (ЛРУ) 2 и 3 и блок выделения информации (БВИ) 4. Входной сигнал поступает на 1-ые входы блока ФАПЧ 1, двух блоков АРУ 2 и 3 и БВИ 4. Сглаженное напряжение с выхода блока ФАПЧ 1 подается на 2-ые входы блоков АРУ 2.и 3 и БВИ 4. В блоках АРУ 2 и 3 осуществляется формирование сигналов . управления для блока ФАПЧ 1, по управляющему сигналу с выхода которого БВИ 4 осуществляет преобразование входного сигнала для ввделения из него информационных параметров. Цель достигается введением двух блоков АРУ 2 и 3. Даны примеры выполйения блока ФАПЧ 1, блоков АРУ 2 и 3 и БВИ 4. 3 з.п. ф-лы, 4 ил. (Л с N9 Ф СО 00

соки советских со1,!ИАлистичесних щспуьлин

А1

„„SU„, 12611

yg 4 Н 04 ? 27/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCHQMV СВИДЕТЕЛЬСТВУ

h4

Cb госудАрственнмй номитет ссср пО дЕлам изо1-ретений иотнрытий (2!) 3897628/24-09 (22) 20.05.85 (46) 30.09.86. Бюл. И 36 (72) В. В. Горшков и И. В. Леденев (53) 621.394.62(088.8) (56) Тузов Г. И. Статистическая теория приема сложных сигналов. М.: Советское Радио, 1977, с. 205. (54) IIPHEMHHK ФАЗОИАНИПУЛИРОВАННЫХ

СИГНАЛОВ (57) Изобретение относится к технике связи. Повышается достоверность приема при рзлеевскнх замираниях. Устр-во содержит блок фазовой автоподстройки частоты (ФАПЧ) 1, два блока автоматической регулировки усиления (АРУ) 2 и 3 и блок выделения информации (БВИ)

4. Входной сигнал поступает на 1-ые входы блока ФАПЧ 1, двух блоков АРУ

2 и 3 и БВИ 4. Сглаженное напряжение с выхода блока ФАПЧ 1 подается на

2-ые входы блоков АРУ 2 и 3 и БВИ 4.

B блоках АРУ 2 и 3 осуществляется формирование сигналов, управления для блока ФАПЧ 1, по управляющему сигналу с выхода которого

БВИ 4 осуществляет преобразование входного сигнала для выделения из него информационных параметров. Цель достигается введением двух блоков

АРУ 2 и 3. Даны примеры выполнения блока ФАПЧ 1, блоков АРУ 2 и 3 и

БВИ 4. 3 з.п. ф-лы, 4 ил.

1261138

Изобретение относится к технике связи и может использоваться для приема сигналов в системах передачи информации по радиоканалам.

Цель изобретения — повьппение достоверности приема при рэлеевских замираниях.

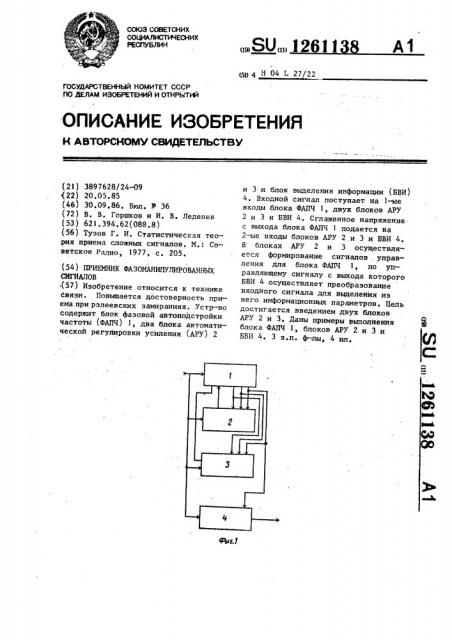

На фиг. 1 представлена структурная электрическая схема предложенного приемника, на фиг. 2 — вариант выполнения блока фазовой автоподстройки частоты; на фиг. 3 — - вариант выполнения блока автоматической регулировки усиления, на фиг. 4 — вариант выполнения блока вьделения информации °

Приемник фазоманипулированных сигналов (фиг. 1) содержит блок 1 фа зовой автоподстройки частоты, два блока 2 и 3 автоматической регулировки усиления, блок 4 вьщеления информации.

Блок 1 фазовой автоподстройки частоты (фиг. 2) содержит опорный генератор 5, первый, второй, третий, четвертый и пятый перемножители 6-10, первый и второй интеграторы, 11 и 12 первый и второй фазовращатели 13 и

1.4, первый и второй линейные фильтры

15 и 16,первый и второй сумматоры 17 и 18, фазовый модулятор 19, нелинейный эчемент 20.

Блоки 5 и 6 автоматической регулировки усиления (фиг. 3) содержат пер(л вый, второй, третий и четвертый перемножители 21-24, линейный фильтр 25, первый и второй сумматоры 26 и 27, формирователь 28 опорной амплитуды.

Блок 4 вьделения информации (фиг. 4) содержит первый и второй перемножнтели 29 и 30, первый и второй и третий сумматоры 31-33, интегратор 34, фазовращатель 35, усилитель 36, ограничитель 37, квадратор 38.

Приемник работает следующим образом.

Принимаемый сигнал поступает на вход блока 1 в виде

S(t) = А() cos(M t 1 Ц л + e) ()

+ В() з п (u,С +(+ + 9 ) (1) где A(t) и B(t) — огибающие квадратурных составляющих; (л, — частота сигнала, . - случайная составляющая за счет нестабильности опорного генератора 5;

) — случайная составляющая за счет влияния канала;

9 — параметр модуляции.

При этом, как следует из анализа

5 экспериментальных данных, входящие в выражение (1) случайные величины А, В,(,), подлежащие оценке, подчиняются следующим стохастическим дифференциальным уравнениям:

10 х — - х (t) + n (t), х = -g>x>(t) + п (1); (2) х, =х (t);

= -(t„x<(t ) + nF(t); х = - x (t) + n (t)

20 где ха = A A; хь = В-В; хч = Ч

В =М (B); х — компонента вектора непрерыв)

25 ных оцениваемых параметров

5 = аа Ь. q 1 4)1 7 а — известная постоянная; и (t) — взаимонезавнсимые белые шу1 мы с характеристиками;

М(п (,Ь)) = О, м(п (с ) П3(t, ) — НЫ(t ) 35 (КС!1тф г = „»(t = j (К, (x, t )

F,(x, С)) аС О, (3}

4 — К (2) (С)

22(t) а (х С) з „ л х = -(1 х„

50 а $(х *) о

С

Л

55 Ь ЬхЬ

+ — х 121(с)

ССЛ 22(х С) 2 F(xç t)t.

Эх ь

„ая(х t.) ах, 40 где Р; (х, t) = (2/1(1 )(((t) ° S (t, x)

- (/ $ !x, М) 1 = О, 1

Оптимальная обработка принимаемого сигнала, обеспечивающая формирование наилучшей оценки в cMblcae максимума отношения правдоподобия, реализуется с помощью следующей системы уравнений

2261138 хЧ ха+ Ю К 1{1) ° 12,А; (4) о Ч

xq = -)(„х, + — „К, ((*) ) ЬА;

3$(х 1) о о а.:

2О

g1 tl где индекс Я вЂ” оценка соответствующего параметра;

Х вЂ” длительность элементарной посыло ки °

Входной сигнал поступает на первые входы блока 1 фазовой автоподстройки частоты (фиг ° 1), двух блоков 2 и 3 автоматической регулировки усиления, а также блока 4 выделения информации. В блоке 1 (фиг. 2) сигнал с его выхода подается на первые входы первого и пятого перемножите= лей 6 и 10, на вторые входы которых управляющее напряжение подается соответственно с выходов второго фазо- 30 вращателя 14 и второго сумматора 18.

Полученные в результате перемножения сигналы подаются соответственно на второй перемножитель 7 и второй интегратор 12. Сглаженное напряжение с выхода второго интегратора 12 через нелинейный элемент 20 подается на второй перемножитель 7 и на блоки

2,3 и блок 4. Далее сигнал, .пройдя первый и второй линейные фильтры 15 . щ и 16.суммируется в первом сумматоре

17, а затем йнтегрируется первым интегратором 11. В фазовом модуляторе

19 с помощью опорного генератора 5 осуществляется фазовая модуляция . Ю сигнала.

На третий и четвертый перемножители 8 и 9 фазомодулированный сигнал подается соответственно непосредст- 50 венно и через первый фазовращатель

13. На вторые входы третьего и четвертого перемножителей 8 и 9 управляющие сигналы подаются с первого и второго блоков 2 и 3 автоматической 55 регулировки усиления. Просуммированные сигналы во втором сумматоре 18 используются в пятом перемножителе

l0. В блоках 2 и 3 автоматической регулировки усиления (фиг. 3) с помощью первого, второго, третьего и четвертого перемножителей 21-24, первого и второго сумматоров 26 и 27, линейного фильтра 25 и формирователя

28 опорной амплитуды осуществляется формирование сигналов управления из входного сигнала третьим и четвертым перемножителями 8 и 9.

По управляющему сигналу с выхода блока 1 блок 4 выделения информации (фиг. 4) осуществляет преобразование входного сигнала с помощью первого и второго перемножителей 29 и

30, первого, второго и третьего сумматоров 31-33, фазовращателя 35, интегратора 34, усилителя 36, ограничителя 37 и квадратора 38 с целью выделения из него информационных параметров.

Формула изобретения, 1, Приемник фазоманипулированных сигналов, содержащий блок фазовой автоподстройки частоты, первые вход и выход которого соединены соответственно с первым и вторым входами блока выделения информации, выход которого является выходом приемника, входом которого является первый вход блока фазовой автоподстройки частоты, отличающийся тем, что, с целью повышения достоверности приема при рэлеевских замираниях, в него введены два блока автоматической регулировки усиления, первые входы кото« рых соединены с первым. входом блока фазовой автоподстройки частоты, .пер« вый, второй и третий выходы которого. соединены соответственно с вторыми, третьими и четвертыми входами первого и второго блоков. автоматической регу лировки усиления, выходы подключены соответственно к второму и третьему входам блока фазовой автоподстройки частоты.

2. Приемник по п. 1, о т л и— ч а ю шийся тем, что блок фазовой автоподстройки частоты содержит последовательно соединенные первый перемножитель, второй перемножитель, к второму входу которого под ключен выход нелинейного элемента, первый линейный фильтр, вход которого подключен к входу второго линейного фильтра, первый сумматор, к

1261138 второму входу которого подключен выход второго линейного фильтра, первый интегратор, фазовый модулятор, к второму входу которого подключен выход спорного генератора, первый фазовращатель, к входу которого подключен первьй вход третьего перемножителя, чеТвертый перемножитель и второй сумматор, второй вход и выход которого соединены соответственно с выходом 10 третьего перемножителя и с входом второго фазовращателя, выход которого подключен к второму входу первого перемножителя, первый вход которого соединен с первым входом пятого пе- 15 ремножителя, второй вход и выход которого соединены соответственно с выходом второго сумматора и с входом второго интегратора, выход которого подключен к входу нелинейного эле- 20 мента, при этом первый вход первого перемножителя и вторые входы четвертого и третьего перемножителей являются соответственно первым, вторым и третьим входами блока фазовой автоподстройки частоты, первым, вторым и третьим выходами которого являются соответственно выходы второго сумматора, нелинейного элемента и фазового модулятора. 30

3 Приемникпоп. 1 о тлич aþùèé ся тем, что каждый блок автоматической регулировки усиления содержит последовательно соединенные первый перемножитель, вто- З рой перемножитель, первый сумматор, к второму входу которого подключен выход третьего перемножителя, линейный фильтр, второй сумматор, к второму входу которого подключен вы- 40 ход формирователя опорной амплитуды и четвертый перемножитель, второй вход и выход которого соединены соответственно с вторым входам первого перемножителя и с первым входом третьего перемножителя, причем первый вход первого перемножителя и вторые входы третьего, второго и четвертого перемножителей являются соответственно первым, вторым, третьим и четвертым входами блока автоматической регулировки усиления, выходом которого является выход второго сумматора.

4. Приемник по п. 1, о т л и— ч а ю шийся тем, что блок выделения информации содержит два перемнажителя, фазавращатель и последовательна соединенные квадратор, вход которого подключен к входу фазавращателя, первый сумматор, к второму входу которого подключен выход первого перемножителя, второй сумматор, к второму входу которого подключен выход третьего сумматора, усилитель, интегратор и ограничитель, выход которого является выходом блока выделения информации, первым входом которого является первьй вход первого перемножителя, второй вход которого соединен с входом фазовращателя, выход которого подключен к пер» ному входу второго перемножителя, втовторой вход и выход которого соединены соответственно с первым входом первого перемножителя и с первым входом третьего сумматора, к второму входу которого подключен выход квадратора, вход которого является вторым входом блока выделения информации.! 2б1138

Фиг. Ф

Составитель А. Москевич

Редактор М. Недолуженко . Техред М.Ходанич Корректор А.Зимокосов

Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Заказ 5247/59

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, н я 4