Устройство адресации оперативной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при построении высоконадежных систем оперативной памяти микро-ЭВМ большой информационной емкости. Целью изобретения является повышение достоверности функционирования. Устройство содержит группу блоков выборки, каждый из которых содержит дешифратор, три триггера, три коммутатора, две схемы сравнения и элемент И. Поставленная цель достигается за счет автоматического замещения неисправных страниц памяти резервными страницами . 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5И4 G06 F936

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3868171/24-24 (22) 15.03.85. (46) 07.10.86. Бюл. № 37 (72) В. П. Андреев.и А. И. Беляков (53) 681.32 (088.8) (56) Авторское свидетельство СССР

¹ 1068939, кл. G 06 F 9/36, 1983.

Авторское свидетельство СССР № 999054, кл. G 06 F 9/22, 1982. (54) УСТРОЛСТВО АДРЕСАЦИИ ОПЕ

РАТИВНОЙ ПАМЯТИ (57) Изобретение относится к области вычислительной техники и может быть исполь„„SU„„1262497 зовано при построении высоконадежных систем оперативной памяти микро-ЭВМ большой информационной емкости. Целью изобретения является повышение достоверности функционирования. Устройство содержит группу блоков выборки, каждый из которых содержит дешифратор, три триггера, три коммутатора, две схемы сравнения и элемент И. Поставленная цель достигается за счет автоматического замещения неисправных страниц памяти резервными страницами. 3 ил.

1262497

Изобретение относится к вычислительной технике и может быть использовано для построения высоконадежных систем оперативной памяти микро-ЭВМ большой информационной емкости.

Целью изобретения является повышение достоверности функционирования.

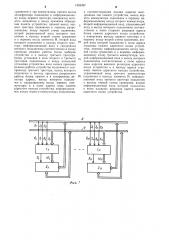

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 — функциональная схема блока выборки; на фиг. 3 — распределение логических адресов.

Устройство содержит группу блоков 1 выборки, адресующих группу блоков 2 памяти, шину 3 управления, шину 4 данных— адреса, все входы блоков выборки подключены к соответствующим функциональным входам устройства, входящим в состав магистралей 3 и 4.

Каждый блок выборки содержит вход 5 адреса — данных, включающий поля 5 признака режима работы блока, 5д адреса зоны памяти, 5 адреса страницы памяти, 5» младших разрядов адреса блока памяти, вход 6 начальной установки, вход 7 записи признака режима работы блока выборки, вход 8 признака обращения к памяти, подключенные к соответствующим входам устройства, выход 9 признака разрешения работы блока памяти, адресный выход 10, включающий поле 10, адреса зоны памяти и поле 10, адреса страницы памяти блока, подключенные к соответствующим входам блока памяти, управляемого данным блоком выборки, дешифратор 11, триггер 12, регистр 13 адреса, коммутаторы 14 и 15, схемы 16 и 17 сравнения, триггеры 18 и 19, элемент И 20, коммутатор 21, поля 22 — 25 адресного входа устройства.

Распределение логических адресов А» по блокам памяти осуществляется следующим образом (фиг. 3) . К старших разрядов

А> определяют адрес блока памяти А „ следующие f разрядов — адрес зоны памяти

Алп, информационный объем V„, которой соответствует адресному пространству микро-ЭВМ определяемому m-разрядным адресом обращения А, микро-ЭВМ; следующие r разрядов — адрес страницы в блоке памяти А, информационный объем Vgn которой соответствует емкости зоны адресов регистров внешних устройств микроЭВМ; m — г младших разрядов — адрес слова

А, внутри страницы блока памяти. Страницы памяти, соответствующие зонам адресов регистров внешних устройств, на фиг. 3 заштрихованы (для примера в качестве этих страниц показаны страницы памяти с максимальным значением А„, что характерно для микро-ЭВМ типа <сЭлектроника — 60») .

Устройство работает следующим образом (работа устройства рассматривается на примере одного из блоков выборки, номер которого опущен) .

При необходимости обращения процессора»о адресу слова, содержащемуся, на15

55 пример, в блоке памяти 2, с помощью блока выборки 1 предварительно производится активизация (т.е. разрешение работы этого блока и выбор внутри него соответствующей зоны емкостью Чзп . Для этого процессор обращается по некоторому адресу Ал из области адресов регистров внешних устройств с записью кодов адресов Ацд и Азп . Код адреса А в дешифруется с помощью дешифраторов 11, — 11, и единичные сигналы с их выходов поступают на информационные входы соответствующих первых три гге ров 12, — 12„

Сигналом, поступающим по шине 3 л на входы 8 — 8П блоков выборки и далее на входы записи соответствующих первых триггеров 12, — 12>, производится запись в них единичной информации. Единичные сигналы с первых выходов первых триггеров

12,— 12„поступают на вторые управляющие входы соответствующих первых схем

16,— 16„сравнения, разрешая их работу. Нулевые сигналы с вторых выходов этих триггеров поступают на управляющие входы соответствующих вторых коммутаторов 15, — 15, разрешая прохождение г старших разрядов адресов Агп с входов

23„— 23П соответствующих блоков выборки на первые входы их вторых схем 17 —

17п сравнения. Через входы 24, — 24 и блоков выборки на входы их первых схем сравнения 16 --16п пос-.упают к — г младших разрядов А». При активизации блока 2 памяти из процессора через вход 5 блока 1 выборки на вход его первой схемы

16 сравнения поступает к — г младших, а через вход 5л на вход второй схемы 17 сравнения — г старших разрядов Аьп . При этом на выходе второй схемы 17 сравнения возникает единичный сигнал, который поступает на первый управляющий вход первой схемы 16 сравнения и разрешает ее работу. Единичный сигнал с выхода первой схемы 16 сравнения блока 1 выборки и нулевые сигналы с выходов первых схем сравнения остальных блоков выборки поступают на информационные входы соответствующих третьих триггеров 191 — 19 и . Сигналом, поступающим с шины 3 магистрали 3 управления через входы 71 — 7П бло ков выборки на входы записи их третьих триггеров 19 — 19„производится установка в единичное состояние триггера 19 блока 1 выборки и в нулевое состояние третьих триггеров остальных блоков выборки.

Единичный сигнал с первого выхода 19 триггера через управляющий выход 9 блока

1 выборки поступает на вход поступления сигнала «Разрешение работы» блока 2 памяти, производя его активизацию, и на входы записи второго триггера 18 и регистра

13 адреса. Передним фронтом единичного сигнала с выхода триггера 19 производится запись в регистр 13 адреса кода адреса зоны

1262497 памяти A3ll поступаюшего на его вход по входу 5 входа 5 адреса — данных, и установка второго триггера 18 в единичное или нулевое состояние в зависимости от требуемого режима работы блока I выборки.

Если на информационный вход триггера 18 по входу 51 входа 5 адреса — данных поступает единичный сигнал, то триггер 18 устанавливается в единичное состояние и тем самым блок 1 выборки переводится в первый режим работы, который обеспечивает возможность блокировки неисправных страниц блока 2 памяти или дальнейшее расширение информационного объема системы оперативной памяти за счет использования страниц блока 2 памяти, соответствующих зонам адресов регистров внешних устройств.

При установке триггера 18 в нулевое состояние блок 1 выборки переводится во второй режим работы, в котором обращения к страницам блока 2 памяти соответствующих зонам адресов регистров внешних устройств, 20 запрещены.

Перед началом работы сигналом «Начальная установка» с входов 6 — 6 блоков выборки производится установка их первых

18 — 18 „и вторых 191 — 19 триггеров в нулевое состояние.

Рассмотрим работу блока 1 выборки в первом режиме.

С выхода регистра 13 адреса по адресному выходу 10 f-разрядный код адреса зоны памяти Аьп поступает на адресные входы блока 1 памяти, производя выборку в нем зоны памяти емкостью Vq и на управляющий вход S-входового первого коммутатора

14. На входы первого коммутатора 14 с входов блока выборки подаются коды адресов неисправных страниц каждой из зон блока 2 памяти. При отсутствии неисправной страницы в какой-либо зоне на соответствующий вход 22 подается код адреса страницы памяти, соответствующей зоне адресов регистров внешних устройств. Код адреса неисправной страницы выбранной зоны блока 2 4О памяти с соответствуюшего входа коммутатора 14 поступает на второй вход второго коммутатора 15.

При обращении процессора к активизированHQMv блоку 2 памяти m-разрядный код А, через вход о адреса данных посту45 пает на вход дешифратора 11, на выходе которого появляется нулевой сигнал. Поэтому по сигналу с входа 8 производится установка первого триггера 12 в нулевое состояние. Единичный сигнал с второго выхода триггера 12 поступает на управляющий вход второго коммутатора 15, разрешая прохождение неисправной страницы выбранной зоны памяти на второй вход второй схемы 17 сравнения. Если обращение процессора производится к неисправной странице выбран- 55 ной зоны памяти, то на выходе второй схемы 17 сравнения возникает единичный сигнал, который через элемент И 20 поступает на управляющий вход третьего коммутатора 21. При этом на выходы 10> адресного выхода блока выборки с его входа 25 поступает код адреса страницы памяти, соответствующей зоне адресов регистров внешних устройств, т.е. производится переадресация обращения к этой странице. Во втором режиме работы нулевой сигнал с выхода второго триггера 18 запрещает появление на выходе элемента И 20 единичного сигнала.

В этом случае код адреса страницы памяти с входа 5 непосредственно поступает на выход 10» и переадресации обращения не производится.

Если страницы памяти, соответствующие зонам адресов регистров внешних устройств, предназначаются для расширения информационного объема системы оперативной памяти, то вторые триггеры 18

18 блоков выборки используются для хранения дополнительного разряда логического адреса обращения, единичное значение которого свидетельствует об обращении к этим страницам, а на входы 22 — 22п блоков выборки подаются коды адресов этих страниц в общем адресном пространстве. Коды адресов на входы 22 — 25 блоков выборки могут быть поданы, например, путем подключения шин этих входов к шине единичного либо нулевого потенциала в зависимости от значения соответствующих разрядов.

Если информационный объем блоков памяти равен V „, то регистры 131 --13 и адресов и первые коммутаторы 141 — 14П в блоках выборки могут отсутствовать. При этом код адреса неисправной страницы блока 2 памяти подается на второй вход второго ком м ута тор а 15.

Таким образом, предлагаемое устройство позволяет осуществить замену в каждой зоне блока памяти одной отказавшей страницы памяти на страницу, адрес которой определяет зону адресов регистров внешних устройств в соответствующей зоне блока памяти, либо использовать эти страницы для дальнейшего наращивания информационного объема системы оперативной памяти микро-ЭВМ.

Формула изобретения

Устройство адресации оперативной памяти, содержащее группу блоков выборки, причем каждый блок выборки содержит дешифратор, регистр адреса и триггер, при этом вход дешифратора подключен к полю адреса обрашения адресного входа устройства, информационный вход регистра адреса подключен к полю адреса зоны памяти адресного входа устройства, отличающееся тем, что, с целью повышения достоверности функционирования, в каждый блок выборки введены два триггера, элемент И, две схемы

1262497 сравнения и три коммутатора, причем выход дешифратора подключен к информационному входу первого триггера, синхровход которого подключен к входу признака обращения памяти устройства, прямой выход первого триггера подключен к первому разрешающему входу первой схемы сравнения, второй разрешающий вход которого подключен к выходу второй схемы сравнения и к первому входу элемента И, второй вход которого подключен к выходу второго триггера, информационный вход и синхровход которого подключены соответственно к входу признака режима работы блока выборки устройства и к выходу третьего триггера, входы установки в ноль второго и третьего триггеров подключены к входу начальной установки устройства, вход записи признака режима работы устройства подключен к синхровходу третьего триггера, выход которого подключен к выходу признака разрешения работы блока памяти и к синхровходу ре- >0 гистра адреса, выход которого подключен к управляющему входу первого коммутатора и к полю адреса зоны памяти адресного выхода устройства, информационные входы первого коммутатора подключены к соответствующим входам адресов неисправных зон памяти устройства, выход первого коммутатора подключен к первому информационному входу второго коммутатора, второй информационный вход, управляющий вход и выход которого подключены соответственно к полю старших разрядов адреса блока памяти адресного входа устройства, к инверсному выходу первого триггера и к первому входу второй схемы сравнения, второй вход которой подключен к полю адреса страницы памяти адресного входа устройства, первому информационному входу первой схемы сравнения и к первому информационному входу третьего коммутатора, второй информационный вход и выход которого подключены соответственно к полю адреса зоны адресов внешних регистров адресного входа устройства и к выходу адреса страницы памяти адресного выхода устройства, управляющий вход третьего коммутатора подключен к выходу элемента И, информационный вход третьего триггера подключен к выходу первой схемы сравнения, второй информационный вход которой подключен к полю младших разрядов адреса памяти адресного входа устройства.

1262497 иа 5аок 2 памяти фиг.. 2

Погическии адрес обращения An

Aofm)

&ал naasmun

Составитель М. Силин

Редактор В. Данко Техред И. Верес Корректор О. Луговая

Заказ 5429/47 Тираж 67! Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4