Устройство для сопряжения двух вычислительных машин

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ЭЛЕКТРОННО-ВЫЧИСЛИТЕЛЬНЫХ МАШИН (ЭВМ), содержащее два интерфейсных блока, в каждый из которых входит узел приемопередающих усилителей , дещифратор управляющих сигналов, дещифратор адреса, регистр состояния, коммутатор , регистр данных вывода, причем магистральная группа входов-выходов узла приемопередающих усилителей каждого интерфейсного блока соединена с информационными входами-выходами соответствующей ЭВМ, группа информационных выходов , группа выходов состояния, группа адресных выходов и группа управляющих выходов узла приемопередающих усилителей соединены соответственно с группами информационных входов регистра данных вывода, регистра состояния, дешифратора адреса и дешифратора управляющих сигналов , а группы выходов коммутатора и дешифратора управляющих сигналов соединены соответственно с группами информационных и управляющих входов узла приемопередаточных усилителей, первый, второйи третий выходы дешифратора управляющих сигналов соединены соответственно с синхровходами регистра данных вывода, коммутатора и регистра состояния, выход дещифратора адреса соединен со стробирующим входом дешифратора управляющих сигналов, выход разряда идентификации регистра состояния соединен с информационным входом коммутатора , выходы регистра даннь1х вывода соединены с первой группой информационных входов коммутатора, отличающееся тем, что, с целью повышения достоверности обмена информации между ЭВЛ, в каждый интерфейсный блок введены регистр данных ввода и две группы шинных формирователей, причем выходы регистра данных вывода соединены с информационными входами iiniHных формирователей первой группы, вы.чоды которых соединены с второй группой информационных входов коммутатора, четвертый выход дешифратора управляющих сигналов соединен с управляющими входами шинных формирователей первой группы, выходы шинных формирователей второй группы соединены с соответствующими информационФ ными входами регистра данных ввода, вы (Л ходы которого соединены с третьей группой информационных входов коммутатора и с соответствующими информационными входами шинных формирователей второй группы, пятый выход дешифратора управляющих сигналов одного интерфейсно1-о блока соединен с входом стробирования реГС гистра состояния и синхровходом регистра О5 данных ввода другого интерфейсного блоN3 С71 ка, выходы разрядов «ошибка передачи и «Готовность обмена регистра состояния одного интерфейсного блока соединены соответственно с входами разрядов «Ошибка передачи и «Готовность обмена регистра состояния другого интерфейсного блока , четвертый выход дешифратора унравляюших сигналов одного интерфейсного блока соединен с управляющими входами П1ИННЫХ формирователей второй группы другого интерфейсного блока, входы-выходы шинных формирователей первой и второй групп одного интерфейсного блока соединены с входами-выходами шинных формирователей второй и первой групп другого интерфейсного блока.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1262511

А1 (51) 4 G 06 F 1300

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

4 1")

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

H А BTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3873965/24-24 (22) 22. 03. 85 (46) 07.10.86. Бюл. № 37 (72) А. B. Петров и E. Ю. Пчелкина (53) 681.3 (088.8) (56) Авторское свидетельство СССР № !051527, кл. G 06 F 3/04, 1982.

Авторское свидетельство СССР № 922716, кл. G 06 F 3/04, 1980. (54) (57) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ЭЛЕКТРОННО-ВЫЧИСЛИТЕЛЬНЫХ МАШИН (ЭВМ), содержащее два интерфейсных блока, в каждый из которых входит узел приемопередающих усилителей, дешифратор управляющих сигналов, дешифратор адреса, регистр состояния, коммутатор, регистр данных вывода, причем магистральная группа входов-выходов узла приемопередающих усилителей каждого интерфейсного блока соединена с информационными входами-выходами соответствующей ЭВМ, гру ппа информационных выходов, группа выходов состояния, группа адресных выходов и группа управляющих выходов узла приемопередающих усилителей соединены соответственно с группами информационных входов регистра данных вывода, регистра состояния, дешифратора адреса и дешифратора управляющих сигналов, а группы выходов коммутатора и дешифратора управляющих сигналов соединены соответственно с группами информационных и управляющих входов узла приемопередаточных усилителей, первый, второй и третий выходы дешифратора управляющих сигналов соединены соответственно с синхровходами регистра данных вывода, коммутатора и регистра состояния, выход дешифратора адреса соединен со стробирующим входом дешифратора управляющих сигналов, выход разряда идентификации регистра состояния соединен с информационным входом коммутатора, выходы регистра данных вывода соединены с первой группой информационных входов коммутатора, отличающееся тем, что, с целью повышения достоверности обмена информации между ЭВМ, в каждый интерфейсный блок введены регистр данных ввода и две группы шинных формирователей, причем выходы регистра данных вывода соединены с информационными входами шинных формирователей первой группы, выходы которых соединены с второй группой информационных входов коммутатора. четвертый выход дешифратора управляющиx сигна

;IoB соединен с управляющими входами lllllHных формирователей первой группы, выходы шинных формирователей второй группы ñooдинены с соответствующими информационными входами регистра данных ввода. выходы которого соединены с третьей группой информационных входов коммутатора и с соответствующими информационными входами шинных формирователей второй группы, пятый выход дешифратора управляющих сигналов одного интерфейсно1о блока соединен с входом стробирования регистра состояния и синхровходом регистра данных ввода другого интерфейсного блока, выходы разрядов «ошибка передачи» и

«Готовность обмена» регистра состояния одного интерфейсного блока соединены соответственно с входами разрядов «Ошибка передачи» и «Готовность обмена» регистра состояния другого интерфейсного блока, четвертый выход дешнфратора управляющих сигналов одного интерфейсного блока соединен с управляющими входами шинных формирователей второй группы другого интерфейсного блока, входы-выходы шинных формирователей первой и второй групп одного интерфейсного блока соединены с входами-выходами шинных формирователей второй и первой групп другого интерфейсного блока.

1262511

Изобретение относится к вычислительной технике и может найти применение в вычислительных системах.

Целью изобретения является повышение достоверности обмена информацией между

ЭВМ.

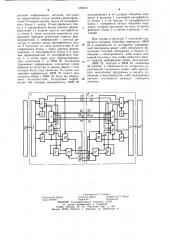

На чертеже представлена блок-схема устройства.

Устройство содержит первый и второй интерфейсные блоки 1 и 2, каждый из которых включает узел приемопередающих усилителей 3, дешифратор 4 управляющих сигналов, дешифратор 5 адреса, регистр 6 данных вывода, регистр 7 состояний, коммутатор 8, регистр 9 данных ввода, группы шинных формирователей 10 и 11. Устройство также содержит входы-выходы 12 — 19 интерфейсных блоков, двунаправленные шины 20 и 21 — шины данных. Интерфейсные блоки 1 и 2 подключены соответственно к

ЭВМ 22 и 23.

Обмен информацией между ЭВМ осуществляется в программном режиме и включает в себя адресный цикл и цикл приема или передачи данных.

Со стороны ЭВМ в каждом интерфейсном блоке программно доступными являются регистр 7 состояний, регистры 6 и 9 данных вывода. При считывании информации из регистра 9 в режиме контроля соответствующим образом включаются двунаправленные шинные формирователи 10 и 11 и производится чтение информации, хранящейся в регистре 9 данных ввода, в ту ЭВМ, которая произвела запись в этот регистр информации.

Для обращения к любому из регистров, ЭВМ в адресном цикле операции помещает адрес необходимого регистра, старшие разряды которого указывают на принадлежность этого адреса к области адресов интерфейсного блока, куда входит регистр, а младшие разряды — на конкретный регистр, к которому идет обращение. В случае соответствия адресов дешифратора 5 адреса

ЭВМ выдает на дешифратор 4 управляющих сигналов сигнал выборки устройства.

Дешифратор 4 управляющих сигналов производит выбор необходимого регистра интерфейсного блока и, в зависимости от вида операции, проводимой ЭВМ, производит либо запись информации в выбранный регистр, либо считывание из него данных.

Дешифратор 4 управляющих сигналов обеспечивает также выдачу в ЭВМ синхросигнала, позволяющего машине судить о правильности проводимого цикла обращения к устройству.

Устройство работает следующим образом

При включении питания или по сигналу начальной установки, поступающему в интерфейсные блоки 1 и 2 от управляющих ими

ЭВМ, регистры 7 состояний каждого из

5 о

<о

55 интерфейсных блоков 1 и 2 выставляют на выходах 16 сигналы готовности интерфейсных блоков к приему информации, с выхода 16 одного интерфейсного блока сигнал готовности поступает через входы !7 в регистр 7 состояний другого интерфейсного блока.

При необходимости, например, передать слово информации из ЭВМ 22 в ЭВМ

23 управляющая программа ЭВМ 22 опрашивает регистр 7 состояний интерфейсного блока 1 и анализирует его на наличие сигнала

«готовность вывода». В случае наличия такого сигнала ЭВМ проводит операцию записи информации в регистр 6 данных вывода. Эта информация поступает на информационные входы шинных формирователей

10 первой группы и, так как на его управляющем входе сигнал «Считывание контрольной информации» отсутствует, передается на вторую двунаправленную шину 21 данных первого интерфейсного блока и первую двунаправленную шину 20 данных второго интерфейсного блока.

Так как сигнал «считывание контрольной информации» на управляющих входах шинных формирователей 11 второй группы второго интерфейсного блока отсутствует, то информация, поступающая по первой двунаправленной шине 20, данных, будет транслироваться, соответственно, на входы регистра 9 данных ввода интерфейсного блока 2. Запись информации в регистр 9 данных ввода интерфейсного блока 2 будет осуществляться по сигналу стробирования, поступающему на вход 12 интерфейсного блока 2 с выхода 13 дешифратора 4 интерфейсного блока l.

Управляющая программа ЭВМ 23 опрашивает регистр 7 состояний интерфейсного блока 2 и анализирует его на наличие сигнала «Готовность ввода». При наличии такого сигнала ЭВМ 23 проводит операцию чтения информации из регистра 9 данных ввода интерфейсного блока 2. Выполнение операции чтения из регистра 9 данных ввода вызывает обнуление разряда «Готовность ввода» регистра 7 интерфейсного блока 2 и установку на выходе 16 этого блока сигнала готовности, который, поступая на вход

17 интерфейсного блока 1 и затем в регистр 7 состояний, может быть считан оттуда ЭВМ

22 как сигнал готовности вывода.

Далее ЭВМ 22 вновь может осуществить передачу слова информации в ЭВМ 23.

В случае, если ЭВМ 22 необходимо убедиться в правильности переданной в ЭВМ 23 информации, т.е. фактически той, которая была записана в регистр 9 данных ввода интерфейсного блока 2 и затем считана оттуда в ЭВМ 23. ЭВМ 22 проводит операцию чтения информации из регистра 9 интерфейсного блока 2, при которой дешифратор 4 выдает сигнал «Считывание конт1262511

«Ошибка перей интерфейсноинтерфейсного

«Ошибка перевход 15 интеррегистр 7 сосустанавливает в «1» разряд дачи» в регистре 7 состояни го блока 1 и на выходе 14 блока 1 появляется сигнал дачи», который поступает на фейсного блока 2 и затем в тояний.

Составитель Г. Стернин

Редактор В. Данко Техред И. Верес Корректор Л. Патай

3a к а з 5429/47 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 рольной информации», который поступает на управляющие входы шинных формирователей 10 первой группы, выход 18 интерфейсного блока 1, входы 19 интерфейсного блока 2 и управляющие входы шинных формирователей 11 второй группы интерфейсного блока 2. Этим сигналом изменяется направление передачи указанных шинных формирователей, и информация с выхода регистра 9 данных ввода интерфейсного блока 2 поступает на вход коммутатора 8 интерфейсного блока 1 через шинные формирователи 11 интерфейсного блока 2 и шинные формирователи 10 интерфейсного блока 1, а затем через узел приемопередающих усилителей 3 в ЭВМ 22. Последняя сравнивает информацию, считанную таким образом из регистра 9 данных ввода, с той, которая была туда записана. В случае совпадения информации ЭВМ 22 может продолжить обмен с ЭВМ 23. Если же обнаружено несоответствие полученной информации той, которая записывалась, ЭВМ 22

При чтении в регистре 7 состояний единичного разряда «Ошибка передачи» ЭВМ

23 в зависимости от алгоритма управляющей программы может либо прекратить выполнение текущей программы и выдать сообщение о неисправности, либо ждать повторной посылки с тем, чтобы поместить вместо ложной информации вновь полученную.

ЭВМ 22, передав в ЭВМ 23 сообщение об ошибке, в зависимости от алгоритма управляющей программы может либо прекратить выполнение программы и выдать сообщение о неисправности, либо дождавшись сигнала «готовность вывода», повторить посылку.