Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ. Цель изобретения - повьтение быстродействия . Микропрограммное устройство управления содержит блок 1 местного управления, блок 2 обработс S т ел

СОКИ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

„SU„1262516 (50 4 С 06 Р 15/00 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3729126/24-24 (22) 20.04.84 (46) 07.10.86. Бюл. В 37 (72) А.И..Подгорнов, P.С.Мойса, А.Я.Костинский и А.М.Чугаев (53) 681.32 (088.8) (56) Авторское свидетельство СССР

Р 732871, кл. G 06 F 9/22, 1976.

Авторское свидетельство СССР

У 763898, кл. G 06 F 9/22, 1976. (54) I.МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ (57) Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ.

Цель изобретения — повьппение быстродействия. Микропрограммное устройство управления содержит блок местного управления, блок 2 обработ1262516

30 ки условий формирования адреса, память 3, регистр 4 адреса, триггер 5 выбора двойного слова, триггер 6 выбора слова, блок 7 регистров, элемент И 8, триггер 9 блокировки. элемент 2И-ИЛИ 10, два дешифратора

11,14 состояний, два счетчика 12,13 повторений и коммутатор 16 микрокоманд, Сущность изобретения заключается в том, что из памяти выбирают1

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ.

Цель изобретения — повышение быстродействия. 5

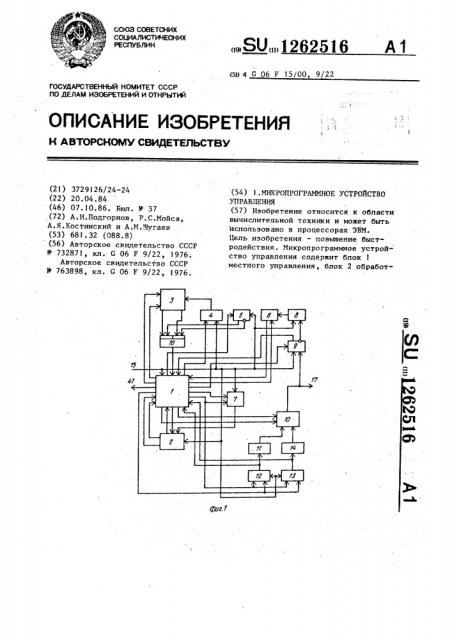

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг.2 — блок обработки условий формирования адреса; на фиг.3 блок местного управления. 10

Устройство (фиг.1) содержит блок 1 местного управления, блок 2 обработки условий формирований адреса, память 3, регистр 4 адреса, триггер 5 выбора двойного слава, 15 триггер 6 выбора слова, блок 7 регистров, элемент И 8, триггер 9 блокировки, элемент 2И-ИЛИ 10, первый дешифратор 11 состояний, первый счетчик 12 повторений, второй счет — 20 чик 13 повторений, второй дешифратор 14 состояний, вход 15 синхрони зации, коммутатор 16 микрокоманд, выход 17 признака цикла.

Блок обработки условий формирования адреса (фиг.2) содержит первый регистр 18, второй регистр 19, арифметика-логический узел 20, третий 21 и четвертый 22 регистры.

Блок местного управления (фиг.3) содержит входной регистр 23, регистр 24 маски, выходной регистр

25, регистр 26 микрокоманд, узел 27 элементов 4И-ИЛИ, первый 28 и вто- З5 рой 29 коммутаторы, первый 30 и второй 31 элементы 3И-KIH первый 32 второй 33„ четвертый 34 и третий 35 элементы И, первый 36 и второй 37 дешифраторы, первый 38 и второй 39 40 мультиплексоры и узел 40 элементов ся сразу четыре микрокоманды, а параллельно с этим осуществляется формирование условий перехода (в микрокоманде условного перехода) .Выборка нужного двойного слова, содержащего микрокоманду, заносится в регистр микрокоманд. При этом разницы Во временах выполнения микрокоманды условного и безусловного переходов нет. з ° п ф лы 3 ип.

И. Устройство имеет управляющий выход 41 .

Памяти выбираются =разу четыре микрокоманды, а параллельно с этим осуществляется формирование условий перехода (в микрокоманде условного перехода) . Выборка нужного двойного слова, содержащего микрокомаиду, заносится в регистр микрокоманд. При этом разницы во временах выполнения микрокоманды условного и безусловного переходов нет.

В один из счетчиков повторений или в оба сразу заносится константа, определяющая число выполнений одной и той же микрокоманды. При первом выполнении этой микрокоманды устанавливается триггер блокировки, который блокирует прием иэ памяти новой микрокоманды. Модифицируясь, счетчики изменяют адреса блоков регистров, участвующих в выполнении микрокоманды. Так как время на формирование адреса следующей микрбкоманды при этом учитывать не надо, то цикл устройства определяется только временем "чтение регистра + выполнение операции арифметика-логическим узлом". После обнуления одного из счетчиков повторений. триггер блокировки сбрасывается и из памяти выбирается новая микрокоманда.

В микрокомандах условнoro перехо" да в качестве условия перехода может использоваться как результат выполнения операции в блоке 2, так и со« держимое отдельных разрядов какоголибо регистра из блока регистров, а также смешанное условие перехода.

Устройство ориентировано на выполне1262 ние микрокоманды условного перехода при возможности выполнения перехода с коэффициентом ветвления, равным 4.

В этом случае условия перехода могут принимать следующие значения: 00, 01,10,11 ° Таким образом, адрес группы из четырех микрокоманд задан в самой микрокоманде, а конкретный переход определяется путем опроса заданных в микрскоманде условий. f0

Работа устройства при выполнении микрокоманды условного перехода можно разбить на следующие этапы: считывание из памяти 3 группы из четырех микрокоманд; считывание одного из регистров, входящих в состав блока 7 регистров и содержащего биты, являющиеся услонием перехода; формирование условий перехода; установка триггера 5 выбора двойного слова; установка триггера 6 выбора слова; занесение очередной микрокоманды в регистр 26 микрокоманд; дешифрация выбранной микрокоманды.

По содержимому регистра 4 адреса из памяти 3 считывается четыре слова, которые поступают на коммутатор 16 микрокоманд, на котором выбирается нужное двойное слово по состоянию триггера 5 выбора двойного 30 слова. Далее выбранное двойное сло-во заносится в выходной регистр

25. В свою очередь это двойное слово подается на коммутатор 29, на котором выбирается нужное слово по состоянию триггера 6 выбора слова. Выбранное слово заносится в регистр 26 микрокоманд, содержимое которого подается на второй дешифратор 37.

Под управлением соответстнующего,40 второго дешифратора 37 на коммутаторе 28 выбирается слово из памяти 3 с коммутатора 29 или значение регистра 21 блока 2 и передается через тракт данных в регистры блока ?.

В формировании адресон регистров 7 блока, поступающих из первого дешифратора 36, участвуют определенные разряды регистра микрокоманд 26, значение соответствующего выхода второ-;0 го дешифратора 37 и значения первого 12 и второго 13 счетчиков. Под управлением соответствующих выходов второго дешифратора 37 на элементах ЗИ-ИЛИ 30 и 31 выбираются признаки результата с регистра 22 блока 2, под управлением второго дешифратора 37, кроме того, выбираются

516 4 признаки безусловных переходов с регистра 26 микрокоманд.

В случае выполнения микрокоманды условного перехода соответствующие выходы второго дешифратора 37 упранл;=ют выбором на первом 38 и втором 39 мультиплексорах условий перехода, подаваемых с регистра 21 блока 2 на фоне чтения группы из четырех слоев памяти 3. Эти выбранные условия переходов под управлением соответствующих выходов второго дешифратора 37 передаются на установку новых значений триггера 5 выбора двойного слова и триггера 6 выбора слова.

В микропрограммах часто встречаются циклы, н которых однотипные действия выполняются над различными операндами. Микрокоманды, составляющие цикл, отличаются только полями, адресующими операнды. При этом н основу работы устройства положено требование размещения операндов, участвующих в цикле, в регистрах блока 7, имеющих последовательные адреса. Работу устройства в этом случае можно разбить на следующие этапы: выбора микрокоманды из памяти 3 в регистр 26 микрокоманд; занесение в счетчики 12 и 13 константы, определяющей количество микрокоманд в цикле; состояние счетчиков l? и 13; считывание операндов в блок 2; формирование результата в блоке 2; состояние триггера 9 блокировки; модификация счетчиков.

После занесения такой микрокоманды в регистр 26 микрокоманд с соответствующего выхода второго дешифратора выдается сигнал занесения в первый 12 и второй !3 счетчики из памяти через тракт данных. В случае ненулевых значений первого !2 или второго 13 счетчиков с элемента 2ИИЛИ 10 под управлением соответствующих выходов второго дешифратора

37 вырабатывается сигнал, устанавливающий в единичное состояние триггер 9 блокировки, который, в свою очередь, блокирует прием новой информации из памяти 3 в выходной регистр 25 и блокирует изменения сос— тояния триггера 6 выбора слова. Состоян2 е этого триггера обеспечивает повторную выборку данной микрокоманды из выходного регистра 25, исключая обращение к памяти 3. Одновре1262:"> менной сигнал с выхода элемента

2И-ИЛИ 10 поступает на выход 17 для уменьшения длительности цикла процессора на время, неоГ>ходимое для обра" щения к памяти. Количество повторений данной микрокоманды определяется состоянием счетчиков 12 и 13. При обнулении счетчиков через. выход 17 выдается сигнал увеличения цикла процессора и сбрасывается триггер

9 блокировки, который разрешает прием очередной микрокоманды из!

20

50 памяти. формула изобретения

l ° Микропрограммное устройстно управления, содержащее блок обработки условий формирования адреса, блок регистров, триггер выбора двойного слова, триггер выбора слова, регистр адреса, память и блок местного управления, содержащий входной регистр, выходной регистр, регистр маски, регистр микрокоманд, дгза мультиплексора, узел элементов 4И-ИЛИ, два децгиАратора, дна элемента ЗИ-ИЛИ, два коммутатора, узел элементон И и с первого по третий элементы И, причем информационный вход памяти соединен с выходом узла элементов 4И-ИЛИ, первые входы первой и второй групп ко30 торого соединены с выходом входного регистра, информационнь!й вход которого соединен с информационным выходом блока обработки условий формирования адреса, второй информационный выход которого соединен с первым информационным входом первого коммутатора, второй информационный вход которого соединен с информационным входом регистра микрокоманд и с выходом второго коммутатора, первый информационный вход которого соединен с первым входом третьей группы узла элементон 4И-ИЛИ и с первым выходом выходного регистра, второй выход которого соединен с вторым ивАормационннм нходом второго коммутатора и первым входом четвертой группы узла элементов 4И-ИЛИ, RTopE>p входы первой и четвертой групп которого соединены с прямым выходом узла элементов И, инверсный выход которого соединен с первыми входами второй и третьей групп узла элементов 4ИИЛИ, первый вход узла элементов И соединен с выходом регистра маски, информационный вход которого соединен с выходом поля маски регистра

l6 Ь микрокомаил, выход поля анализируемого условия которого соединен с первым входом первого дешифратора, второй вход и выход которого соединены соответственно с первым ныходом второго дешифратора и входом номера регистра блока регистрон, вход синхронизации которого соединен с входами синхронизации триггера выбора двойного слова, регистра адреса, регистра микрокоманд и блока обраГ>отки условий формирования адреса, первыми входами первого, второго и третьего элементов И и входом синхронизации устройства, второй вход узла элементов И соединен с управляюI щим входом второго коммутатора и ныходом триггера выбора слов, вход синхронизации которого соединен с выходом первого элемента ЗИ-ИЛИ, первый и второй входы первой группы которого соединены соответственно с вторым выходом второго дешифратора и выходом второго мультиплексора, управляю!>гий вход которого соединен с третьим выходом второго дешиАратора, четвертый выход которого соединен с управляющим входом первого мультиплексора, выход которого соединен с первым входом первой группы второго элемента ЗИ-ИЛИ, второй вход первой группы которого соединен с пятым выходом второго дешифратора, шестой и седьмой выходы которого соединены соответственно с перными входами второй и третьей групп второго элемента ЗИ-ИЛИ, второй вход второй группы которого соединен с ныходом признака выбора двойного слова регистра микрокоманд, выход признака выбора слова которого соединен с первым входом второй группы первого элемента ЗИ-ИЛИ, второй вход второй группы которого соединен с восьмым выходом второго дешифратора, девятый и десятый выходы которого соединены соответственно с первым входом третьей группы первого элемента ЗИ-ИЛИ и с управляющим входом первого коммутатора, выход которого соединен с информацион-. ным входом блока регистров, выход которого соединен с информационным входом блока обработки условий Аормирования адреса, вход кода операции которого соединен с одиннадцатым выходом второго дешиАратора, двенадцатый, тринадцатый и четырнадца10

7 262 тый выходы которого соединены с вторыми входами соответственно первого, второго и третьего элементов И, выходы которых соединены соответственно с входами записи входного регист- 5 ра, регистра маски и памяти, адрес-. ный вход которой соединен с выходом регистра адреса, информационный вход ксторого соединен с выходом поля адреса регистра микрокоманд, выход поля местного управления которого соединен с входом второго дешифратора, вторые входы третьих Групп первого и второго элементов 3И-ИЛИ соединены с выходом признака результ:.:. блока обработки условий форми.— рования адреса, выход второго элемента 3И-ИЛИ соединен с информационным входом триггера выбора двойного слова, выход поля микрооперации регист- 20 ра микрокоманд подключен к управляющему выходу устройства, о т л и— ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены коммутатор микрокоманд, элемент

И, триггер блокировки, элемент 2И-ИЛИ первый и второй дешифраторы состояний, перый и второй счетчики повf торений, кроме того, в блок местного управления введен четвертый элемент И, причем вход синхронизации устройства подключен к входу синхронизации триггера блокировки, к счетным входам первого и второго счетчиков повторений, к первому входу элемента И устройства и первому входу четвертого элемента И, второй вход которого соединен с прямым выходом триггера блокировки, инверсный выход которого соединен с вторым вхо- 40 дом элемента И устройства, выход которого соединен с входом синхронизации триггера выбора слова, информационный вход триггера блокировки соединен с пятнадцатым выходом вто- 4> рого детифратора, шестнадцатый и семнадцатый выходы которого соединены соответственно с первыми входами первой и второй групп элемента 2ИИЛИ,. вторые входы первой и второй групп которого соединены соответственно с выходами первого и второго дешифраторов состояний, выход элемента 2И-ИЛИ соединен с входом установки в ноль триггера блокировки и с выходом признака цикла устройства, 5!6 8 вход первого дешифратора состояний соединен с третьим входом первого дешифратора и с выходом первого счетчика повторений, вход записи/счета которого соединен с входом записи/

/счета второго счетчика повторений и восемнадцan-ьм выходом второго дешифратора, выход первого комму татора соединен с информационными входами первого и второго счетчиков повторений, выход второго счетчика повторений соединен с четвертым входом первого дешифратора и с входом второго дешифратора состояний, выход четвертого элемента И соединен с входом записи выходного регист ра, информационный вход которого соединен с выходом коммутатора микрокоманд, первый и второй управляющие входы которого соединены соот" . ветственно с прямым и инверсным выходами триггера выбора двойного сло ва, первый и второй информационные входы коммутатора микрокоманд соединены-соответственно с первым и вторым выходами памяти.

2. Устройство по п.1, о т л ич а ю щ е е с я тем, что блок обработки условий формирования адреса содержит четыре регистра и арифметико-логический узел, причем информационный вход блока соединен с информационными входами первого и второго регистров, входы синхронизации которых соединены с входами синхронизации третьего и четвертого регистров и подключены к входу синх.. ронизации блока, выход первого регистра соединен с первым информационным входом арифметико-логического узла и подключен к первому информационному выходу блока, выход второго регистра соединен с вторым информационным входом арифметико-логи ческого узла, вход кода операции которого подключен к входу кода операции блока, выходы результата операции и признака результата операции арифметико-логического узла соедине-. ны соответственно с информационными входами третьего и четвертого регистров, выходы которых являются соответственно вторым информационным выходом и выходом признака результата блока.

1262516

Фиг Я

Составитель Ю.Ланцов

Редактор С,Патрушева Техред И.Поповк с Корректор С.Черни

Заказ 5430/48 Тираж 671

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35. Раушская наб., д.4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул. Проектная, 4