Устройство для передачи телеметрической информации

Иллюстрации

Показать всеРеферат

Изобретение может использоваться в адаптивных телеметрических системах, где требуется сжатие передаваемой информации . Целью изобретения является повышение информативности устройства. Устройство осуществляет сжатие информации от каждого канала (датчика) в соответствии с алгоритмом предсказателя первого порядка и передачу на выход только существенных отсчетов входных сигналов и кода числа идущих подряд несущественных отсчетов . Устройство содержит хронизатор, коммутатор, формирователь импульсов, блок памяти, аналого-цифровой преобразователь, накапливающий и вычитающий счетчики, регистр, счетчик несущественных отсчетов, блок сравнения, элементы ИЛИ и блок задержки . Хрокизатор содержит генератор тактовых импульсов, элемент И, триггер, ключи, делитель частоты, элемент ИЛИ и элемент задержки. Блок сравнения содержит элементы И и элементы ИЛИ. Счетчик несущественных отсчетов содержит элементы ИЛИ, счетчик и элементы И. Блок памяти содержит элементы И. Аналого-циф (Л ровой преобразователь содержит триггер, элемент И, элемент сравнения, счетчик, элементы И и цифроаналоговый преобразователь . 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК î 4 G 08 С 19/28

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

OllHCAHHE ИЗОБРЕТЕНИЯ l3, 13

Н А BTOPCKOMY СВИДЕТЕЛЬСТВУ (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ

ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ (57) Изобретение может использоваться в адаптивных телеметрических системах, где требуется сжатие передаваемой информации. Целью изобретения является повышение информативности устройства. Устройство осуществляет сжатие информации от каждого канала (датчика) в соответствии (21) 3869089/24-24 (22) 12.03.85 (46) 07.10.86. Бюл. № 37 (71) Институт кибернетики АН АЗССР (72) Т. А. Алиев, P. М. Кадымов и Я. А. Атакишиев (53) 621.398 (088.8) (56) Авторское свидетельство СССР № 594517, кл. G 08 С 19/28, Н 04 J 3/00, 1976.

Авторское свидетельство СССР № 1123045, кл. G 08 С 19/28, 1984.

„„SU,„, 1262553 А1 с алгоритмом предсказателя первого порядка и передачу на выход только существенных отсчетов входных сигналов и кода числа идущих подряд несущественных отсчетов. Устройство содержит хронизатор, коммутатор, формирователь импульсов, блок памяти, аналого-цифровой преобразователь, накапливающий и вычитающий счетчики, регистр, счетчик несущественных отсчетов, блок сравнения, элементы ИЛИ и блок задержки. Хронизатор содержит генератор тактовых импульсов, элемент И, триггер, ключи, делитель частоты, элемент ИЛИ и элемент задержки. Блок сравнения содержит элементы И и элементы ИЛИ. Счетчик несущественных отсчетов содержит элементы ИЛИ, счетчик и элементы И. Блок памяти содержит элементы И. Аналого-цифровой преобразователь содержит триггер, элемент И, элемент сравнения, счетчик, элементы И и цифроаналоговый преобразователь. 5 ил.

1262553

Изобретение относится к телеметрии и может использоваться в адаптивных информационно-измерительных системах.

Целью изобретения является повышение информативности устройства.

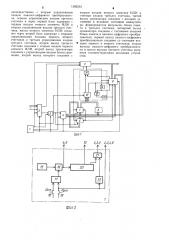

На фиг. показана структурная схема устройства; на фиг. 2 — функциональная схема хронизатора; на фиг. 3 — функциональная схема блока сравнения; на фиг. 4— функциональная схема счетчика несущественных отсчетов; на фиг. 5 — функциональная схема аналого-цифрового преобразователя.

Устройство для передачи телеметрической информации (фиг. 1) содержит хронизатор 1, коммутатор 2, формирователь 3 импульсов, блок 4 памяти, аналого-цифровой преобразователь 5, первый накапливающий счетчик 6, второй вычитающий счетчик

7, регистр Я,третий счетчик 9 несущественных отсчетов, блок 10 сравнения, первый 11 и второй 12 элементы ИЛИ, второй 13 и первый 14 блоки задержки.

Хронизатор 1 (фиг. 2) содержит генератор 15 тактовых импульсов, элемент И

16, триггер !7, ключи 18 и 19, делитель 20 частоты, элемент ИЛИ 21 и элемент 22 задержки.

Блок 10 сравнения (фиг. 3) содержит элементы И 23 — 30 и элементы ИЛИ 31 — 34.

Счетчик 9 несущественных отсчетов (фиг. 4) содержит элементы ИЛИ 35 и 36, счетчик 37 и элементы И 38 и 39.

Блок 4 памяти (фиг. 4) содержит элементы И 40 и 4!.

Аналого-цифровой преобразователь 5 (фиг. 5) содержит триггер 42, элемент И 43, элемент 44 сравнения, счетчик 45, элементы

И 46 и цифроаналоговый преобразователь 47.

Устройство работает следующим образом.

Коммутатор 2 опрашивает поочередно все датчики (каналы).

Рассмотрим работу устройства в К-м цикле преобразования. К концу (К вЂ” 1) -го цикла преобразования в каждом адресе блока 4 памяти находятся младшие разряды цифровых отсчетов каждого канала этого цикла, разность двух соседних (К вЂ” 2) -го и (К вЂ” 1)-го циклов преобразования отсчетов и количество идущих подряд несущественных отсчетов, соответствующих (К вЂ” 1)му циклу преобразования. В начале К-го цикла преобразования сигнал с первого выхода хронизатора 1 поступает на входы коммутатора 2 и формирователя 3. При этом измеряемый аналоговый сигнал первого канала через коммутатор 2 поступает на вход аналого-цифрового преобразователя 5, а код номера канала, по которому подготавливаются соответствующие адреса блока 4 памяти данного канала, передается с выхода коммутатора 2 на вход формирователя 3.

Последний вырабатывает сигнал, который устанавливает в нуль накапливающий 6 и вычитающий 7 счетчики и задает адрес канала на входе блока 4 памяти. По этому адресу из блока 4 памяти по кодовым шинам числа младшие разряды цифрового отсчета первого канала (К вЂ” 1) -го цикла преобразования передаются в вычитающий счетчик 7, разность двух соседних (К вЂ” 2) -го и (К вЂ” 1)-ro циклов преобразования (отсчетов) заносится в регистр 8, количество идущих подряд несущественных отсчетов первого канала соответствующих (К вЂ” 1) -ому циклу преобразования, заносится в счетчик 9 несущественных отсчетов.

Сигнал с первого выхода хронизатора 1 поступает также на вход преобразователя 5 (фиг. 5), устанавливая в единичное состояние триггер 42, который единичным выходом разрешает прохождение импульсов от хронизатора 1 через элемент И 43 на вход счетчика 45. С поступлением каждого из этих импульсов содержимое счетчика 45 увеличивается на единицу. Благодаря этому на выходе преобразователя 47 образуется ступенчато нарастающее напряжение, высота каждой ступеньки которого равна весу младшего разряда счетчика 45. Это ступенчатое напряЖение с выхода преобразователя 47 поступает на вход элемента 44 сравнения. В результате сравнения этого напряжения с измеряемым напряжением отсчета первого канала в момент равенства на выходе элемента 44 сравнения вырабатывается сигнал, устанавливающий в нуль триггер 42, который единичным выходом запирает элемент И 43 и останавливает прохождение импульсов с выхода хронизатора 1 на вход счетчика 45. При этом содержимое счетчика 45 соответствует цифровому эквиваленту аналогового сигнала первого канала К-го цикла преобразования. Одновременно импульсы с первого выхода преобразователя 5 поступают на счетные входы накапливающего 6 и вычитающего 7 счетчиков, разрядность которых гораздо меньше разрядности счетчика 45, поэтому с окончанием каждого цикла преобразования содержимое счетчика 6 соответствует лишь содержимому младших разрядов счетчика

45, а содержимое счетчика 7 равно разности младших разрядов значений отсчетов (К вЂ” 1)-го и К-го циклов преобразования.

По истечении максимального времени преобразования хронизатор 1 на втором выходе вырабатывает сигнал, разрешающий сравнение в блоке 10 содержимого счетчика 7 и регистра 8 (анализ разности соседних отсчетов, полученных в (К вЂ” 1) -м и К-м циклах преобразования).

На фиг. 3 показан вариант функциональной схемы блока 10 для сравнения содержимого счетчика 7 и регистра 8. В зависимости от возможных комбинаций содержимого

1262553 счетчика 7 и регистра 8 блок 10 вырабатывает сигнал либо на первом, либо на втором выходах, согласно таблице (фиг. 3). На элементах И 23 — 30 и ИЛИ 31 — 34 блока 10 происходит поразрядное сравнение содержимого счетчика 7 и регистра 8. Когда значение разности соседних отсчетов К-го цикла преобразования не отличается от значения разности соседних отсчетов (К в 1)-го цикла преобразования данного канала, на первом выходе блока 10 формируется сигнал совпадения, увеличивающий содержимое счетчика 9 на единицу и через элемент ИЛИ

12, блок 13 задержки разрешающий запись содержимого счетчиков 6, 7 и 9 (младшие разряды отсчета К-го цикла преобразования, разность значений отсчетов (К вЂ” 1) -го и

1(-го циклов преобразоания и количество идущих подряд несущественных отсчетов, соответствующих К-му циклу преобразования) в блок 4 памяти по адресу первого канала.

В случаях, когда значение разности соседних отсчетов К-го цикла преобразования отличается от значения разности соседних отсчетов (К в 1)-го цикла преобразования данного канала, на втором выходе блока 10 формируется сигнал несовпадения, который через элемент ИЛИ 11 поступает на вход преобразователя 5 и через элементы

И 46 (фиг. 5) разрешает передачу цифрового кода существенного отсчета на выход устройства. Одновременно сигнал несовпадения с выхода элемента ИЛИ 11 поступает на входы блока 14 задержки и счетчика 9 (фиг. 4), где через элементы И 39 разрешает параллельную передачу кода количества идущих подряд несущественных отсчетов, соответствующих К-му циклу преобразования, на выход устройства. Сигнал, задержанный блоком 14, записывает в счетчик 9 единицу и через элемент ИЛИ 12 и блок 13 задержки переписывает содержимое счетчиков 6, 7 и 9 в блок 4 памяти по адресу, соответствующему первому каналу.

После этого на первом выходе хронизатора 1 (фиг. 2) вырабатывается сигнал, который поступает на входы коммутатора 2 и формирователя 3. Измеряемый аналоговый сигнал второго канала через коммутатор

2 поступает на вход преобразователя 5, а код номера канала передается с второго выхода коммутатора 2 на вход формирователя 3. Далее работа устройства повторяется для второго канала аналогично.

В случае, когда количество идущих подряд несущественных отсчетов больше, чем максимальное значение содержимого счетчика 9, происходит переполнение счетчика 9, на его старшем разряде появляется сигнал, который через элемент ИЛИ 11 поступает на входы преобразователя 5 и счетчика 9, и передает значение цифрового кода отсчета и количество идущих подряд несуществен5

1О

55 ных оосчетов данного канала, соответствующих этому циклу преобразования, на выход устройства. Далее этот же сигнал, задержанный блоком 14, записывает в счетчик 9 единицу, через элемент ИЛИ 12 и блок 13 задержки переписывает содержимое счетчиков 6, 7 и 9 в блок 4 памяти по адресу, соответствующему данному каналу.

В начале работы устройства замыканием ключа 19 «Пуск» (фиг. 2) хронизатор 1 очищает блок 4 памяти, устанавливает коммутатор 2, формирователь 3 и счетчик 9 в исходное состояние. Этот же сигнал, задержанный в элементе 22, через элемент ИЛИ

28 с выхода хронизатора 1 поступает на входы коммутатора 2, формирователя 3 и преобразователя 5. В конце работы при замыкании ключа 18 «Ост» сигнал устанавливает триггер 17 в нулевое состояние, запрещая прохождение импульсов с выхода генератора 15 через элемент И 16 на вход делителя

20 частоты.

Таким образом, предложенное устройство обладает большей информативностью, передавая на выход только существенные отсчеты входных сигналов и код числа идущих подряд несущественных отсчетов.

Формула изобретения

Устройство для передачи телеметрической информации, содержащее коммутатор, информационные входы которого являются входами устройства, хронизатор, первый выход которого и первый выход коммутатора соединены соответственно с первым управляющим и информационным Входами аналого-цифрового преобразователя, регистр, выходы которого соединены с соответствующими первыми информационными входами блока сравнения, и блок памяти, отличающееся тем, что, с целью повышения информативности, в него введены формирователь импульсов, счетчики, элементы ИЛИ и блоки задержки, объединенные управляющий вход коммутатора и первый управляющий вход формирователя импульсов подключены к первому выходу хронизатора, второй выход коммутатора соединен с вторым управляющим входом формирователя импульсов, выход которого соединен с управляющим входом блока памяти и первыми управляющими входами первого и второго счетчиков, выходы первого счетчика и первые выходы второго и третьего счетчиков соединены с соответствующими информационными входами блока памяти, выходы которого соединены с соответствуюгцими информационными входами первого, второго, третьего счетчиков и регистра, вторые выходы второго счетчика соединены с соответствующими вторыми информационными входами блока сравнения, первый выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен

1262553 непосредственно с вторым управляющим входом аналого-цифрового преобразователя, первым управляющим входом третьего счетчика и через первый блок задержки с первым входом второго элемента ИЛИ и вторым управляющим входом третьего счетчика, выход второго элемента ИЛИ соединен через второй блок задержки с вторыми управляющими входами первого, второго счетчиков и третьим управляющим входом третьего счетчика, второй выход третьего счетчика соединен с вторым входом первого элемента ИЛИ, второй выход хронизатора соединен с управляющим входом блока сравнения, второй выход которого соединен с вторым входом второго элемента ИЛИ и счетным входом третьего счетчика, третий выход хронизатора соединен с входами установки в исходное состояние коммутатора, формирователя импульсов, блока памяти и третьего счетчика, четвертый выход хронизатора соединен с тактовыми входами блока памяти и аналого-цифрового преобразователя, первый выход аналого-цифрового преобразователя соединен со счетными вхо10 дами первого и второго счетчиков, вторые выходы аналого-цифрового преобразователя и третьи выходы третьего счетчика являются соответствующими выходами устройства.

1262553

1262553

Редактор И. Николайчук

Заказ 5434/50

Составитель М. Никуленков

Техред И. Верес Корректор М. Шароши

Тираж 515 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4