Запоминающее устройство с контролем информации при записи

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Целью изобретения является повышение быстродействия и надежности устройства. Запоминающее устройство содержит накопитель, блок местного управления, блок контроля, регистр числа, распределитель импульсов , формирователь сигналов записи , элемент И и регистр адреса, дешифратор адреса, одновибрАтЪр, . формирователь выходнбйс сигназГов и с S5 триггер. Повышение быстродействия . (/) и надежности устройства обеспечивается за счет селекции информации при передаче и исключения останова при сбоях. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕа«УБЛИК (др 4 С 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

"«» г

» ч »

»

4Я

Cb

Ю

Ю е Д эР@

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1003151 (21) 3855317/24-24 (22) 03.01.85 (46) 07.10.86. Бюл. Р 37 (71) Рижское ордена Ленина производственное объединение ВЭФ им.В.И.Ленина

: (72) Т.А. Новикова, Ю.С, Студнев и Ф.А.Фукс (53) 681.327.6(088.8} (56) Авторское свидетельство СССР

У 1003151, кл. G 11 С 29/00, 1983.

„„SU„„3262574 А2 (54) ЗАПОИИНАКШЕЕ УСТРОЙСТВО С КОНТРОЛЕМ ИНФОРМАЦИИ ПРИ ЗАПИСИ (57) Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Целью изобретения является повышение быстродействия и надежности устройства. Запоминающее устройство содержит накопитель, блок местного управления, блок контроля, регистр числа, распределитель импульсов, формирователь сигналов записи, элемент И и регистр адреса, дешифратор адреса, одновибратЬр,, формирователь выходнйх сигнвНов и . триггер. Повышение быстродействия . и надежности устройства обеспечивается за счет селекции информации при передаче и исключения останова при сбоях. 1 ил.

1262574

10

2S

50

Изобретение относится к вычислительнойй технике и может быть использовано при построении запоминающих устройств.

Целью изобретения является повышение быстродействия и надежности устройства.

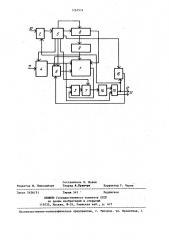

На чертеже представлена схема запо инающего устройства с контролем информации при записи.

Запоминающее устройство содержит накопитель 1, блок 2 местного управления, блок 3 контроля, регистр 4 числа, распределитель 5 импульсов, формирователь 6 сигналов записи, элемент И 7, регистр 8 адреса, дешифратор 9 адреса, входы 10 и 11, управляющий выход 12 .(результата .сравнения), информационные выходы 13, одновибратор 14, формирователь 15 выходных сигналов и триггер 16.

Устройство работает следующим образом.

Установка в исходное состояние при подаче питания производится выходным сигналом элемента И распре1 1 делителя 5, устанавливающего в процессе заряда RC-цепи начальное состояние на счетчике и дешифраторе распределителя 5 и регистра 8 адреса. Управляющие импульсы с входа 10 через блок 2 местного управления поступают на вход распределителя 5, работающего в режиме повторяющихся циклов. В течение каждого цикла распределитель 5 формирует сигнал переключения адреса и последователь- . ность команд анализа поступившей инфорации.

В начале цикла формируется сигнал переключения адреса, поступающий как импульс отсчета на вход регистра 8 адреса, младшие разряды с выхода которого поступают на адресные входы накопителя 1, а старшие — на вход дешифратора 9, формирующего сигналы обращепия к конкретному блоку памяти накопителя 1.

Бо втором такте цикла производится запись входной информации в регистр 4 числа и ее трансляция на информационные входы накопителя 1 и входы блока 3 контроля. При этом на выходе накопителя 1 присутствует информация, ранее записанная по адресу, поступившему из регистра 8.

Сравнение вновь поступившей (входной) информации и предыдущей (выходной) информации накопителя 1 производится в блоке 3 контроля в течение этого же второго цикла.

Третьим тактом цикла разрешается трансляция результата сравнения через элемент И 7 на вход одновибратора

14 и далее через формирователь 15 выходных сигналов на выход 12 устройства. Если входная информация не совпадает с выходной, сигнал с выхода блока 3 контроля, транслируемый элементом И 7, запускает одновибратор

14, сигнал с выхода которого разрешает трансляцию информации с выходов регистра 4 числа на выходы 13 устройства. Таким образом, осуществляется передача не всей информации, записанной в накопителе 1, а только ее изменение.

Результат сравнения (сигнал о несовпадении информации) поступает на инверсный вход блока 2 местного управления, запрещая поступления уп- . равляющих импульсов в распределитель 5. Таким образом. обеспечивается его остановка и прекращается анализ на время передачи. Помимо этого сигнал о несовпадении информаций поступает на управляющий вход триггера 16, который, срабатывая формирует сигнал на вход формирователя 6 сигналов записи н разрешает прием импульса соответствующей команды из распределителя 5.

Результат сравнения, поступающий на вход 12 устройства, может использоваться как сигнал контроля или как сигнал, управляющий работой запоминающего устройства с источником передачи и приема информации.

Четвертым тактом цикла формируется команда записи, поступающая на информационный вход формирователя 6 сигналов записи, транслируемая вход- ным элементом И на выходные элементы

И формирователя 6 сигналов записи.

При совпадении информации о наличии команды записи с сигналом обращения к блоку памяти накопителя 1, поступающим с выходов дешифратора 9, на выходе одного из оконечных элементов

И формирователя 6 появляется команда записи входной информации в блок накопителя 1, т.е. входная информация, отличная от ранее записанной в 03Ó по данному адрес и переданная на выходы 13 устройства, записывается в накопитель 1 и появляется на его

1262574 выходах, что воспринимается блоком 3 контроля как совпадение информации.

Сигнал с выхода блока 3 снимается.

IIo окончании работы одновибратора

14 запрещается выдача информации íà 5 выходы 12 и 13 устройства, снимаются запрет с инверсного входа блока 2 местного управления и сигнал с управляющего входа триггера 16.

В результате под воздействием управляющего импульса формируется пят и такт цикла работы распределителя 5, устанавливающий триггер 16 в исходное состояние.

Следующий управляющий импульс фор-11 мирует следующий цикл работы распределителя 5 с анализом сигналов, поступающих по новому адресу, сформированному как двоичное число, большее предыдущего на единицу. 20

В случае возникновения сбоя по передаче информации, когда при несовпадении входной и выходной информаций накопителя 1 информации на выходах 13 и сигнал на выходе 12 устройства не появляются, триггер 16 остается в исходном состоянии, запись изменения информации в накопитель 1 не состоялась. Таким образом, в случае сбоя останова всего устрой- 30 ства не происходит, а информация передается при повторных обращениях к данному адресу.

Если при проведенном анализе входная и выходная информации накопителя 1 совпадают, сигнал на выходе блока 3 контроля не появляется, передача информации на выходы 13 устройства и запись информации в накопитель 1 не производятся, так как на 4О входе формирователя 6 сигналов записи отсутствует разрешающий сигнал с выхода триггера 16.

После 5-го такта поступающим управляющим импульсов открывается новый цикл работы, регистр 8 адреса переводится в новую адресную позицию, в которой устройство работает по описанному алгоритму.

Формула изобретения

Запоминающее устройство с контролем информации при записи, по авт.св. N- 1003151, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия и надежности устройства, в него введены одновибратор, формирователь выходных сигналов и триггер, причем Информационные выходы формирователя выходных сигналов являются информационными выходами устройства, управляющий выход указанного формирователя соединен с вторым входом блока местного управления, синхровходом триггера и явля-» ется управляющии выходом устройства, информационные входы формирователя выходных сигналов подключены к выходам регистра числа, а синхровход соединен с выходом однавибратора, вход которого подключен к выходу элемента И, адресные и управляющие входы накопителя соединены соответственно с выходами младших разрядов регистра адреса и выходами формирователя сигналов записи, вход разрешения которого подключен к выходу триггера, установочные входы регистра адреса и триггера соединены с соответствующими выходами распределителя импульсов.

1 2625.74

Составитель 0. Исаев

Техред А.Кравчук

Редактор И. Николайчук.1

Корректор С. Черни

Заказ 5436/51

Тираж 543

Подписное

ВЯИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород . ул. Проектная, 4