Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминакяцим устройствам с автономным контролем. Устройство содержит блоки памяти, формирователи 9 и 10 сигналов четности, формирователи 11 и 12 сигналов контрольного слова , блоки 13 и 14 сравнения, блок 15 обнаружения ошибок, дешифратор 16, блок 17 элементов И, блок 18 коррекции ошибок. Достигается упрощение устройства. Кроме того, за счет сокращения числа контрольных разрядов уменьшается емкость контрольной час ти памяти. 1 з.п. ф-лы, 4 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5в 4 С 11 С 29 00 Ъ ф(\ р „i gy g e

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К -ASTOPCHOMY СВИДЕТЕЛЬС ГВУ

И

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3869053/24-24 (22) 19.03.85 (46) 07.10.86. Бюл. 8 37 (72) Н.Д.Рябуха, С.В.Корженевский, В.Б.Жмыхов и Г.N.Òêà÷åâ (53) 681.327(088.8) (56) Авторское свидетельство СССР

У 1109809, кл. G 11 С 29/00, 1983.

Авторское свидетельство СССР

Ф 1115107, кл. С 11 С 29/00, 1983.

„„SU„„1262576 А 1 (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ABTOH0MHbIM КОНТРОЛЕМ (57) Изобретение относится к вычис- лительной технике, в частности к запоминакщим устройствам с автономным контролем. Устройство содержит блоки 1 -1 4 памяти, формирователи 9 и

44

10 сигналов четности, формирователи 11 и 12 сигналов контрольного слова, блоки 13 и 14 сравнения, блок 15 обнаружения ошибок, дешифратор 16, блок 17 элементов И, блок 18 коррекции ошибок. Достигается упрощение устройства. Кроме того, за счет сокращения числа контрольных разрядов уменьшается емкость контрольной час- Я

8 ти памяти. 1 з.п. ф-лы, 4 ил.!

262576

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. !!ель изобретения — упрощение устройствае

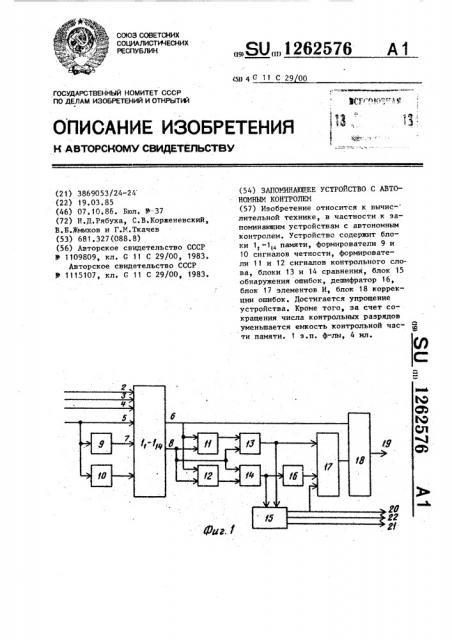

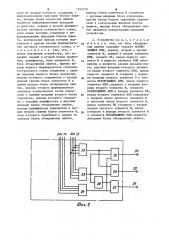

На фиг. 1 представлена функциональная схема запоминающего устройства с авт ономным контролем, на фиг. 2 — функциональная схема блока обнаружения ошибок, на фиг. 3 — функциональная схема части блока элементов И и части блока коррекции, на фиг. 4 — Н-матрица используемого корректирующего кода.

Устройство содержит блоки 1 -1, памяти с адресными входами 2, входамц 3 записи, входами 4 считывания, информационными входами 5 и информационнымп выходами 6, контрольными входами 7 и .выходами 8, первый 9 и второй 10 формирователи сигналов четности, первый 11 и второй 12 формирователи сигналов контрольного слова, первый 13 и второй 14 блоки сравнения, блок 15 обнаружения ошибок, дешифратор 16, блок элементов

И 17, блок 18 коррекции ошибок, информационные выходы 19 устройства, первый 20, второй 21 и третий 22 контрольные выходы устройства.

Блок 15 обнаружения ошибок(фиг.2) содержит первый 23 и второй 24 элементы ИЛИ, первый 25, второй 26 и третий 27 элементы И, элемент НЕ 28 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 29.

Блок 18 коррекции ошибок содержит сумматоры по модулю два, число которых равно количеству информационных разрядов блоков памяти.

Предположим, что каждый блок памяти предназначен для хранения четырех разрядов слова. Поскольку в качестве примера взято запоминающее устройство, имеющее четырнадцать блоков памяти, то слово состоит из пятидесяти шести разрядов, причем 48 из них информационные и 8 контрольные, Порядок соединения входов 2 с входами формирователей 9 и 10, а также выходов блоков 1 -1, с входами формирователей 11 и 12 определяются

Н-матрицей, структура которой приве" дена на фиг. 4, где обозначены информационные I -Iqg разряды блоков

1„ -1, памяти и контрольные ?ш-Х разряды блоков 1, и 1, памяти, а также сигналы четности С, -С формиров. 1телей 9 и 10 и сигналы контроль5

55 ного слова К,-К формирователей 11 и 12.

Формирователи 9-12 построены по параллельно-последовательной схеме на сумматорах по модулю два.

Блоки 13 и 14 сравнения содержат сумматоры по модулю два, причем в блоке 13 производится поразрядное сравнение сигналов четности С, -С4 с сигналами контрольного слова К, -К и на выходе соответствующих сумматоров по модулю два формируются сигналы сравнения (несравнения) Б -S . В блоке 14 производится порязрядное сравнение сигналов четности С -С с сигналами контрольного слова К„-К, и на выходе соответствующих сумматоров по модулю два формируются сигналы сравнения (несравнения) Я -S<

Дешифратор 16 построен по линей- ной схеме на элементах И и производит преобразование позиционного кода сигналов S>-$ в унитарный код.

Дешифратор 16 имеет двенадцать выходов.

Блок элементов И 17 содержит элементы И, их число равно числу информационных разрядов блоков памяти, причем выход каждого элемента И соединен с входом соответствующего сумматора по модулю два блока 18 коррекции ошибок, другой вход которого соединен с соответствующим информационным выходом блоков памяти.

Часть. блока элементов И 17 (фиг.3) содержит элементы И 30-33. Часть блоков 18 коррекции ошибок (фиг. 3) содержит сумматоры 34-3? по модулю два.

На фиг. 3 обозначены первые входы

В -В блока 18 коррекции ошибок, подключенные, например, соответственно к девятому-двенадцатому разрядам блоков памяти.

Устройство работает следующим образом.

При записи коды чисел по входам 5 поступают на информационные входы блоков 11 -1,, и на входы формирователей 9 и 10. Формирование сигналов четности С„ -С4 в формирователе 9 и сигналов четности С -С в формирователе 10 происходит в соответствии с

Н-матрицей кода (фиг. 4), которая указывает последовательность получения значений сигналов четности С -С

s режиме записи и определяет значение сигналов К -К8 контрольного слова в режиме считывания. Например, значение сигнала четности Сб равно .

1262576

3 сумме по модулю два значений информационных разрядов 1, 1„, I

I38, 1я, а значе ие разряда К6 контрольного слова также равно сумме по модулю два значений указанных информационных разрядов и разряда ? 4 блоков памяти.

При считывании информационные и контрольные разряды чисел из блоков

1, -1,4 поступают на входы формирователей 11 и 12, а на первые входы блока 18 поступают только информационные разряды чисел. Формирователь 11 формирует разряды К,-К4, а формирователь 12 — разряды К -К контроль- 15 ного слова. В блоке 13 происходит сравнение сигналов контрольного слова К;-К4 и сигналов четности С,-С4, считанных из разрядов 149-1 2 блоков памяти. С выходов первого блока 13 20 сравнения сигналы сравнения (несравнения) Я -Я4 поступают на первые входы блока элементов И 17 и блока

15 обнаружения ошибок. В блоке 14 происходит сравнение сигналов конт- 25 рольного слона К,-К и сигналов четночти С вЂ .С, считанных из разрядов

15 Irg бл к в памя 1и

С выходов блока 14 сигналы сравнения (несравнения) Я -S< .поступают ЗО на входы дешифратора 16 и на вторые, входы блока 15 обнаружения ошибок.

Дешифратор 16 преобразует двоичный позиционный код сигналов S -S в

Унитарнь|й Номера Отказавших разря 5 дов одного из блоков памяти указывают сигналы S -S а номер отказавшего блока памяти — сигналы Я -Я .

Пусть, например, возникла пакетная ошибка в девятом-двенадцатом разря- 40 дах,, эти разряды относятся к третьему блоку памяти. Предположим, что значения сигналов четности С -C> равны нулю. В соответствии с Н-матрицей формируются следующие значения 45 разрядов контрольного слова: К =1, К21, К =1, К4=1, .К =О, К =О, К -1

К8=1 После сравнения их с контрольными разрядами С -С> получают S S2=

5О

Сигналы Я -Я (принимая Я за младший разряд) образуют двоичное число 0011, соответствующее третьему блоку памяти, т.е. тому блоку памяти, в котором произошла пакетная ошибка.

При поступлении этого кода на вход,. дешифратора 16 на его третьем выходе формируется единичный сигнал, который поступает на входы элементов И

30-33 (фиг. 3). На остальные входы этих элементов поступают единичные сигналы Я -$4 и единичный сигнал разрешения коррекции, сформированный в блоке 15 обнаружения ошибок. При совпадении всех трех единичных сигналов на выходах элементов И 30-33 формируются единичные сигналы коррекции, поступающие на входы сумматоров 3437 по модулю два блока 19 коррекции пакетных ошибок. При,этом происходит сложение по модулю два значений инфОрмационных разрядов ?9 1,2 и IIocTjj пивших единичных сигналов. Таким образом происходит коррекция пакетных ошибок.

В блоке обнаружения ошибок формируются сигналы разрешения коррекции, сигнал обнаружения двойного пакета ошибок и сигнал некорректируемой ошибки.

Элемент И 26 реализует контроль на наличие пакетной корректируемой ошибки. Наличие единичного сигнала на выходе элемента ИЛИ 24 и отсутствие единичного сигнала на выходе элемента ИЛИ 23 свидетельствует о возникновении двойного пакета ошибок и элемент И 27 формирует сигнал обнаружения двух пакетов ошибок.

Элемент ИСКДОЧЛЮЩЕЕ ИЛИ 29 формирует сигнал о некорректируемой.ошибке, которая обнаруживается по наличию на выходе элемента И 25 нулевого сигнала и единичного на выходе элемента ИЛИ 23. При отсутствии ошибок сигналы Я -S> равны нулю, сигналы коррекции также равны нулю и информационные сигналы на выход блока 18 коррекции ошибок выдаются без измвнения.

Формула изобретения

Запоминающее устройство с asтономным контролем, содержащее блоки памяти, адресные входы, входы записи и входы считывания которых являются соответственно первым, вторым и третьим входами устройства, первый и второй формирователи сигналов чегности, выходы которых подключены к контрольным входам блоков памяти, информационные взводы которых и входы формирователей сигналов четности обьединены и являются четвертым входом устройства, блок коррекции ошибок, 5 12625 одни из входов которого соединены с информационными выходами блоков памяти, выходы блока коррекции ошибок, являются информационными выходами устройства, первый и второй формирователи сигналов контрольного слова, одни входы которых соединены с информационными выходами блоков памяти, контрольные выходы которых подключены к другим входам формирователей сигналов контрольного .слова, о тл и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит первый и второй блоки сравнения, дешифратор, блок элементов И, блок обнаружения ошибок, причем выходы первого формирователя сигналов контрольного слова, соединены с одними входами первого блока сравнения, выходы которого подключены к входам первой группы блока элементов И и одним входам блока обнаружения ошибок, выходы второго формирователя сигналов контрольного слова соединены с одними входами второго блока д5 сравнения, выходы которого соединены с входами дешифратора и другими входами блока обнаружения ошибок, выходы дешифратора подключены к вход м второй группы блока элементов И, 30 о вход которого. подключен к одному из выходов блока обнаружения ошибок, 76 d выходы блока элементов И соединены с другими входами блока коррекции, другие входы блоков сравнения подключены к контрольным выходам блоков памяти, выходы блока обнаружения ошибок являются контрольными выходами устройства.

2 ° Устройство по п.1, о т л и ч аю щ е е с я тем, что блок обнаружения ошибок содержит элемент ИСКЛЮЧАКЩЕЕ ИЛИ, первый, второй и третий элементы И, первый и второй элементы

ИЛИ, элемент НЕ, входы первого элемента И и первого элемента ИЛИ объединены и являются одними входами блока, другими входами которого являются входы второго элемента ИЛИ, выход первого элемента И соединен с первыми входами второго элемента И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента ЮТИ соединен с вторыми входами второго элемента И, элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ и входом элемента HE выход второго элемента ИЛИ подключен к первому входу третьего элемента И и третьему входу второго элемента И, выход элемента НЕ соединен с вторым входом третьего элемента И, выход которого и выходы второго элемента И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами блока обнаружения ошибок.

1262576 g 5 -77 J 4/ Ъ Ъ Ъ Ъ Ь 4 3 Ъ 17 2У Ъ

Ъ 4 4 4 4 0 Ъ 4 f8 4 8 Ъ Ъг Ъ4 26 7гВ Ъ Ъ с к сг кг с к с4 "4 св кв

47 ку

С0 "б

Сб Кб

Фиг,4

Редактор И.Николайчук

Заказ 5436/51 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предпрйятие, г. Ужгород, ул. Проектная, 4 4

B txodГ

om /б

omВ 52

Выход ат Я ат/5

8у

Выход ал/о ото

Выход

om/о

omВ

Составитель О.Кулаков

Техред А.Кравчук Корректор- E.Ñèðîõìàí