Логический элемент на кмдп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может использоваться при разработке универсальных и спе- , циализированных интегральных схем на комплементарных МДП-транзисторах. Цель изобретения - повьщение надежности логического элемента (ЛЭ) - достигается уменьшением числа используемых транзисторов. ЛЭ содержит р -канальные транзисторы 1-4, П-канальные транзисторы 5-9, образующие четыре пары последовательно включенных транзисторов 1 и 2, 3 и4, 5и6, 7и8, вькодную 10, шины 11 и 12 питания, входные шины 13 и 14, узлы 15 и 16, в которых реализуется инверсия логических переменных А-А и В-В соответственно. На чертеже показана схема ЛЭ НЕРАВНОЗНАЧНОСТЬ . В описании изобретения с приводится схема ЛЭ РАВНОЗНАЭДОСТЬ. (Л 4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) Ai (58 4 Н 03 К 19 094

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Ъ

Ф

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А9ТОРСКОМУ СВИДЕТЕЛЬСТВУ (21 ) 383 5348/24-21 (22) 03.01.85 (46) 07,10.86. Бюл. 11- 37 (72) С.В.Ильин, С.E.Калинин, А.И.Березенко и Л.Н.Корягин (53) 621.374 (088.8} (56) Авторское свидетельство СССР

Ф 1008909, кл. Н 03 К 19/02, 1981.

Патент США В 4006365, кл. Н 03 К 19/08, 1977. (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДПТРАНЗИСТОРАХ (57} Изобретение относится к импульсной технике и может использоваться при разработке универсальнык и специализированных интегральных схем на комплементарных МДП-транзисторах.

Цель изобретения — повышение надежности логического элемента (ЛЭ) достигается уменьшением числа используемых транзисторов, ЛЭ содержит р -канальные транзисторы i 4, ))-канальные транзисторы 5-9, образумцие четыре пары последовательно включенных транзисторов 1 и 2, 3 и 4, 5 и 6, 7 и 8, выходную шину 10, шины ll и 12 питания, входные шины

13 и 14, узлы 15 и 16, в которых реализуется инверсия логических пере-. менных А-А и В-В соответственно, На .чертеже показана схема ЛЭ НЕРАВНОЗНАЧНОСТЬ. В описании изобретения приводится схема ЛЭ РАВНОЗНАЧНОСТЬ.

4 ил.

1262721

Изобретение относится к импульсной технике и может быть использовано при разработке универсальных и специализированных интегральных схем на комплементарных МДП-транзисторах.

Цель изобретения — повышение надежности логического элемента.

Поставленная цель достигается уменьшением числа используемых транзисторов °

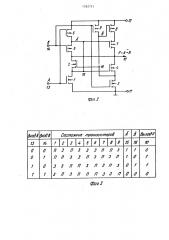

На фиг.! представлена электрическая принципиальная схема логическо—

ro элемента НЕРАВНОЗНАЧНОСТЬ; на фиг.2 — то же, логического элемента

РАВНОЗНАЧНОСТЬ; на фиг.3 — таблица истинности логического элемента НЕРАВНОЗНАЧНОСТЬ; на фиг. 4 — то же, логического элемента РАВНОЗНАЧНОСТЬ.

Логический элемент содержит рканальные (фиг.1) или и -канальные (фиг.2) транзисторы 1 — 4, и -канальные (фиг.1) или р †канальн (фиг.2) транзисторы 5 — 9, образующие четыре пары последовательно включенных транзисторов 1 и 2, 3 и

4, 5 и 6, 7 и 8, стоки транзисторов

2,4,5 и 7 подключены к выходной шине 10 истоки транзисторов 1 и 3 подключены к шине 11 питания, исто- ки транзисторов 6,8 и 9 подключены к второй шине 1 2 питания, сток транзистора 9 подключен к затворам транзисторов 2 и 8 и к стоку транзистора

3, затворы транзисторов 1 и 6 подключены к первой входной шине 13, затворы транзисторов 3,5 и 9 подключены к второй входной шине 14.. На входную шину 13 поступает логическая переменная ", на шину 14 — логическая переменная В, в узле 15 реализуется инверсия логической переменной А-А, в узле 16 — инверсия логической переменной В-В.

Логический элемент НЕРАВНОЗНАЧНОСТЬ (фиг.1) работает в соответствии с таблицей истинности (фиг.3).

В таблице истинности низкому и высокому уровням сигналов соответствуют .логические "0" и "1" обозначения 11. и 3 соответствуют состояниям транзисторов, когда они проводят (11) и когда закрыты {Э). Во второй строке таблицы истинности приведены подчиненные номера транзисторов, соответствующие фиг,1.

При А = 0 и В = 0 уровень логического 0 на выходе F устанавливается через проводящие транзисторы 7 и 8, при А = I и В = 1 — через транзисторы 5 и 6.

При А 0 и В = 1 уровень логи5 ческой "1" на выходе F устанавливается через проводящие 1 и 2, при A = 1 и В = 0 — через транзисторы 3 и 4.

Логический элемент РАВНОЗНАЧНОСТЬ (фнг.2)работает в соответствии с

1О таблицей истинности (фиг,4).

При А = 0 и В = 0 уровень логи-. ческой 1 на выходе F устанавливается через проводящие транзисторы

5 и 6, при А = 1 и В = 1 — через !

5 транзисторы 7 и 8.

При А = О и В = 1 уровень логического "0 на выходе F устанавливается через проводящие транзисторы .

3 и 4, при А = 1 и В = 0 — через проводящие транзисторы 1 и 2.

Формула изобретения

25 Логический элемент на КМДП-транзисторах, содержаший, первый, второй, третий и четвертый транзисторы с каналами проводимости первого типа и пятый, шестой, седьмой, восьЗо мой и девятый транзисторы с каналами проводимости второго типа, стоки второго, четвертого, пятого и седьмого транзисторов подключены к выходной шине, а их истоки — соответ35 ственно к стокам первого, третьего, шестого и восьмого транзисторов, истоки первого и третьего транзисторов Iloäêëþ÷åíû к первой шине питания ! истоки шестого, восьмого и девятого транзисторов подключены к второй

40 шине питания, сток девятого транзистора подключен к затворам второго и восьмого транзисторов и стоку третьего транзистора, затвор первого тран45 зистора подключен к первой входной шине, затворы третьего и девятого транзисторов подключены к второй входной шине, затворы четвертого и седьмого транзисторов подключены к стоку первого транзистора, о т л нч а ю шийся тем, что, с целью повышения надежности, затвор и сток шестого транзистора подключены соответственно к первой входной шине и стоку первого транзистора, а затвор пятого транзистора подключен к второй входной шине.

l26272l

1262721

Составитель А.Кабанов

Техред А.Кравчук

Корректор Л.Патай

Редактор A.Л!андор

Тираж 816 Подписное

ВНИИГИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Заказ 5446/58 дроизводственно-полиграфическое предприятие, r.Ужгород, ул.Проектная,4