Устройство для вычисления систем логических функций

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназначено для реализации систем логических функций. Цель изобретения - повышение быстродействия устройства. Поставленная цель достиг ается тем, что устройство содержит ш матриц памяти, два дешифратора, m групп элементов ИЛИ и m коммутаторов, две группы информационных входов, m выходов . При подаче переменных х, х на первую группу входов и переменных x., ) Xf, на вторую группу входов на выходах устройства реализуются логические функции f ... fm от п переменных. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК дц4 С 06 F 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, М

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

1Ц

»»» с чено для реализаьГли систем логических функций. Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство содержит ш матриц памяти, два дешифратора, ш групп элементов ИЛИ и ш коммутаторов, две группы информационных входов, ш выходов. При подаче переменных х, х„ на первую группу входов и переменных х„, х„ на вторую группу входов на выходах устройства реализуются логические функции f f„, от и переменных. 2 ил.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ll0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3875275/24-24 (22) 26.03,85 (46) 15.10.86. Бюл, У 38 (72) Л.Б. Авгуль, В.И. Бенкевич, В.А. Мищенко и А. П. Криницкий (53) 681.3(088.8) (56) Авторское свидетельство СССР

У 962918, кл. G 06 F 7/00, 1981.

Авторское свидетельство СССР

У 1119004, кл. G 06 Р 7/00, 1983. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИСТЕМ ЛОГИЧЕСКИХ ФУНКЦИЙ (57) Изобретение относится к области вычислительной техники и предназна„„SU„„1264160 А 1

1.264160

l0

Изобретение относится к вычислительной технике и предназначено для реализации систем логических функций, описывающих работу цифровых преобразователей.

Цель изобретения — повышение быст— родействия устройства для вычисления систем логических функций.

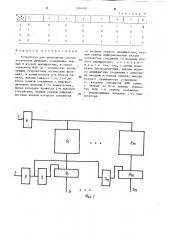

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 — функциональная схема устройства для рассматриваемого примера, Устройство содержит первую 1 и вторую 2 группы информационных входов, m (по числу реализуемых устройством логических функций) выходов 3 -3 „ первый 4 и второй 5 дешифраторы, m матриц памяти 6, — 6 „

m групп элементов ИЛИ 7, — 7„„ и m коммутаторов 8, — 8,„.

Первая 1 и вторая 2 группы информационных входов устройства соединены с входами первого 4 и второго

5 дешифраторов соответственно. Выходы первого дешифратора 4 соединены с адресными шинами матриц памяти

61 — 6, выходы которых соединены с информационными входами коммутаторов 8 — 8,„ соответственно. Выходы второго дешифратора 5 соединены с входами элементов ИЛИ 7 — 7„,, выходы которым соединены с управляющими входами коммутаторов 8 — 8, соответственно..Выходы коммутаторов 8 — 8щ являются выходами устройства 3 — 3 .

Устройство работает следующим образом.

Система m логических функций и переменных f<(х,,х,„), i=1,m разлагается по Шенному по к (к (n) переменным х,, х„ на функции и-к переменных { 11 (х„,х,„) . Таким образом, .1 в и ° к каждой функции f соответствует 2 функций Й

Функции Й размещаются в памяти так, что каждая из них занимает одно слово (строку) в i — и матрице памяти. Очевидно, одноименным разрядам S (S=1,2" к) функций ф П (x „+< x„) и (j = 1,2) будут соответствовать булевы функции $.Я (х, х„), каждая из которых занимает S-й столбец в i-й матрице памяти. Следовательно, переменные х„,,х„ определяют функцию +;4 в i-й матрице, а переменные х, х, — значение выбранной функции которое совпадает со значением функции f; (х,, x,„) на данном наборе переменных х, х

Если переменные х, х„ подать на первый дешифратор, выход которого подключить к адресным шинам матриц памяти, переменные х ...,х„ подать на второй дешифратор, выход которого подключить к управляющим входам коммутаторов, информационные входы которых соединить соответственно с выходами матриц памяти, то на выходе коммутаторов реализовываются функции f,(х,,х,„) .

Однако, с целью уменьшения anna— ратурных затрат все попарно тождественные зункции Ч, =Ч,g (S = 1,2" ", f. = 1,2" ", SP1) которым соответствуют сигналы на S=M и Г=м вьиодах второго дешифратора, размещаются в памяти так, чтобы они занимали один столбец. Тогда соответствующий управляющий вход коммутатора подключается к выходу элемента ИЛИ, входы которого соединяются с S--M и 1=м выходами второго дешифратора.

Более подробная работа предлагаемого устройства рассмотрена на примере реализации системы трех булевых функций пяти переменных (табл.1), а функциональная схема устройства для рассматриваемого примера приведена на фиг.2.

Разложим и (x,,õ ) по к=2 переменным (таб.л.2).

Очевидно, .Чм= Ч, =Ч щ = Й (х1,х ); 1 = 4 gq — Е 2 (Х 1, х );

Ч<5 17 f )(x 1, э х ) ь Y„= и (х, хр) .

Следовательно, функции Ч „, Ф„, 1; размещаются в одном столбце первой матрицы памяти 6> выход которого подклю ается к информационному входу коммутатора 8„, соответствующий управляющий вход которого подключен к выходу элемента ИЛИ группы 7, входы которого соединены с первым, вторым и восьмым выходами второго дешифратора 5.

Функции Ч „ и Ч„, Ф, и Ч, также занимают по одному столбцу в матрице памяти 6, . Соответствующие управляющие входы коммутатора 8 также соединяются с выходами элементов ИЛИ группы 7

Поскольку функция Ф, не имеет тождественной функции, то соответствую1264160

Таблица 1

0 0 щий ей управляющий вход коммутатора

8 непосредственно соединен с шестым выходом второго дешифратора 5.

Логические функции 2 и 1 реа лиэуются аналогично. х х х xq

Таким образом, при подаче переменных х,, х„ на входы 1 первого дешифратора 4 и переменных х„,, х„ на входы 2 второго 5 дешифратора на выходах 3,— З,неустройства реализуются логические функции (— „соответственно.

1 264160 1

:4

2 1

3. 0

4 0

) 2 (3 4 ) Та блица 2

1 О

0 1 о

25

Формула изобретения

Устройство для вычисления систем логических функций, содержащее первый и второй дешифраторы, m групп элементов ИЛИ (m — количество реализующих устройством логических функций), m коммутаторов и m блоков памяти, выходы каждого i-го (i=1 т) блока памяти соединены с информационными входами i-го коммутатора, выход которого является i-и выходом устройства, первая групга информационньгх входов которого соединена со входами первого дешифратора, вторая группа информационных входов устройства соединена со входами второго дешифратора, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия, выходы первого дешифратора соединены с адресными входами m блоков памяти, выходы второго дешифратора соединены со входами элементов ИЛИ групп с первой по vA -ю выходы элементов ИЛИ -й группы соединены с управляющими входами — гс коммутатора.

1264) 60

Составитель О. Береэикова

Техред Корректор М.Пожо

Редактор Т. Митейко

Заказ 5562/48 Тираж 671 По дпис н ое

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035s Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул . Проектная, 4