Накапливающий сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах ЭВМ и устройствах цифровой автоматики. Цель изобретения - повышение быстродействия . Накапливающий сумматор в каждом разряде содержит три RS-триггера , девять элементов И, четгфв элемента ИЛИ и шины управления работой сумматора. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (I9) (Ш

А1 (5ц 4 G 06 Р 7/50

ГОСУДАРСТВЕННИКИ HOMHTET СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

«., а Рр

ОПИСАНИЕ ИЗОБРЕТЕНИЯ: лМ.

Ф ф h

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3868083/24-24 (22) 07.01.85 (46) 15.10.86. Бюл. У 38 (72) Б..И. Власов и С.Т. Гузеев (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР

II 911517, кл. G 06 F 7/50, 1979.

Авторское свидетельство СССР

Р 11t2363, кл. С 06 Р 7/50, 1983. (54) НАКАПЛИВАКЩИЙ СУММАТОР (57) Изобретение относится к цифровой вычислительной технике и макет быть использовано в процессорах ЭВ1Ф и устройствах цифровой автоматики.

Цель изобретения — повышение быстродействия. Накапливающий сумматор в каждом разряде содержит три RS-триггера, девять элементов И, четыре элемента ИЛИ и шины управления работой сумматора. 1 ил.

i 264165

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ и цифровым устройствам автоматики.

Цель изобретения — повышение быстродействия накапливающего сумматора.

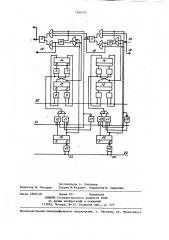

На чертеже представлена функциональная схема двух разрядов накапливающего сумматора.

Сумматор содержит в каждом разряде элементы ИЛИ 1-4, элементы И 513, триггеры 14-16, элемент НЕ, 17, выход 18 переноса в следующий разряд и выход 19 ускорения переноса в следующий разряд. Кроме того, сумматор содержит шину 20 управления пересылкой кода, шину 21 управления сложением, шину 22 разрежения приема кода и информационные входы 23.

Рассмотрим работу сумматора при выполнении операции сложения двух положительных чисел, представленных в двоичном коде. Будем считать,что код первого слагаемого хранится в триггерах 14, а код второго слагаемого поступает в сумматор с входов

23. Триггеры 16 приемного регистра предварительно установлены в нулевое состояние или прием информации в этот регистр осуществляется парафазным кодом.

По первому временному такту Ct ) выполняются элементарные операции (ЭО) приема кода второго слагаемого в приемный регистр (триггеры 16) и пересылка кода первого слагаемого, хранящегося в триггерах 14, в триггеры 15. Для выполнения этих двух

Э0 на шины 20 и 22 одновременно подаются исполнительные импульсы.

Если в триггере 14 хранится код единицы, то исполнительный импульс через элемент И 9 поступает íà Sвход триггера 15 и установит его в единичное состояние. Если же в триггере 14 хранится код нуля, то исполнительный импульс через элемент И 8 поступает на R-вход триггера 15 и устанавливает его в нулевое состояние. После завершения выполнения этой ЭO в триггерах l4 и 15 будут храниться одинаковые коды.

Если на шине 23 разряда имеется высокий (низкий) потенциал, соответствующий коду единицы, то исполнительный импульс через элемент И 12 поступает на Я-вход триггера 16 и

1О

50 устанавливает его в единичное состояние. Если на шине 23 отсутствует потенциал, соответствующий коду единицы, то триггер 16 установлен в нулевое состояние.

После переключения триггеров 15 и 16 создаются условия для формирования и распространения сигнала сквозного переноса.

В тех разрядах сумматора, в которых триггеры 14-16 хранят единицы на шине 18 формируется потенциал переноса. Этот потенциал формируется за счет логических элементов ИЛИ 1,2 и И 5. В данном разряде задержка сигнала переноса равна 2t.

Если в следующем разряде в триггере 16 или 15 будет храниться единица, то сигнал переноса, поступивший по шине 18 из младшего разряда, через элемент И 13 поступает на вход элемента ИЛИ 2 данного разряда и одновременно на элемент ИЛИ 1 старшего разряда. Таким образом, в данном разряде задержка сигнала переноса будет только, где — задержка логических элементов И и ИЛИ.

После завершения формирования максимального сквозного переноса, по третьему временному такту (t ) выполняется формирование результата сложения двух кодов за счет подачи на шину 21 исполнительного импульса. Если в рассматриваемом разряде код, хранящийся в триггере 16, и сигнал переноса, поступивший из младшего разряда с выхода 18, равны единице или нулю, т.е. одинаковы, то исполнительный импульс не проходит на счетный вход триггера

l4 и в данном разряде состояние триггера НЕ 14 меняется. Если же код триггера 16 и значение потенциала переноса, поступившего из младшего разряда, не совпадают,то исполнительный импульс по цепи .элементов И 11, ИЛИ 3 поступает на входы .элементов И 6 и 7 и инвертирует состояние триггера 14.

Формула изобретения

Накапливающий сумматор, содержащий в каждом разряде три триггера, три элемента ИЛИ и восемь элементов И, причем первый вход первого элемента И соединен с шиной управления приемом кода в сумматор, второй

1264165 вход соединен с информационным входом данного разряда сумматора, а выход первого элемента И подключен к

S-входу первого триггера, единичный выход которого соединен с первым 5 входом первого элемента ИЛИ и с первым входом второго элемента И, второй вход которого соединен с шиной управления отношением сумматора, а выход второго элемента И подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выход второго элемента ИЛИ соединен с первыми входами четвертого и пятого элементов И, вторые входы которых соединены соответственно с одиночным и нулевым выходами второго триггера, R- u S-входы которого соединены с выходами соответственно шестого и 20 седьмого элементов И, первые входы которых соединены с шиной управления пересылкой кода сумматора, а вторые входы соединены соответственно с нулевым и единичным выходами 2> третьего триггера, R- u S-входы которого соединены с. выходами соответственно четвертого и пятого элементов И, первый и второй входы третьего элемента ИЛИ подключены со- 30 ответственно к выходу переноса и к выходу ускорения переноса предыдущего разряда сумматора, первый вход третьего элемента И соединен с первым входом третьего элемента ИЛИ, выходы первого и третьего элементов ИЛИ подключены к соответствующим входам восьмого элемента И, выход которого соединен с выходом переноса данного разряда сумматора, отличающийся тем, что, с целью повышения быстродействия, сумматор дополнительно содержит четвертый элемент ИЛИ, девятый элемент И и элемент НЕ, причем третий вход второго элемента И соединен с выходом элемента НЕ, вход которого соединен с первым входом третьего элемента И, второй вход которог:о подключен к нулевому выходу первого триггера, а третий вход соединен с шиной управления сложением сумматора, второй вход первого элемента ИЛИ соединен с выходом ускорения переноса данного разряда и с выходом девятого элемента И, первый вход которого подключен к выходу четвертого элемента ИЛИ, второй вход девятого элемента И соединен с первым входом третьего элемента ИЛИ, третий вход которого соединен с первым входом четвертого элемента ИПИ и с единичным входом второго триггера, второй вход четвертого элемента ИЛИ соединен с единичным выходом первого триггера.

Составитель А. Степанов

Редактор И. Касарда Техред И.Ходанич Корректор Е. Сирохман

Заказ 5562/48 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открмтий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полигра4ийеское предприятие, г. Ужгород, ул. Проектная,4