Цифровой коррелятор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной Технике и предназначено для корреляционной обработки сложных сигналов в задачах гидролокации, вигации, командоуправления и передачи информации. Цель изобретения повьшение быстродействия. Сущность изобретения заключается в использовании для достижения поставленной цепи принципа обработки по частям. Общий объв выборок принимаемого сигнала делится на равные части, обрабатьшаемыёпараллельно во времени. Для реализации этого принципа устройство дополнительно содержит второй элемент задержки, одновибратор, второй и третий счетчики с соответствующими функ1щональньв4и связями между ними и известными блоками корСО релятора . 1 ил. С to

4200 А 1

11Ю (11) tgg 4 С 06 F 15/336

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТНЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТЙРЫТЬФ, (21) 3790393/24-24 (22) 01 ° 08.84 (46) 15.10.86. Бюл. У 38 (71) Одесское отделение Морского гидрофиэического института АН УССР (72) В.К.Богушевич, М.И.Скила и А.В.Холопцев (53) 681.33(088.8) (56). Авторское свидетельство СССР

В 940172, кл. С 06 F 15/336, 1980.

Авторское свидетельство СССР

Ф 959091, кл. G 06 Р 15/336, 1980.

Авторское свидетельство СССР

Ф 1096656, кл. G 06 F 15/336, 1983. (54) ЦИФРОВОЙ КОРРЕЛЯТОР (57) Изобретение относится к вычислительной технике и предназначено для корреляционной обработки сложных сигналов в задачах гидролокации, навигации, командоуправления и пере-. дачн инФормации. Цель изобретения— повышение быстродействия. Сущность изобретения заключается в использовании для достижения поставленной цели принципа обработки по частям.

Общий объем выборок принимаемого сигнала делится на равные части, обрабатываемые параллельно во времени.

Для реализации этого принципа устройство дополнительно содержит второй элемент задержки, одновибратор, . второй и третий счетчики с соответствующими функциональньаии связямн между ними и известными блоками коррелятора. 1 ил.

1264200 2

С выхода генератора 12 тактовые импульсы поступают на вход счетчика

4 и через элемент И 11 — на вход счетчика 9. Весь процесс вычисления одного значения функции корреляции происходит 3a (N/n) + 1 тактов. Последовательное изменение состояний счетчиков 4 и 9, адресные выходы которых соединены с адресными входами элементов 3 и 8 памяти, обеспечивает

55

Изобретение относится к вычислительной технике, предназначено для корреляционной обработки сложных сигналов, и может быть использовано в системах навигации, командоуправления и передачи информации.

Цель изобретения — повышение быстродействия.

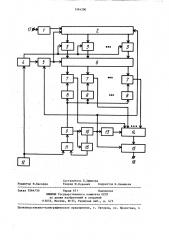

На чертеже представлена структурная схема цифрового коррелятора. 10

Коррелятор содержит аналого-цифровой преобразователь 1, второй коммутатор 2, первую группу элементов 3 памяти, третий счетчик 4, второй счетчик 5, первый коммутатор 6, 15 группу блоков 7 умножения, вторую группу 8 элементов памяти, первый счетчик 9, второй элемент 10 задержки, элемент И 11, г.енератор 12 тактовых импульсов, первый элемент 13 20 задержки, сумматор 14, регистр 15, одновибратор 16, информационный вход 17 коррелятора, выход 18 коррелятора.

1 абота коррелятора основана на принципе обработки сигнала "no частям", который заключается в делении общего числа выборок принимаемого сигнала (и соответственно опорного) на 1 равных частей и обработке этих 30 частей одновременно, параллельно во времени. При этом операция вычисления одного значения функции корреляции, заключающаяся в нахождении суммы произведений всего числа выборок.

35 принимаемого и опорного сигналов, заменяется операцией одновременного нахождения сумм произведений отдельных частей общего числа выборок принимаемого и опорного сигналов с пос40 ледующим суммированием получаемых частных результатов. В этом случае время обработки всего сигнала определяется временем обработки отдельной его части и не зависит от количест45 ва обрабатываемых параллельно частей.

Коррелятор работает следующим образом. последовательное извлечение информации из них, т. е. рециркуляцию частей принимаемого и опорного сигналов.

Счетчики 4 и 9 имеют равное число рабочих состояний (N =- N/n), определяющих соответственно число используемых элементов 3 и 8 памяти. С выхода счетчика 4 сигнал поступает на первый (суммирующий) вход счетчика 5.

Этот счетчик имеет число рабочих состояний, равное числу элементов 3 памяти и указывает номер элемента, в котором хранится предыдущая выборка сигнала. Счетчик 5 совместно со счетчиком 4 фактически представляет собой счетчик адреса всех элементов 3 памяти, используемых для хранения принимаемого сигнала. С управляющего выхода счетчика 9 на его N ì рабочем такте (импульс переноса) сигнал поступает на входы элемента 10 задержки и одновибратора 16. На следующем N + 1-м такте генератор 12 тактовых импульсов через элемент 10 задержки подает сигнал на вход разрешения вычитания счетчика 5. На этом же такте одновибратор 16 подает сигнал на элемент И 11 и блокирует (запI рещает) прохождение N + 1-ro тактового импульса на вход счетчика 9.

Этим достигается сдвиг в течение цикла корреляции на единицу нумерации элементов 3 памяти относительно нумерации элементов 8 памяти, т.е. эффект "продвижения принимаемого сигнала относительно опорного. За время цикла корреляции счетчик 9 последовательно изменяет свои состояния от 1-го до N -го и опять приходит в 1-е состояние.

Счетчик 4 за это время изменяет свое состояние от начального r-го ( до N --ro, далее 1-ro и в конце цикла корреляции приходит в r + 1-е ! состояние. На этом N + 1 такте через элемент 10 задержки подается сигнал на управляющий вход регистра

15; осуществляется выдача вычисленного значения функции корреляции.

Подается сигнал на вход элемента 13 задержки, а через него — на управляющий вход сумматора 14, осуществляя обнуление последнего и подготовку к работе в новом цикле корреляции.

Подается сигнал на тактовый вход коммутатора 2, производя запись новой выборки принимаемого сигнала в соответствующий элемент 3 памяти.

3 1264

После завершения процесса записи нбвой выборки принимаемого сигнала задним фронтом тактового импульса счетчик 4 переводится в новое состояние. Коммутатор 6 обеспечивает подключение выхода элементов 3 памяти к первому входу соответствующего блока 7 умножения, к второму входу которого подключены выходы элементов

8 памяти, хранящих выборки опорного ð сигнала-эталона. При этом коммутатор

6 работает таким образом, что всегда обеспечивает поступление в течение цикла корреляции (в процессе ре1 циркуляции) самых старых N выборок принимаемого сигнала (начало принимаемого сигнала) на вход первого блока 7 умножения группы, на второй вход которого поступают первые N выборок опорного сигнала (его начало), а самые новые выборки поступают на первый вход и-го блока 7 умножения группы, на второй вход которого поступают последние N выборок опорного сигнала (его конец).

Группа блоков 7 умножения в течение цикла корреляции (рециркуляции) формирует на своих выходах по М произведений выборок принимаемого Зр и опорного сигналов ° Эти произведения поступают на входы сумматора 14, на выходе которого в конце цикла корреляции (рециркуляции) образуется значение функции корреляции "все- З го" принимаемого и "всего" опорного сигналов. 11осле завершения цикла корреляции это значение функции корреляции переносится в регистр 15.

Формула изобретения

Цифровой коррелятор, содержащий аналого-цифровой преобразователь, вход которого является информацион45 ным входом коррелятора, первый и второй коммутаторы,-первую и вторую группы элементов памяти, группу блоков умножения, генератор тактовых импульсов, первый элемент задержки, 200 4 сумматор, первый счетчик, эл мент И и регистр, причем выходы первого коммутатора соединены с первыми входами соответствующих блоков умножения группы, первый выход управляемого генератора соединен с входом записи регистра, о т л и ч а ю щ и й— с я тем, что, с целью повышения быстродействия, в него введены второй элемент задержки, одновибратор, второй и третий счетчик, причем выход аналого-цифрового преобразователя соединен с информационным входом второго коммутатора, управляющий вход которого объединен с одноименным входом первого коммутатора и соединен с выходом второго счетчика, выходы второго коммутатора соединены с информационными входами соответствующих элементов памяти первой группы, адресные входы которых соединены с информационным выходом третьего счетчика, счетный вход которого объединен с первым входом элемента

И и соединен с выходом генератора .тактовых импульсов, выход переноса третьего счетчика соединен с входом разрешения суммирования второго счетчика, вход разрешения вычитания которого объединен с тактовым входом второго коммутатора и через первый элемент задержки — с входом разрешения суммирования сумматора, а через второй элемент задержки объединен с входом одновибратора и подключен к выходу переноса первого счетчика, выход одновибратора соединен с вторым входом элемента И, выход которого соединен со счетным входом первого счетчика, информационный выход первого счетчика соединен с адресными входами элементов памяти второй группы, выходы которых соединены с вторыми входами соответствующих блоков умножения группы, выходы которых соединены с соответствующими информационными входами сумматора, выход которого соединен с информационным входом регистра, выход которого является выходом коррелятора.

1264200

Составитель Е.Ефимова

Техред М.Ходанич Корректор В.Синицкая

Редактор И.Касарда

Заказ 5564/50

Тираж 671 Подписное

ВНИИПИ Государственного. комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4