Универсальный логический модуль

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике и вычислительной технике и предназначено для реализации всех логических функций п переменных . Цель изобретения - упрощение конструкции модуля. Устройство содержит п информационных шин 1-4 и 2 настроечных шин 5-20. Наличие п линеек, каждая i-я (,n) из которых содержит 2 логических ячеек при условии, что каждая логическая ячейка состоит из выполненных на МОП-транзисторах элементов И-НЕ и с РАВНОЗНАЧНОСТЬ, позволяет модулю (Л обладать регулярной структурой и делает его более однородным. 1 табл., 2 ил. ю О5 4 00 00 05

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (д11 4 Н 03 К 19/094

ОПИСАНИЕ ИЗОБРЕТЕНИЯ"

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3904737/24-21 (22) 04.06.85 (46) 15.10,86. Бюл, № 38 (72) Л.Б.Авгуль, А.В.Пархоменко, В.А.Мищенко и A.Ë,Êðèíèöêèé (53) 681,325.65(088.8) (56) Авторское свидетельство СССР № 333550, кл. (06 F 7/00, 1970, Якубайтис Э.А. Универсальные логические элементы. — Автоматика и вычислительная техника, 1973, ¹ 5.

„„SU„„1264336 А 1 (54) УНИВЕРСАЛЬН11Й ЛОГИЧЕСКИЙ МОДУЛЬ (57) Изобретение относится к микроэлектронике и вычислительной технике и предназначено для реализации всех логических функций и переменных. Цель изобретения — упрощение конструкции модуля. Устройство содержит.п информационных шин 1-4 и

2" настроечных шин 5-20. Наличие и линеек, каждая 1-я (1=1,n) из которых содержит ? логических ячеек при условии, что каждая логическая ячейка состоит из выполненных на

МОП-транзисторах элементов И-HF, и а

РАВНОЗНАЧНОСТЬ, позволяет модулю обладать регулярной структурой и делает его более однородным. 1 табл., 2 ил.

1264336

15

25 то

EIx,x„7l=RIR(RtRIU,х,U l,а, а(LI, о,о,x а(а(о, U )к,а(о х,ор

X,RiR(R(U,,Х, и > ХР(и„Х,и„!! Х,й(Я(и„X V„) X R(U,X U,,i))) Изобретение относится к микро.—

1 электронике и вычислительной технике и предназначено для реализации всех логических функций и переменных.

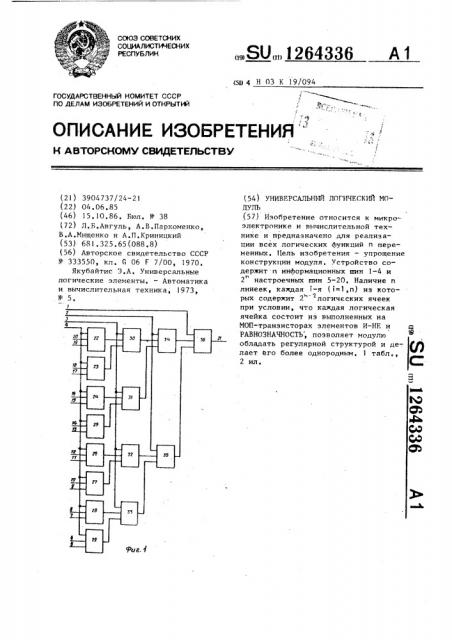

Бель изобретения — упрощение конструкции универсального логического модуля, На фиг. 1 приведена структурная схема предлагаемого модуля при n=4, Модуль содержит л =4 информационных шин 1-4, 2 =16 настроечных шин. н

5-20, выходную шину 21, ? =8 логических ячеек 22-29 первой линейки, 2 =4 логических ячеек 30-33 второй линейки, 2 =2 логических ячеек 34 ь-э п-4 и 35 третьей линейки и ? 4=1 логическую ячейку 36 четвертой линейки.

На фиг. 2 представлена принципиальная схема логической ячейки на

МОП-транзисторах.

Логический элемент И-HF. собран на транзисторах 37-39,элемент РАВНОЗНАЧНОСТЬ вЂ” на транзисторах 42-46.

Первая входная шина элемента РАВНОЗНАЧНОСТЬ (затвор транзистора 44) соединена с первой шиной 47 управления ячейки, вторая шина 41 управления которой соединена с первой вход- З0 ной шиной элемента И-HE (затнор транзистора 38), вторая входная шина которого (затвор транзисторов 37) соединена с информационной шиной 40 ячейки. Выходная шина элемента ИHF. (сток транзистора 39) соединена с второй входной шиной элемента РАВ-, НОЗНАЧНОСТЬ (затвор транзистора 43).

Выходная шина элемента РАВНОЗНАЧ-

НОСТЬ (сток транзистора 43) соеди- 40 иена с выходной шиной 48 ячейки.

Электрическое питание элементов ИНЕ и РАВНОЗНАЧНОСТЬ осуществляется по шинам 49 и 50, 45

И общем случае универсальный логический модуль на МОП-транзисторах, реализующий все логические функции

/ и переменных, содержит и информации онных и 2 настроечных шин, и .линеек; 50 каждая i-я (i=1,n) из которых содержит 2" логических ячеек, информационная шина каждой логической ячейки

1-й (i=T n) линейки соединена с 1-й информационной шиной модуля, а выходные шины всех логических ячеек

j-й (i=1, и=1) линейки соединены соответственно с шинами упранления логических ячеек (j+1)-й линейки, выходная шина логической ячейки а -й линейки соединена с выходной шиной модуля, настроечные шины которого соединены соответственно с шинами управления логических ячеек первой линейки.

Каждая логическая ячейка содержит выполненные на МОП-транзисторах элемент И-НЕ и элемент РАВНОЗНАЧНОСТЬ, выходная шина которого соединена с выходной шиной ячейки, а первая,входная шина соединена с первой шиной управления ячейки, вторая шина упранления которой соединена с первой нходной шиной элемента И-НЕ, вторая входная шина которого соединена с информационной шиной ячейки, а выходная шина соединена с второй входной шиной элемента РАВНОЗНАЧНОСТЬ.

Предлагаемый модуль строится на основе разложения:

f(x,,x„}=R(9 (х,х ), х,- Ч (х,x )) (1) где Г(х,х ) - произвольная логическая функция и переменных; Р.(х,х )=1,2- некоторые логические

1 функции n-I переменной;

R() - функция равнозначности.

При этом если f(x .,x„) разложить ю по !леннону:!.(x,õ )=x, Ч,(х,х }vx. Ч (х,x =), (2)

Пернообразная модуля получается путем последовательного и-кратного разложения F(х,x„) по переменным х,х,...,х„ согласно (1), 1

Например, для =4 первообразная имеет вид .

1264336 где l(=(U,,И2,...,И! ) — вектоР настройки, 4 UJ Ejn% )), /=1,16 °

Универсальный логический модуль содержит и линеек, каждая 1-я (i= !!-1

=1,n) из которых содержит 2 логических ячеек. Логическая ячейка описывается выражением: у R(U, хИ ), 10 дуля.

При подаче на информационные шины переменных х,,х и на настроечные шины сигналов настройки U Ц, на выходной шине модуля реализуется логическая функция f(õ„,х„), определяемая вЕктором настройки 1 =

=(и „И„...,И,.) .

40

Модуль работает следующим образом.

На .информационные шины 1-4 пода; 45 ются двоичные переменные х, х4 соответственно, на насtpDB IHIIB IIIHHbl

6-20 — сигнала настройки П И ccss ответственно (причем настроечные шины 5. 7, 9-19 модуля соединены с

50 первыми шинами управления соответствующих ячеек, а настроечные шины

6, 8, 10-20 — с вторыми шинами управления соответствующих ячеек), На выходе 21 модуля реализуется логическая функция f(õ,,x, ), определяе55 мая вектором настройки У=(И„,U

И, ). где x — сигнал на информационной шине ячейки;

li,, И вЂ” сигналы на шинах управления !

5 ячейки.

Структурно ячейка представляет собой выполненные на МОП-транзисторах элементы И-НЕ и РАВНОЗНАЧНОСТЬ, Информационная шина каждой ячейки i-й (i=i,n) линейки соединена с i-й информационной шиной модуля, на которую подается переменная х

>-iс!

1!1ины управления ячеек первой линейки соединены с настроечными шинами модуля, на которые подаются сигналы настройки U,, И ., принимаю. щие значения "О" и "1". Выходные шины всех ячеек j-й (j=l, и-1) линейки соединены с шинами управле30 ния логических ячеек (j+1)-й линейки, а выходная шина ячейки и-й линей. ки соединена с .выходной шиной моРассмотрим алгоритмы настройки.

Он основан на соотношениях (1) и (2), Пусть у, - значение реализуемой модулем логической функции f(x,x ) на (i-1)-м наборе, i=1 2".

Ф

Тогда исходным для нахождения вектора настройки !(является вектор

W =(у,y ....,y ). Вектор V находят о 2и из W за и шагов. Причем на 1-м шаге получается вектор W. из вектора

44,!, а на последнем шаге 14„= !(. — >

1. !, =,у,у ...,,у,,,2,...,г ),! й(=(и и ! М где m=2, z =у.gy,, 1=1,m.

2. н =,у,у,...,у,p,ð,...,ð тт 2 С 2 С

7,,л,...,7, г,г,...,г}, где

2 l и т.д, На и-м шаге компоненты вектора совпадают с соответствующими компонентами вектора 7! .

Пример. Найти вектор настройки У модуля четырех переменных (фиг.. 1 и,2).на функцию f(х x )= ! 4

=х ° x Vx ° х

Оч ев идн о

w =(0,о,n,1,n,î,о,1,о,о,0,1, l,1, 1,1) .

Тогда

cubi =(0,0,0,1 0,0,0,1,0,0,0,0,1 1, 1,О) . 4 =(0,0,0,1,0,0,0,0,0,0,0,0,1,1, 1,0) .

W =(0,о,о,1,î,0,î,n,î,0,0,о,l,l,,0,1). =(0,0 0 1 0 0 0 0 0 0 0 0 1,0, 0,1).

Таким образом, настройки модуля:

И; =О, 1=4, 13, 16;

U„=1, j=l,16, )ф1.

Количество МОП-транзисторов, необ. ходимых для построения универсального логического модуля, может быть рассчитано по формуле:

5=8 . (2 -1) !!, (модуль р переменных содержит 2 !!

:=2 -1 логических ячеек, каждая из которых содержит 8 МОП-транзисторов,, фиг., 2).

Количество МОП-транзисторов, необходимых для реализации универсального логического модуля, приведено в таблице.

1264336 ких ячеек, индюрмапионная шина каждой логической ячейки i-й (i=1,n) .линейки соединена с 1-й информаци онной шиной модуля, а выходные шины

S всех логических ячеек j-й (1=1,п-1) линейки соединены соответственно с шинами управления логических ячеек (j+1)-й линейки, выходная шина логической ячейки е --й линейки соединена с выходной шиной модуля, настроечные шины которого соединены соответственно с шинами управления логических ячеек первой линейки, а каждая логическая ячейка содержит выполненные на МОП-транзисторах элемент И-HE и элемент РАВНОЗНАЧНОСТЬ, выходная шина которого соединена с первой шиной управления ячейки, вторая шина управления которой соединена с первой входной шиной элемента И-HE вторая входная шина которого соединена с информационной шиной ячейки, а выходная шина соединена с второй входной шиной элемента РАВНОЗНАЧНОСТЬ.

Количество МОПтранзисторов

120

248

504

1016

2040 2760

524280

Формулаизобретения

Универсальный логическгй модуль на МОП-транзисторах, содержащий и

h информационных и 2 настроечных шин, о т л и ч а м шийся тем, что, с целью упрощения конструкции, он содержит п линеек,каждая i-я (i=1,n) н-1 из которых содержит 2 логичес<иа 2

Составитель О. Скворцов

Редактор А.Огар Техред А.Кравчук Корректор Л.Пилипенко

Заказ 5574/57 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул, Проектная, 4