Устройство циклового фазирования

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧ ЕСНОЙ Х

РЕСПУБЛИН (!! 4 Н 04 L 7/00, 7/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ l "

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3919289/24-09 (22) 27.06.85 (46) 15.10.86. Бюл. ¹ 38 (71) Харьковский ордена Ленина поли технический институт им.В.И.Ленина (72) В.П.Гетман, М.А.Иванов и 1О.В.Щербина !.(53) 621.394.622 (088.8) (56) Авторское свидетельство СССР № 511717, кл. Н 04 L 7/08, 1974.

Авторское свидетельство СССР № 924888, кл. Н 04 Ь 7/00, 1979. (54) УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ (57) Изобретение относится к технике связи.и может использоваться при приеме дискретной информации. Цель изобретения — повышение помехоустойчивости. Устр-во содержит блок выделения и распределения канальных символов 1БВРКС) 1, декодер 2, блоки умножения на обраэукнцие многочлены (БУ) 3 и 6, синхрогенератор 4, счетчик временного интервала 5, „„SU„„1264364 А 1 ключи 7 и 8 и решающий блок (РБ) 9.

РБ 9 состоит из накопителей !О и 11 и двухпорогового анализатора !2. С

БВРКС 1 две информационные последовательности поступают на БУ 3 и 6, в которых происходит умножение на соотв.многочлены. Если узловая синхронизация установлена правильно, с

БУ 3 на РБ 9 будет поступать последовательность нулей. При этом вероятность появления единиц на выходе БУ 6 равна 0,5. При нарушении узловой синхронизации единичные символы с вероятностью 0,5 будут появляться на выходе БУ 3. При этом . с РБ 9 сигнал о необходимости изменения узловой синхронизации поступает на БВРКС I и на счетчик временного интервала 5. БВРКС 1 меняет узловую синхронизацию на противоположную, а сигнал со счетчика временного интервала 5 закрывает ключи 7 и 8 на время, определяемое емкостью

БУ 3 и 6. 2 ил.

1264364

Изобретение относится к технике связи и может быть использовано для циклового фазирования кодов при приеме дискретной информации.

Цель изобретения — повышение по- 5 мехоустойчивости.

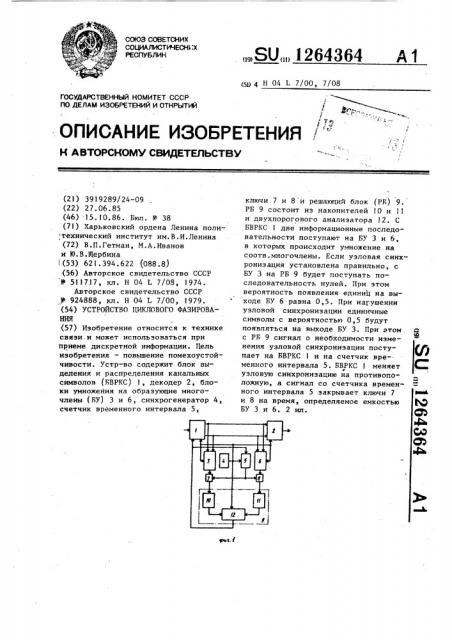

На фиг.l представлена структурная электрическая схема устройства циклового фазирования; на фиг.2 — пример реализации счетчика временного,. 10 интервала.

Устройство циклового фазирования содержит блок 1 выделения и распределения канальных символов, декодер

2, первый блок 3 умножения на образующие многочлены, синхрогенератор

4, счетчик 5 временного интервала, второй блок 6 умножения.на образующие многочлены, первый и второй ключи 7 и 8, решающий блок 9, при этом 20 решающий блок 9 содержит первый и второй накопители 10 и ll и двухпороговый анализатор 12, а счетчик 5 временного интервала содержит элемент И "13, счетчик 14, триггер 15.

Устройство работает следующим образом.

С выхода блока 1 выделения и распределения канальных символов инфор" мационные последовательности 30

Т „(D) = I(D) f„(D) + E„(D) и

Т (Р) — Х.(Р) f (Р) + Е (Р) поступают на входй первого 3 и второго 6 блоков умножения на образующие многочлены в различных комбинациях. При этом в первом 3 блоке умножения на образующие многочлены первая последовательность Т,(D) умножается на многочлен f (D), а вторая последовательность Т2(D) умножается на многочлен f,(D). Если узловая синхронизация установлена правильно, то на выходе первого блока 3 умножения на образующие многочлены при отсутствии ошибок будет постоянно следо45 вать последовательность нулей. В это же время во втором 6 блоке умножения на образующие многочлены первая последовательность Т,(D) умножается на многочлен f„(D), а вторая последовательность Т2(D) умножается на многочлен f (D). При этом очевидно, что независимо от наличия ошибок в канале связи вероятность появления единиц на выходе второго блока 6 умножения на образующие многочлены равна вероятности появления единичного символа в информационных последовательностях Т, (Р) и Т (Р), т.е. равна 0,5. Этот Жакт фиксируется решающим блоком 9, и устройство циклового фазирования сохраняет прежнее состояние узлового синхронизма.

При возникновении вставок и выпадений символов, число которых не кратно двум, узловая синхронизация нарушается. При этом уже второй блок 6 умножения на образующие миогочлены умножает первую последовательность Т,(Р) на многочлен Й (Р), а вторую последовательность Т (Р) 2 на многочлен f,(D). В это же время первый блок 3 умножения на образующие многочлены умножает цоследова тельность Т, (D),íà многочлен Е1(Р),; а последовательность Т (Р) на мно2 гочлен f 2(D) и íà его выходе появляются 1едийичные символы с вероятностью 0,5. Этот факт фиксируется решающим блоком 9, и он выдает сигнал о необходимости изменения узловой синхронизации в блок вычитания и распределения канальных символоЪ 1 и в счетчик временного интервала 5.

По этому сигналу блок выделения и распределения канальных символов изменяет, узловую синхронизацию на противоположную. Одновременно по этому же сигналу срабатывает триггер 15, и синхроимпульсы от синхрогенератора через элемент И 13 поступают на счетный вход счетчика 14, емкость которого определяется числом ячеек в первом 3 и втором 6 блоках умножения на образующие многочлены.

При переполнении счетчика 14 сигналом с его выхода триггер 15 устанавливается s исходное состояние..

Таким образом, в течение времени, определяемого емкостью счетчика 14 „ на выходе триггера 15 присутствует сигнал, удерживающий первый и второй ключи 7,и 8 в закрытом положении.

За это время информация, оставшаяся в ячейках памяти первого 3 и второго 6 блоков умножения на образующие многочлены от прежнего состояния уз- ловой синхронизации, "вытолкнута" символами последовательностей, соответствующих новому состоянию узловой синхронизации. При этом решающий блок 9 контролирует это новое состояние.

3 )264364

Формула и з о б р е т е н и я э

Составитель Н.Лебедянская

Редактор А.Гулько Техред И.Попович . Корректор В.Синицкая

Заказ 5576/58 Тираж 624

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Производственно -полиграфическое предприятие, г.ужгород, ул. Проектная, 4

Устройство циклового фазирования, содержащее блок выделения и распределения канальных символов, вход ко- Б торого является входом устройства, декодер, выход которого является выходом устройства, и решающий блок, выход которого соединен с управляющим входом блока выделения и распре- о деления канальных символов, первый ,и второй выходы которого соединены соответственно с первым и вторым входами декодера, о т л и ч а ю щ е— е с я тем, что, с целью повышения 15 помехоустойчивости, в устройство введены первый и второй блоки умножения на образующие многочлены, первый и второй ключи,- синхрогенератор и счетчик временного интервала, при 2о том выходы блока выделения и распределения канальных символов соединены соответственно с первыми и вто рыми информационными входами первого и второго блоков умножения на образующие многочлены, выходы которых через соответствующие первый и второй ключи соединены с входами решающего бпока, выход синхрогенератора соединен с синхровходами решающего блока, первого и второго блоков умножения на образующие многочлены, блока выделения и распределения канальных символов, декодера и счетчика временного интервала, выход которого соединен с управляющими входами первого и второго ключей, при этом выход решающего блока также соединен с управляющим входом счетчика временного интервала.