Многоканальное приемное устройство стартстопных телеграфных сигналов

Иллюстрации

Показать всеРеферат

(59 4 Н 04 L 25/40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬП ИЙ

ОПИСАНИЕ ИЗОБРЕТЕН

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ

" 4

r .- °, (21) 3703718/24-09 (22) 22.02.84 (46) 15.10.86. Бюл. Ф 38 (72) В.В.Берлов, Г.Т.Новиков и С.М.Перескоков (53) 621.394.62(088.8) (56) Авторское свидетельство СССР

Ф 559437, кл. Н 04 L 25/40, 1976. (54) ИНОГОКАНАЛЬНОЕ ПРИЕМНОЕ УСТРОЙСТВО СТАРТСТОПНЫХ ТЕЛЕГРАФНЫХ СИГНАЛОВ (57) Изобретение относится к радиотехнике и упрощает устройство путем исключения из каналов оперативных запоминающих блоков, накопителей, блоков стробирования и формирователей стробнрующих импульсов. Устройство содержит счетчики (С) 1, 5, задающий г-р 2, общий элемент ИЛИ З,блок памяти (БП) 4, элемент запрета 6, блок сравнения 7, дешифратор 8, каналы 9, - 9„, каждый из которых состоит из элемента НЕ 10, циклового триггера 11, элемента И 12, регистра

„SU„„1264367 А 1

13, элементов ИЛИ 14, 15, блока выделенйя фронта 16. В исходном состоянии ячейки БП 4 находятся в состоянии "0". С 1 изменяет состояние при поступлении импульсов с-.г-ра 2, выда.. ° ет сигналы на адресные входы БП 4 и входы дешифратора 8. С другого выхода С 1 импульс поступает на вход С 5, выходы которого соединены с первыми входами блока 7 и через элемент запрета 6 с информационными входами

БП 4. Выход БП 4 соединен с вторыми входамн блока 7. В каждом канале

9, - 9„ цикловой триггер 11 находит-. ся в нерабочем состоянии и запрещает д работу регистра 13 информационный @

1 вход которого соединен с информацион. ныл входом циклового триггера 11 и через элемент НЕ 10 с входом устрой- С ства. Запись числа, соответствуащего

Q времени поступления в канал перехода от стопа к старту, происходит независимо для каждого канала, поэтому работа каналов будет происходить не-. зависимо; скорости передачи в каждом канале д.б. одинаковыми. t ил.

1264367

1О

30 п ° k

f î

Изобретение относится к радиотехнике и может использоваться для приема и регистрации телеграфных сообщений в многоканальных линиях связи.

Цель изобретения — упрощение устройства.

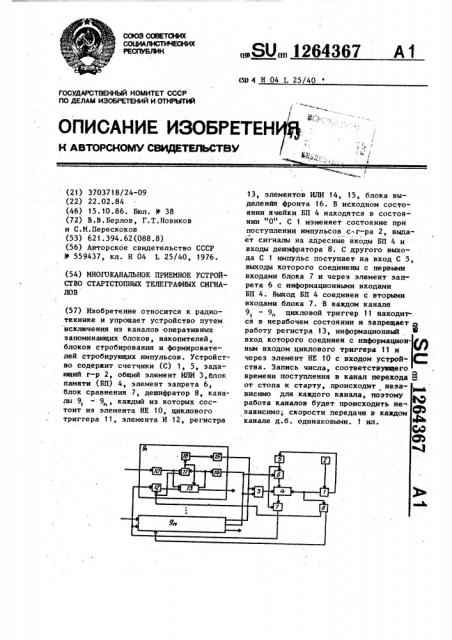

На чертеже представлена структур" ная электрическая схема предложенного многоканального приемноro устройства.

Многоканальное приемное устройство стартстопных телеграфных сигналов содержит первый счетчик 1, задающий генератор 2, общий элемент ИЛИ 3, блок 4 памяти, второй счетчик 5, элемент запрета 6, блок 7 сравнения, дешифратор 8, каналы 9 — 9„, каждый из которых состоит из элемента НЕ

10, циклового триггера 11, элемента

И 12, регистра 13, первого и второго элементов ИПИ 14, 15 и блока 16 выделения фронта, Устройство работает следующим образом.

В исходном состоянии ячейки блока 4 памяти находятся в состоянии

"О", Первый счетчик 1 изменяет состояние при поступлении импульсов с задающего генератора 2, выдает сигналы на адресные входы блока 4 памяти и входы дешифратора 8. С другого выхода первого счетчика 1 импульс поступает на вход второго счетчика 5, выходы которого соединены с первыми входами блока 7 сравнения и через элемент запрета 6 с информационными входами блока 4. Выход блока 4 соединен с вторыми входами блока 7 сравнения. В каждом канале 9 — 91 цикловой триггер 11 находится в нерабочем состоянии и запрещает работу регистра 13, информационный вход которого соединен с информационным входом циклового триггера 11 и через элемент НЕ 1О с входом устройства.

Выход элемента И I2 соединен со счетным входом регистра 13, его первый вход подключен к выходу блока 7 сравнения, его второй вход соединен . с выходом дешифратора 8. Выходной сигнал циклового триггера 11 через блок 16 выделения фронта, второй элемент ИЛИ 15 и общий элемент ИЛИ 3 поступает на вход записи блока 4 памяти. Выход регистра 13 подключен к входу сброса циклового триггера 11 и через первый элемент ИЛИ 14 соединен с первым входом общего элемента ИЛИ 3 и дополнительным входом элемента запрета 6. Если в момент прихода сигнала с выхода дешифратора

8 на информационном входе циклового триггера 11 единичная посылка (старт) он переходит в рабочее состояние.

Выходной сигнал его через блок 16 выделения фронта, элемент ИЛИ .15, общий элемент ИЛИ 3 поступает на вход записи блока 4 памяти и записывает в него число, соответствующее состоянию второго счетчика 5, через открытый элемент запрета 6. При этом,выходной сигнал с блока 7 сравнения через открытый элемент И 12 соответствующего канала 9 - 9„ записывает в регистр 13 входную информацию в инверсном коде. При появлении сигнала на выходе регистра 13 (стартовая посылка) с его выходом выдается знак сообщения, после этого цикловой триггер 11 переходит в нерабочее состояние и запрещает работу регистра 13, и через первый элемент ИЛИ 14 закрывает элемент запрета 6, и через общий элемент ИЛИ 3 "обнуляет" ячейки памяти, соответствующие данному каналу. Задающий генератор 2 имеет частоту, равную где k — целое число; и — число каналов 9, — 9„; .

, — длительность элементарной посылки.

Запись числа, соответствующего времени поступления в канал перехода от стопа к старту, происходит независимо для каждого каналар поэтому работа каналов будет происходить независимо, скорости передачи в каждом канале должны быть одинаковыми. Модуль второго счетчика 5 равен К; а первого счетчика 1 равен П

Формула изобретения

Многоканальное приемное устройство стартстопных телеграфных сигналов, содержащее последовательно соединенные задающий генератор и первый счетчик, а в каждом канале — цикловой триггер, элемент И и регистр, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства путем исключения из каналов оперативных запоминающих блоков, накопителей, блоСоставитель А.Москевич

Редактор А.Гулько Техред Л.Олейник Корректор А Тяс«

Заказ 5577/59 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 12643 ков стробирования и формирователей стробирующих импульсов, в него введены дешифратор, общий элемент ИЛИ и последовательно соединенные второй счетчик, элемент запрета, блок памяти, к второму входу которого подключен первый выход первого счетчика, и блок сравнения, к второму входу

° которого подключен выход второго счетчика, вход которого соединен с вто- tO рым выходом первого счетчика, первый выход которого подключен к входу дешифратора, при этом выход общего элемента ЕЛИ соединен с третьим входом блока памяти, а в каждый канал 15 введены два элемента ИЛИ, блок выделения фронта и элемент НЕ, выход ю которого подключен к первым входам циклового триггера, выход которого соединен с входом блока выделения 20

67 4 фронта, и регистра, первый выход которого соединен с входами первого элемента ИЛИ и с вторым входом циклового триггера, выход которого подключен к второму входу регистра,третий вход которого соединен с выходом элемента И, первый вход которого соединен с соответствующим выходом дешифратора и с третьим входом циклового триггера, причем выход первого элемента ИЛИ подключен к второму входу элемента запрета и к одному входу общего элемента ИЛИ, другой вход которого соединен с выходом второго элемента ИЛИ, к входам которого подключен выход блока выделения фронта, входы элементов

НЕ всех каналов являются входами устройства, выходами которого являются вторые входы регистров.