Многоканальное устройство приоритета

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения сокращение оборудования и улучшение синхронизации устройства. В многоканальное устройство приоритета, содержащее в каждом канале три триггера, три элемента И и элемент ИЛИ, дополнительно введены генератор импульсов, элемент И, триггер, два элемента ШШ и элемент И в каждый канал. Э.то позволяет сократить оборудование и улучшить синхронизацию работы устройства. Изобретение может быть использова-i но в устройствах сопряжения ЦВМ с абонентами автоматизированных систем управления, работающих в режиме разделения времени. I ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (so 4 С 06 F 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3864953/24-24 (22) 11.03.85 (46) 23.10.86. Бюп. У 39 (72) Н.Н.Шарпиле и И.Я.Антонов (53) 681.325(088.8) (56) Авторское свидетельство СССР

11 684536, кл. С 06 F 3/04, G 06 F 9/46, 1978.

Авторское свидетельство СССР

У 734689, кл. G 06 F 9/46, 1980. (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО

ПРИОРИТЕТА (57) Изобретение относится к вычислительной технике. Цель изобретения—

„„Я0„„1265772 А 1 сокращение оборудования и улучшение синхронизации устройства. В многоканальное устройство приоритета, содержащее в каждом канале три триггера, три элемента И и элемент ИЛИ, дополнительно введены генератор импульсов, элемент И, триггер, два элемента ИЛИ и элемент И в каждый канал. Это позволяет сократить оборудование и улучшить синхронизацию работы устройства..

Изобретение может быть использова- но в устройствах сопряжения ЦВМ с абонентами автоматизированных систем управления, работающих в режиме разделения времени. 1 ил.

1265772

Изобретение относится к вычислительной технике, в частности, к устройствам приоритета, и может быть использовано при организации обмена между периферийными устройствами и

ЭВМ, а также для подключения к общему полю памяти регистров приема и выдачи информации в автоматизированных системах управления, работающих !

О в режиме разделения времени.

Целью изобретения является сокращение оборудования.

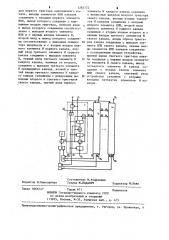

На чертеже приведена функциональная схема многоканального устройства !

5 приоритета, Многоканальное устройство приоритета содержит каналы l, в каждый из которых входят триггеры 2-4 и элементы И 5-7, генератор 8 импульсов, элемент И 9, триггер 10 элементы ИЛИ

11 и 12, каждый канал I содержит элемент И 13 и элемент ИЛИ 14. Устройство имеет запросные входы 15, ответный вход 16 и выходы 17, а также выход 18 элемен а ИЛИ 14, выход 19 эле25 мента И 6, вь од 20 элемента И 13, вход 21 канала 1 и установочной вход

22 устройства.

При включении питающего напряжения в многоканальное устройство приоритета по установочному входу 22 поступает сигнал установки в исходное состояние, который через элемент ИЛИ

14 устанавливает триггеры 2-4 и через элемент ИЛИ 12 триггер 10 в исходное состояние.

Триггеры 2-4 всех каналов устанавливаются в исходное состояние.

Тактовые импульсы с выхода генератора 8 проходят через элементы И 5, 6 и 13. Так как триггеры 2-4 всех каналов находятся в исходном состоянии, сигналы опроса заявок проходят через элемент И 13 на вход 21 второго канала, с выхода второго канала 45 на вход . 21, третьего канала и так далее, т.е. импульсы опроса заявок постоянно анализируют состояние триггера 4 каждого канала до тех пор, пока в один.из каналов по входу 15 не поступит сигнал заявки.

Устройство работает следующим образом.

Сигнал заявки по входу 15 поступает на вход триггера 2 и устанавли- SS вает его в состояние "1". Первый тактовый импульс опроса (отсчет ведется от момента поступления сигнала запроса) с входа 21, проходит через элемент И 5, открытый "1" с выхода триггера 2, и через элемент И 13, открытый "1" с инверсных выходов триггеров 3 и 4, на вход 21 второго канала. Импульс с выхода элемента И 5 поступает на вход триггера 3 и устанавливает его в состояние "1", т.е. он начинает выдавать "0" на входы элементов И 5 и 13, и "1" на вход элемента И 6.

Второй тактовый импульс с входа

21, проходит только через элемент

И б (элементы И 5 и 13 закрыты "0" с инверсного выхода триггера 3) на вход триггера 4, устанавливая его в

"1", и через элемент ИЛИ 11 на вход сброса триггера 10, устанавливая его в "0"

С выхода триггера 10 начинает выдаваться "0", который блокирует прохождение тактовых импульсов через элемент И 9.

С прямого выхода триггера 4 начинает выдаваться "1" на выход 17 и на первый вход элемента И 7 ° После пере— дачи информации по входу 16 поступает сигнал окончания работы общей магистрали. Он поступает одновременно во все каналы, но устанавливает в исходное состояние триггеры 2-4 того канала, который разрешил подключение к магистрали. В данном примере в исходное состояние устанавливаются триггеры 2-4 первого канала, потому что на элемент И 7 этого канала поступает

"!" с выхода триггера 4.

Одновременно через элемент ИЛИ 12 устанавливается в "1" триггер 10 °

Тактовые импульсы опроса с выхода элемента И 9 начинают вновь поступать в каналы 1.

На этом первый канал свою работу заканчивает. Остальные каналы рабо- тают аналогично.

При поступлении заявок по входам

15 сразу в несколько каналов сначала обнаруживается заявка в младшем канале 1 и выполняется, затем в старшем канале и так поочередно, пока не будут выполнены все заявки, т,е. высший приоритет на подключение к магистрали у первого канала, затем у вторжо и так далее, последний канал имеет низкий приоритет.

Рассмотрим работу устройства при одновременном поступлении заявок в первый и второй каналы.

1265772

После выполнения заявки первого канала 1,, по входу 16 поступает сиг-55 нал окончания работы, который устанавливает триггеры 2-4 первого канала I> через элементы И 7 и ИЛИ 14 и

Сигналами заявок по входам 15 устанавливаются триггеры 2 каналов 1

1 и 1„, Первый тактовый импульс с выхода элемента И 9 проходит через элемент 5

И 5, устанавливая в "1" триггер 3, и через элемент И 14 на вход 21д второго канала 1. С входа -21 первый тактовый импульс поступает на входы элементов И 5 и 13 второго канала

Так как элемент И 5 второго кана 2 ла 1 открыт разрешающим потенциалом с выхода триггера 2, первый импульс опроса проходит через элемент И 5 на вход триггера 3 второго канала 1 и устанавливает его в "1". Одновременно импульс проходит через элемент

И 13 второго канала 1 на вход 21 третьего канала и так далее до последнего канала 1„.

Во всех каналах, в которые поступили заявки, первым тактовым импульсом опроса признаки поступивших заявок переписываются из триггеров 2 в триггеры 3 соответствующего канала.

При этом с инверсного выхода триггера 3 начинает выдаваться запрещающий потенциал на входы элементов И 5 и

13, тем самым блокируется передача следующего тактового импульса опроса 30 через элемент И 13 в старший канал, с прямого выхода триггера 3 начинает выдаваться разрешающий потенциал на вход элемента И 6.

Второй тактовый импульс опроса с д выхода элемента И 9 через вход 21, первого канала поступает на входы элементов И 5, 6 и 13, но проходит только через элемент И 6. Триггер 4 устанавливается в "I, которая посту-40 пает на выход 17„ и элемент И 7.

Второй тактовый импульс опроса во второй 1 канал не поступает, так как элемент И 13 закрыт запрещающим потенциалом с инверсного выхода триг-!5 гера 3. Одновременно с выхода элемента И б второй тактовый импульс опроса проходит через элемент ИЛИ 11 на вход сброса триггера 10 и устанавливает его в "0", "0" с выхода тригге- 50 ра 10 блокирует прохождение импульсов через элемент И 9. триггер 10 через элемент ИЛИ 12 в исходное состояние.

Следующий тактовый импульс опроса с выхода элемента И 9 через вход 21 и элемент И 13 первого канала 1 пос1 тупает на вход 21 второго канала

1 . Этот импульс проходит только через элемент И 6 второго канала на вход, триггера 4 и через выход 19 и элемент ИЛИ 11 на вход триггера 10.

С второго выхода триггера 4 второго канала начинает выдаваться разрешающий потенциал на вход элемента И 7 и выход 17.

Запрещающим потенциалом с выхода триггера 1О блокируется прохождение тактовых импульсов через элемент И 9.

При поступлении сигнала окончания работы по входу 16 устанавливается в исходное состояние только триггеры

2-4 второго канала (триггеры 2-4 остальных каналов не могут быть установлены в исходное. состояние, так как элемент И 7 каждого из этих каналов блокирован запрещающим потенциалом с прямого выхода триггера 4) через открытый элемент И 7 и элемент

ИЛИ 14, а также триггер 10 через выход 18 и элемент ИЛИ 12.

Формула изобретения

Многоканальное устройство приоритета, содержащее в каждом канале три триггера, три элемента И и в каждом канале, кроме первого и последнего, элемент ИЛИ, причем прямой выход первого триггера канала соединен с первым входом первого элемента И своего канала, выход первого элемента И канала соединен с единичным входом второго триггера своего канала, прямой выход второго триггера канала соединен с первым входом второго элемента

И своего канала, выход второго элемента И канала соединен с единичным входом третьего триггера своего канала, единичный вход третьего триггера каждого канала является соответствующим выходом устройства, о т л и— ч а ю щ е е с я тем, что, с.целью сокращения оборудования, устройство содержит генератор импульсов, элемент И, триггер, два элемента ИЛИ, в каждом канале четвертый элемент И, а в первом и последнем каналах элемент

ИЛИ, причем каждый запросный вход устройства соединен с единичным вхо)2657

16 17

Составитель М.Кудрявцев

Техред М.Ходанич

Редактор И.Николайчук

Корректор М.Пожо

Заказ 5666/47

Тираж 671

ВНИИТИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-.35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 дом первого триггера одноименного канала, выходы элементов ИЛИ каналов соединены с входами первого элемента

ИЛИ, выход которого соединен с единииным входом триггера, нулевой вход и выход которого соединены соответственно с выходом второго элемента

ИЛИ и с первым входом элемента И, второй вход и выход которого соединены соответственно с выходами генера- 10 тора импульсов и с вторым входом первого элемента И первого канала, первый вход третьего элемента И первого канала соединен с выходом элемента

И, первый вход третьего элемента И 15 каждого канала, начиная со второго, соединен с выходом третьего элемента

И предыдущего канала, второй и третий входы третьего элемента И каждого канала соединены с инверсными вы- 20 ходами второго и третьего триггеров своего канала, третий вход первого

72 ь элемента И каждого канала соединен с инверсным выходом второго триггера своего канала, выходы вторых элементов И каналов соединены с входами второго элемента ИЛИ, второй вход первого элемента И каждого канала соединен с вторым входом второго и с первым входом третьего элементов И своего канала, входы сброса триггеров канала соединены с выходом элемента ИЛИ своего канала, первые входы элементов ИЛИ каналов соединены с установочным входом устройства, прямой выход третьего триггера канала соединен с первым входом четвертого элемента И своего канала, выход четвертого элемента И канала соединен с вторым входом элемента

ИЛИ своего канала, ответный вход устройства соединен с вторыми входами четвертых элементов И каналов.