Устройство для воспроизведения функций двух переменных

Иллюстрации

Показать всеРеферат

Изобретение относится к аналоговой и аналого-цифровой вычислительной технике и может быть применено при моделировании систем автоматического управления. Цель изоб-- ретения - повышение быстродействия. Поставленная цель достигается введением третьего и четвертого цифроаналоговых преобразователей и второго и третьего блоков умножения с соответствующими; связями. Для воспроизведения функций двух переменных производится кусочно-квадратичная аппроксимация кривых f(x. У) и f(x,) и функция определяется по формуле ,f;:(x,y) Ац+ B.-J+C-J хЧ .j+ F;jX -f X. Коэффициенты A-, B;J, С;-, D-, , в цифровой форме хранятся/в блоке памяти, а новые значения коэффициентов извлекаются из блока памя (Л , ти при переходе X и У на новый участок . 2 ил. с

СОЮЗ СОВЕТСКИХ

СОЩИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ао 4 С 06 С 7/26 ф

1, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

:Ь с.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3701699/24-24 (22) 13. 02. 84 (46) 23. 10.86. Бюл. У 39 (71) Московский ордена Ленина и ордена Октябрьской Рево3цоции авиационный институт им. С. Орджоникидзе (72) О.Н. Сахаров и М.И. Чебатко (53) 681".335 (088.8) (56) Авторское свидетельство СССР

Ф 842850, кл. G 06 G 7/26, 1981.

Патент. США У 4000401, кл. 235-150.53, 1976. (54) УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ

ФУНКЦИЙ ДВУХ ПЕРЕМЕННЫХ (57) Изобретение относится к аналоговой и аналого-цифровой вычислительной технике и может быть применено при моделировании систем авто„„SU„„12 5805 А1 матического управления. Цель изоб- ретения — повышение быстродействия.

Поставленная цель достигается введением третьего и четвертого цифроаналоговых преобразователей и второго и третьего блоков умножения с соот- ветствующими,связями. Для воспроизведения функций двух переменных производится кусочно-квадратичная аппроксимация кривых f(x, у ) и f(x,у „) и функция определяется по формуле

f; (x,у) А;+ В;1+С; Х + y(D;+ Р; Х +

Р;1. С3 в цифровой бор eß хранятся=в блоке памяти, а новые значения коэф" фициентов извлекаются из блока памя" ,ти при переходе Х и У на новый учас" ток. 2 ил.

1265805

Изобретение относится к аналого.вой и аналого-цифровой вычислительной технике и может быть применено при моделировании систем автоматического управления.

Цель изобретения — повьппение быстродействия.

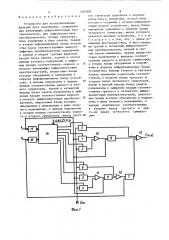

На фиг. 1 представлена структурная схема устройства для воспроизведения функции двух переменных; на фиг. 2 — произвольная функция двух переменных 1,х, у).

Устройство для воспроизведения функций двух переменных содержит два умножающих цифроаналоговых преобразователя 1 и 2, четыре цифроаналоговых преобразователя 3-6, три блока

7-9 умножения, четыре сумматора 1013, блок 14 памяти и два аналогоцифровых преобразователя 15 и 16.

Устройство для воспроизведения функций двух переменных работает следующим образом.

На фиг. 2 приведены две кривые (x,у;1 и (х,у !1 произвольной функции двух переменных при постоянных. ! значениях переменной у =У1 и у У1и

Для воспроизведения функций двух переменных производится кусочно-квадратичная аппроксимация кривых f(x,у; ) и f(х, у;,). На 1 -м участке аппроксимации Функций f (х,у; ) и f (x, У., ) представляются в виде:

<(x,q;)-a; Ь; x с;х 1

Х(х.у;„)=д;+ Х;х+ ;к

Для того, чтобы получить значение функций f(х,у), производим линейную. ,интерполяцию между 4(x, ) и 1(х,i);„):

Ц-Ч; ..!»»!1=!(» ;)» (!»»,q Äj-»(»,» 1);

1 1

Подставляя выражения для (х ) и f (.х,Ч Äj, получаем

Х(х+а; Ь;х!с;х + (d;>3;x>);x -а,-" х-с;х 1= и! )

=а;- д,.aj» b. jf,-b;j)»+

Ъ«ч> %. ч с; — (-с;)1х+Ч! х+ Ъ Ч1 -1 Ч1+!! j 1 %

, -c;

Ф х

Jj 5

Таким образом, 1(х,Ч)ЬЬх+Сх ii((z) ° Гх С,x ), (IJ

45..выражением (2) 50

5

40 где А, В, С, D, Г, С вЂ” функции Х и У

IIpH Х; Х " X;„H У y < yjм функция определяется по формуле

1; (хЧ)=Д; tB;) C(х +)(2; -bF; х+G.„õ 1.(2)

Формула для (х, у ) реализуется устройством, схема которого приведена на фиг.1, причем первый умножающий цифроаналоговый преобразователь

1, цифроаналоговые преобразователи

3 и 5, сумматоры 10 и 13, и второй блок 8 умножения реализуют выражение

А + В, x + С х в виде А +х(В +

+ С;,x) а второй умножающий цифроаналоговый преобразователь 2, цифроаналоговые преобразователи 4 и 6, сумматоры 11 и 12, и первый блок 7 умножения реализуют выражение D;; +

+Fö x+G;) x B Bvpe D;> +x(F;> +G; x) .

С; в цифровой форме хранятся в блоке

I памяти и поступают на входы соответственно блоков 5,3,1,6,4 и 2. Первая входная переменная Х s аналоговой форме поступает на аналоговые входы первого и второго умножающих цифроаналоговых преобразователей 1 и 2, на выходах которых получаются сигналы, соответствующие .произведениям С„х и G,õ. Сигналы с выходов сумматоров 10 и 11, реализующих соответственно суммы В; +С, х и G<> х +

+F;>, проходят соответственно на второй и третий блоки 8 и 9 умножения, которые служат для получения соответственно произведений х(В + С"х) и !1 x(F + G" х) . !

1 !)

Йа выходе сумматора 12 реализуется выражение D + x(F" + С"х}, а на !

»! Ч 1J выходе первого блока 7 умножения— выражение y(D;;+ x(F!> + С;; х )) . Сигнал, соответствующий выходному зна1 чению функции 1;,, получается на выходе сумматора 13 в соответствии с

По цифровым кодам, получающимся на выходах первого и второго аналого цифровых преобразователей 15 и 16, соответствующим входным переменным

Х и У, выполняется адресация дискрет ных значений коэффициентов, хранящихся в блоке 14 памяти, для чего указанные коды подаются на соответствующие группы адресных входов блока 14 памяти. При переходе Х и У на новый участок из блока 14 памяти извлекаются новые значения коэффициентов А", В,, С ", D", F G" !! !! !1 !1 э з . 2б 5805 4

Формула изобретения

Устройство для воспроизведения функций двух переменных, содержащее два умножающих цифроаналоговых преобразователя, два цифроаналоговых преобразователя, четыре сумматора, блок умножения и блок памяти, первый и второй информационные входы устройства через соответствующие аналогоцифровые преобразователи подключены к первой и второй группам адресных входов блока памяти, первый и второй выходы которого подключены к цифровым входам соответственно первого и 15 второго умножающих цифроаналоговых преобразователей, аналоговые входы которых объединены и подключены к первому информационному входу устрой-, ства, а выходы подключены к первым _#_ входам соответственно первого и второго сумматоров, третий и четвертый выходы блока памяти подключены к цифровым входам соответственно первого и второго цифроаналоговых преобразователей, аналоговые входы которых объединены и подключены к шине опорного напряжения, а выходы подключены к вторым входам соответственно первого и второго .сумматоров, выход треть-30 его сумматора подключен к первому входу блока умножения, второй вход

:которого соединен с вторым информационным входом устройства, выход блока умножения подключен к первому входу четвертого сумматора, выход которого является выходом устройства, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены третий и четвертый цифроаналоговые преобразователи, второй и третий блоки умножения, первые входы которых подключены к выходам соответственно первого и второго сумматоров, а вторые входы объединены и подключены к первому информационному входу устройства, выходы второго и третьего блоков умножения подключены соответственно к первому входу третьего и второму. входу четвертого сумматоров, пятый и шестой выходы блока памяти подключены к цифровым входам соответственно третьего и четвертого цифроаналоговых преобразователей, аналоговые входы которых объединены и подключены к шине опорного напряжения, а

I выходы подключены соответственно к второму :входу третьего . и треть му входу четвертого сумматоров.

1265805

Составитель Н. Зайцев

Техред А.Кравчук Корректор М. Самборская

Редактор А. Ворович

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5667/48

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4