Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с коррекцией ошибок. Целью изобретения является повьппение быстродействия устройства. Устройство содержит накопитель,входной и выходной регистры, два коммутатора , два триггера, блок форми рования признака четности, блок контроля достоверности информации, блок сравнения, блок управления, блок вывода данных, группу элементов И и два элемента И. Повышение быстродействия достигается за счет применения одного из двух видов кодирования: без занесения признака четности в контрольный разряд входного регистра и с записью признака четности в контрольный разряд. При первом способе запись производится за несколько тактов, а считывание - за один такт, при втором способе - запись данных за один такт, считывание при отсутствии ошибок за один такт, при наличии ошибки за три такта. Один из этих двух видов кодирования информации применяется в зависимости от направления передачи данных, в результате передача данных вьтолняется за один такт при считывании и записи. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕа1УБЛИН (50 4 6 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМЪГ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3898574/24-24 (22) 22.05.85 (46) 23.10.86. Бюл. У 39 (77) B.Н.Горшков, С.О .Малецкий, А,П.Минин и А.А.Соколов (53) 681.327(088.8) (56) Авторское свидетельство СССР

В 830587, кл. G 11 С 29/00, 1981.

Авторское свидетельство СССР

У 333605, кл. С 11 С 29/00, 1972. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С CAMOKOHTP0ЛЕМ (57) Изобретение относится к вычислительной технике, в частности к запоминаюшим устройствам с коррекцией ошибок. Целью изобретения является повьппение быстродействия устройства.

Устройство содержит накопитель, входной и выходной регистры, два коммутатора, два триггера, блок формирования признака четности, блок кон„.SU„, 1265860 А 1 троля достоверности информации, блок сравнения, блок управления, блок вывода данных, группу элементов И и два элемента И. Повышение быстродействия достигается за счет применения одного иэ двух видов кодирования: без занесения признака четности в контрольный разряд входного регистра и с записью признака четности в контрольный разряд. При первом способе запись производится sa несколько тактов, а считывание — за один такт, при втором способе — запись .данных за один такт, считывание при отсутствии ошибок за один такт, прн наличии ошибки за три такта. Один из этих двух видов кодирования информации применяется в зависимости от направления передачи данных, в результате передача данных выполняется эа один такт при считывании и записи. 3 ил, 1 12

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Целью изобретения является повышение быстродействия устройства.

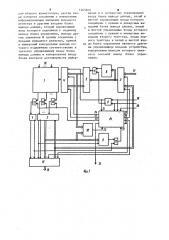

На фиг, 1 представлена функциональная схема предлагаемого устройства, на фиг. 2 и 3 — функциональные схемы наиболее предпочтительных вариантов выполнения блока управления и блока вывода данных.

Устройство содержит (фиг. 1) накопитель 1, входной 2 и выходной 3 регистры, первый 4 и второй 5 коммутаторы, первый 6 и второй 7 триггеры, блок 8 формирования признака четности, блок 9 контроля достоверности информации, блок 10 сравнения, первый ll и второй 12 элементы И, группу элементов И 13, блок 14 управления и блок 15 вывода данных, адресные 16 входы, информационные входы 17 и выходы 18, управляющие входы 19 и 20 устройства, входы 2123 и выходы 24-31 с первого по восьмой блока 14 управления.

Блок 14 управления (фиг, 2} содержит элементы ИЛИ 32-37, элементы

И 38-44, элементы 45-52 задержки, Блок 15 вывода данных (фиг. 3) содержит элементы И 53-56, элементы

ИЛИ 57 и 58, группы элементов И 59 и

60, группу элементов ИЛИ 61.

Предлагаемое устройство работает следующим образом.

Запись и считывание данных можно производить с помощью двух способов кодирования, отличающихся тем, что при первом способе запись производится за несколько тактов, а считывание за один, а при втором способе кодирования данные записываются за один такт, а считываются за несколько тактов, Способ кодирования определяется полярностью сигнала на входе 19.

При первом способе кодирования единичным сигналом на прямом входе

19 триггер 6 устанавливается в единичное состояние. Двоичное кодовое слово под воздействием сигнала с выкода 28 блока 14 передается через коммутатор 5 в регистр 2 ° Признак четности при первом способе кодирования через элемент И 11 в контроль; ный разряд регистра 2 не передается.

Под воздействием сигнала с выхода 24 блока 14 прямой код слова, код ну65860

f5

40 ля в контрольном разряде и код единицы с выхода триггера 6 через пер-. вый коммутатор передаются в.накопитель 1 для записи в ячейку по адресу, поступившему на входы 16. Затем осуществляется контрольное считывание содержимого этой ячейки и по сигналу с выхода 25 — передача через элементы И 13 кода слова в регистр

3 и кода единицы в триггер 7.

В блоке 10 производится сравнение кодов записанного и считанного слов, Если они не совпадают, на вход

23 блока 14 будет сформирован сигнал, по которому через коммутатор 4 в накопитель 1 поступит для записи инверсный код слова с регистра 2, причем в контрольном разряде будет код единицы, что подчеркивает инверсную запись слова, а в дополнительном разряде по-прежнему будет код единицы, указывающий на способ кодирования. При считывании слова, записанного первым способом, по сигналу на входе 20 блок 14 формирует сигнал на выходе 25, считанный код принимается в регистр 3, а в триггер 7 заносится код единицы.Затем по сигналу на выходе 26 блока 15, выдает на выходы 18 устройства код слова с прямых информационных выходов регистра 3, если в контрольном разряде нуль, или с инверсных — если в контрольном разряде единица.

Следовательно, запись информации при первом способе кодирования производится за три такта; запись, контрольное чтение, восстановление (запись инверсного кода при ошибке) » а чтение — за один такт.

При втором способе кодирования единичный сигнал на инверсном входе

l9 устанавливает триггер 6 в нулевое состояние, Двоичное кодовое слово под воздействием сигнала с выхода

28 блока 14 передается через коммутатор 5 в регистр 2. При этом в контрольный разряд регистра 2 через элемент И 11 заносится признак четности, сформированный блоком 8, Кодовая комбинация с прямых выходов регистра

2 и код нуля с выхода триггера 6 записываются в накопитель l по соответствующему адресу. При считывании слова, записанного вторым способом,: по сигналу на входе 20 блок 14 формирует сигнал на выходе 2$, считанный код поступает в регистр 3, а в триг)265860 гер 7 — код нуля. Код слова и признак четности с прямых выходов регистра 3 поступают в блок 9, в.котором код слова контролируется на четность и результат сравнивается с 5 поступившим признаком четности.

При совпадении сформированного и принятого признака четности сигнал ошибки не формируется. Тогда блок 14 вырабатывает единичный сигнал на. выхо-10 де 26, по которому блок 15 выдает на выходы 18 код слова с прямых выходов регистра 3. При несовпадении фор.мируется сигнал ошибки, который через элемент И 12 поступает на вход 15

22 блока 14, à íà его выходе 29 формируется единичный сигнал. Этот сигнал обеспечивает передачу инверсного кода слова с регистра 3 через коммутатор 5 в регистр 2 и блок 8. По 20 сигналу с выхода 24 блока 14 новая кодовая комбинация с прямых выходов регистра 2 и код нуля и выхода триггера 6 записывается в накопитель 1 по тому же адресу. Затем производится считывание и прием кода в регистр

3 и триггер 7. Если ошибка одного разряда систематическая, то после повторного считывания блок 9 подтвердит сигнал ошибки, на выходе 30 бло- Ç0 ка 14 будет выработан сигнал, по которому блок 15 выдаст на выходе 18 код слова с инверсных выходов регистра 3. Если же ошибка была случайная, то после повторного считывания блок

9 не вырабатывает единичный сигнал и блок 14 выдаст на выход 31 сигнал

"Сбой", а на выходах 26 и 30 будут сигналы нулевые, следовательно, код слова на выходы 18 не поступит, Таким образом, запись информации при нтором способе кодирования производится за один такт, чтение приотсутствии ошибок — за один такт, а при наличии ошибки — за три такта (чтение, запись инверсного кода, чтение).

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, первый коммутатор, группу элементов

И, выходной регистр, блок контроля достоверности информации, блок управ-5> ления и блох вывода данных, выходы которого являются информационными выходами устройства, причем информационные входы накопителя соединены с выходами первого коммутатора, первый управляющий вход которого подключен к первому выходу блока управлеиия, второй выход которого соединен с первыми входами элементов И группы, вторые входы которых подключены к информационным выходам накопителя, прямые информационные выходы выходного регистра соединены с входами блока контроля достоверности информации и одними из . входов блока вывода данных, первый управляющий вход которого подключен к третьему выходу блока управления, о т л и ч а ю щ е е с я тем, что, с целью:повышения быстродействия, в него введены блок формирования признака четности, второй коммутатор, входной регистр, триггеры, блок сравнения и элементы И, причем первый вход блока управления является первым управляющим входом устройства, одни из входов второго коммутатора являются информационными нходами устройства, а выходы соединены с входами входного регистра и блока формирования признака четности, вы ход которого подключен к первому входу первого элемента И, нторой вход которого соединен с инверсным выходом первого триггера, а выход— с контрольным входом входного регистра, прямые выходы которого подключены к одним из входов первого коммутатора и блока сравнения, другие входы которого соединены с прямыми информационными выходами выходного регистра, прямой выход первого триггера подключен к второму управляющему входу первого коммутатора и нторому входу блока управления, четвертый выход которого соединен с третьим управляющим входом первого коммутатора, другие входы которого подключены к инверсным выходам входного регистра, вход второго триггера соединен с ныходом одного иэ элементов. И группы, а инверсный выход — с первым входом второго элемента И, второй вход которого подключен к выходу блока контроля достоверности информации, а выход — к третьему входу блока управления, четвертый вход которого соединен с выходом блока сравнения, пятый и шестой выходы блока управления подключены к управляющим нхо"

S 1 дам второго коммутатора, другие входы которого соединены с инверсными информационными выходами выходного регистра и другими входами блока вывода данных, второй управляющий вход которого подключен к седьмому выходу блока управления, выходы других элементов И группы соединены с входами выходного регистра, прямой и инверсный контрольные выходы которого подключены соответственно к третьему управляющему входу блока вывода данных и контрольному входу блока контроля достоверности инфор265860 Ь мании и к четвертому управляющему входу блока вывода данных, пятый и шестой управляющие входы которого соединены с прямым и инверсным выходами блока вывода данных, пятый и шестой управляющие входы которого соединены с прямым и инверсным выходами второго триггера, входы первого триггера и пятый и шестой вхоt0 ды блока управления являются другими управляющими входами устройства, контрольным выходом которого является восьмой выход блока управления.

Составитель Г.Зайцева

Редактор Н.Егорова Техред Д.Сердкщова Корректор М.Максимишинец

Заказ 5672/51 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород»; ул. Проектная, 4