Устройство для поверки ваттметров

Иллюстрации

Показать всеРеферат

Изобретение относится к области электроизмерительной техники. Может быть использовано при поверке электроизмерительных приборов. Цель изобретения - повышение точности устройства . В устройство, содержащее источник 5 напряжения, источник 12 тока, фазозадающую цепь, образцовый 11, поверяемый 7 приборы, для достижения цели введены генератор 1 эталонной частоты, ключ 2, перестраиваемый делитель 9 частоты, прецизионные делители 6 напряжения и 13 тока, коммутаторы 4 напряжения и 10 тока, микропроцессор 8, а фазозадакяцая цепь выполнена в виде управляемой линии 3 задержки. В материалах изобретения раскрыт возможный вариант построения микропроцессора 8. Импульсные последовательности поступают на соответствующие измерительные цепи поверяемого 7 и образцового 11 приборов. Показания приборов вводятся оператором в микропроцессор 8, которым и осущесто вляется вычисление значений погрешностей в поверяемой отметке и сравне- /Л ния их с допустимыми с целью определения соответствия поверяемого прибора 7 установленному классу точноети . 1 з.п. ф-лы, 2 ил.г

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5ц 4 G Ol К 35/00,.7

I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОЬЮ СВИДЕТЕЛЬСТВУ

БТ! Л".".

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3890069/24-21 (22) 30.04.85 (46) 30.10.86. Бюл. У 40 (72) В.Н.Чинков, В.И.Анохин, В.Г.Разладов и И.10.Курганцев (53) 621.317.7.089.6(088.8) (56) Авторское свидетельство СССР

Ф 798656, кл. G 01 R 35/00, 1981.

Авторское свидетельство СССР

9 789960, кл. G 01 К 35/00, 1980. (54) УСТРОЙСТВО ДЛЯ ПОВЕРКИ ВАТТМЕТРОВ (57) Изобретение относится к области электроизмерительной техники. Может быть использовано при поверке элек-. троизмерительных приборов. Цель изобретения — повышение точности устройства. В устройство, содержащее источник 5 напряжения, источник 12 тока, фазозадающую цепь„ образцовый 11, поверяемый 7 приборы, для достижения

Л0„„1267312 А 1 цели введены генератор 1 эталонной частоты, ключ 2, перестраиваемый делитель 9 частоты, прецизионные делители 6 напряжения и 13 тока, коммутаторы 4 напряжения и 10 тока, микропроцессор 8, а фазозадающая цепь выполнена в виде управляемой линии 3 задержки. В материалах изобретения раскрыт возможный вариант построения микропроцессора 8. Импульсные последовательности поступают на соответствующие измерительные цепи поверяемого 7 и образцового 11 приборов. Показания приборов вводятся оператором в микропроцессор 8, которым и осуществляется вычисление значений погрешностей в поверяемой отметке и сравнения их с допустимыми с целью определения соответствия поверяемого при- С, бора 7 установленному классу. точности. 1 з.п. ф-лы, 2 ил.

lasL

1 1

Изобретение относится к электроизмерительной технике и преимущественно может быть использовано при поверке электроизмерительных приборов.

Цель изобретения — повышение точности устройства.

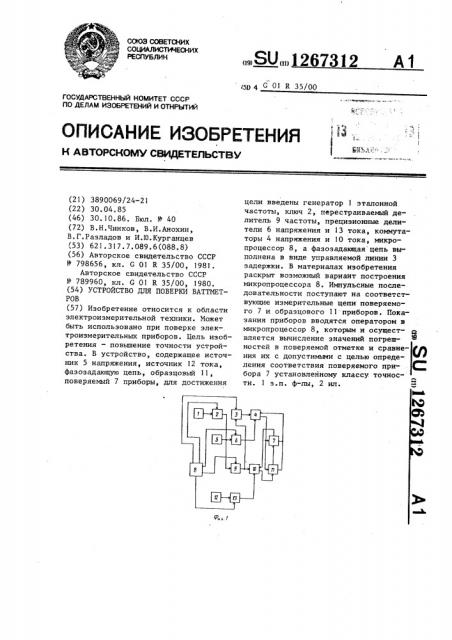

На фиг.! изображена функциональная электрическая схема устройства, на фиг.2 — схема микропроцессора, вариант исполнения.

Устройство содержит генератор 1 эталонной частоты, ключ 2, управляемую линию 3 задержки, коммутатор 4 напряжения, источник 5 напряжения, прецизионный делитель 6 напряжения, поверяемый прибор 7, микропроцессор

8, перестраиваемый делитель 6 частоты, коммутатор 10 тока, образцовый прибор 11, источник 12 тока и прецизионный делитель 13 тока, причем вы.ход генератора 1 эталонной частоты соединен с входом ключа 2, выход которого подключен к информационному входу перестраиваемого делителя 9 частоты„ а управляющий вход — к первому выходу микропроцессора 8, вторым выходом соединенного с управляющим входом управляемой линии 3 задержки, информационный вход которой соединен с точкой, объединяющей выход перестраиваемого делителя 9 час" тоты и управляющий вход коммутатора

10 тока., а выход подключен к управляющему входу коммутатора 4 напряжения, своими выходами подключенного к параллельно соединенным измерительным цепям напряжения образцового 11 и поверяемого 7 приборов, последовательно соединенные измерительные цепи тока. которых подключены к выходам коммутатора 10 тока, по информационному входу соединенного с выходом прецизионного делителя 13 тока, информационный вход которого соединен с выходом источника 12 тока, а управляющий — с пятым выходом микропроцессора 8, своим третьим выходом подключенного к управляющему входу прецизионного делителя 6 напряжения, информационный вход которого соединен с выходом источника 5 напряжения, а выход — с информационным входом коммутатора 4 напряжения, микропроцессор 8 по своему четвертому выходу подключен к управляющему входу перестраиваемого делителя 9 частоты., Микропроцессор 8 содержит формирователь 14 адресных шйн, оперативное

267312 2

10

50 запоминающее. устройство 15, блок 16 управления передачей данных, микропрограммную память 17, первый буферный регистр 18, центральный процессорный элемент 19, блок 20 микропрограммного управления, генератор 21 тактовых импульсов,, блок 22 приоритетных прерываний и второй буферный регистр 23. При этом в микропроцессоре 8 выход генератора 21 тактовых импульсов соединен с точкой, объединяющей первый вход второго буферного регистра 23, первый вход блока

22 приоритетных прерываний и первые входы блока 20 микропрограммного управления и центрального процессорного элемента 19, первым выходом подключенного к второму входу .блока 20 микропрограммного управления, по первому выходу соединенного с входом микропрограммной памяти 17, первый и второй выходы которой подключены соответственно к первым входам формирователя 14 адресных шин и блока 16 управления передачей данных, по первому выходу соединенного с вторым входом центрального процессорного элемента 19, вторым выходом подключенного к второму входу формирователя 14 адресных шин, выход которого соединен с первьпч входом оперативного запоминающего устройства 15, своим выходом подключенного к третьему входу блока 16 управления передачей данных, вторым выходом соединенного с третьим входом блока 20 микропрограммного управления, четвертый вход которого подключен к третьему выходу микропрограммной памяти 17 по четвертому выходу соединенной через первый буферный регистр 18 с третьим входом центрального процессорного элемента 19, третьим выходом подключенного к второму входу блока 16 управления передачей данных, соединенного по третьему выходу с вторым входом оперативного запоминающего устройства 15, а четвертый вход центрального процессорного элемента 19 через второй буферный регистр 23 подключен к выходу блока 22 приоритетных прерываний, по второму входу соединенного с вторым выходом блока 20 микропрограммного управления.

Формирователь 14 адресных шин предназначен для организации передачи данных между центральным процессорным элементом 19, оперативным за3 1

1 поминающим устройством 15 и внешними абонентами.

Оперативное запоминающее устройство 15 служит для промежуточного хранения информации о внешних абонентах и результатов операций, выполняемых центральным процессорным элементом

19. Оно выполнено на микросхемах серии К565РУ2 и набирается платами емкостью по четыре килобайта каждая.

Дешифрация плат, а также адресация внутри плат осуществляются адресом, образуемым на адресных шинах цент- рального процессорного элемента 19.

Блок 16 управления передачей данных предназначен для организации обмена информацией узлов микропроцессора 8 между собой, а также с внешними абонентами. Ha его основе организуется интерфейс ввода — вывода информации °

Микропрограммная память 17 необходима для записи и хранения микропрограмм работы устройства и реализована на микросхемах КР556РТ4 в виде "страниц" матричного типа.

Буферный регистр 18 микрокоманд предназначен для промежуточного хранения разрядов микрокоманды, считываемой из микропрограммной памяти 17.

Такое включение обеспечивает совмещение цикла выполнения текущей микрокоманды, хранимой в буферном регистре

18 микрокоманд, и выбора адреса следующей микрокоманды, что позволяет существенно увеличить скорость выполнения программ, т.е. повысить быстродействие микропроцессора 8.

Основным узлом микропроцессора 8 является 32-разрядный центральный процессорный элемент 19, реализованный на элементах К589ИКО2 с элементами ускоренного переноса К589ИКОЗ и непосредственно выполняющий требуемые арифметические операции. Управление центральным процессорным элементом 19 осуществляется микропрограммно стандартным для серии К589 способом. Код микрокоманды передается по первому входу центрального процессорного элемента 19 и состоит из двух полей — функциональной группы (Fгруппы), определяющей тип выполняемой операции, и группы регистров (R-группы), определяющей, какой из внутренних регистров участвует в операции.

Блок 20 микропрограммного управления,. выполненный на основе микро267312 4 схемы К589ИК01, служит для управления последовательностью выборки микрокоманд нз микропрограммной памяти

17, а также для управления тремя регистрами флажков, которые используются для органиэации условных переходов по признакам, вырабатываемым центральным процессорным элементом

19. При этом используется стандарт10 ная система переходов к следующему адресу микрокоманды.

Генератор 21 тактовых импульсов необходим для задания временной сетки работы микропроцессора 8.

Блок 22 приоритетных прерываний предназначен для организации прерывания основной программы и перехода к выполнению подпрограммы по командам оператора.

Буферный регистр 23 .служит для осуществления временной развязки между выполнением операции прерывания в центральном процессорном элементе 19 и выдачей кода следующего прерывания.

Процесс поверки осуществляют следующим образом.

Оператор осуществляет ввод в микропроцессор 8 значений коэффициента мощности, частоты поверочного сигнала и поверяемой отметки. После этого микропроцессор 8 производит установку коэффициентов деления прецизионных делителей 6 и 13 напряжения и тока в соответствии со значением поверяемой отметки; задает коэффициент

35 деления перестраиваемого делителя 9 частоты, исходя из требуемой частоты поверочного сигнала; определяет значение временной задержки ht по формуле

40 Р 2Т ТТ

ht

23т 1Г где at — временной сдвиг между испытательными сигналами напря45 жения и тока;

2Т вЂ” период испытательного сигнала; ц — фазовый сдвиг между векторами напряжения и тока в по50 веряемом приборе.

Полученное значение t записывается в управляемую линию 3 задержки.

После выполнения указанных операций микропроцессором 8 формируется сигнал, по которому открывается ключ

2 н импульсы с выхода генератора 1 эталонной частоты начинают поступать на информационный вход перестраиваеный вход управляемой линии 3 задержки и на управляющий вход коммутатора

10 тока. Коммутатором 10 тока производится коммутация подаваемого на

его информационный вход уровня пос10 тоянного тока с положительного значения на отрицательное и наоборот. Уп" равляемая линия задержки 3 служит для задания фазового сдвига между векторами напряжения и тока. Таким образом, на управляющий вход коммутатора 4 напряжения импульсы поступают с требуемой временной задержкой. Ком- 2о мутатор 4 напряжения производит попеременное переключение уровня постоянного напряжения с положительного значения на отрицательное и наоборот. уровни постоянного напряжения и тока поступают на информационные входы коммутаторов 4 и 10 напряжения и тока от источников 5 и 12 напряжения и тока соответственно через прецизионные делители 6 и 13 напряжения и тока. Прецизионными делителями 6 и 13 напряжения и тока осуществляется установка требуемых амплитудных значений формируемого сигнала. Для этого на их управляющие входы с микропро30

35 цессора 8 поступают коды коэффициентов деления, изменяющиеся в соответствии с номером поверяемой отметки.

Таким образом, на выходах прецизионных коммутаторов 4 и 10 напряжения и тока формируются последовательности импульсов прямоугольной формы типа "меандр". Закон их формирования имеет вид

45,Г а, 0(1: y; (-а, Т

1-Ь, Т гт, 50 где а — амплитудное значение испытательного сигнала напряжения;

Ъ вЂ” амплитудное значение испытательного сигнала тока.

Сформированные импульсные последовательности поступают на соответствующие измерительные цепи поверяемого 7 и образцового .11 приборов. Показания приборов вводятся оператором в

5 12673 мого делителя 9 частоты, которым производится деление поступающей на его вход импульсной последовательности в соответствии с требуемым значением частоты поверочного сигнала, С выхода перестраиваемого делителя 9 частоты импульсы поступают на информацион12 Ь микропроцессор 8, которым и осущестas".яется вычисление значений погрешностей в поверяемой отметке и сравнения их с допустимыми с целью определения соответствия поверяемого прибора 7 установленному классу точности. Описанный процесс осуществляется во всех поверяемых отметках.

Микропроцессор 8 работает следующим образом.

По пусковой команде с блока 16 управления передачей данных в блок

20 микропрограммного управления поступает сигнаЛ, инициирующий формирование первого адре< а микрокоманды, поступающего на адресные шины микропрограммной памяти !7. На информационных выходах микропрограммной памяти 17 формируется код первой микрокоманды, поле которой„ содержащее

26 бит, условно можно разбить на следующие составляющие: 7 бит — для управления выбором адреса следующей микрокоманды," 1 бит — функция загрузки адреса микрокоманды; 4 бита — для управления признаками (флагами) блока 20 микропрограммного управления;

7 бит — код микрофункции, реализуемой центральным процессорным элементом 19; 1 бит реализует условную синхронизацию, 1 бит подается на шину маски; 2 бита используются для управления прерываниями, разрешая соответственно запись и считывание када уровня приоритета выполняемой программы; 3 бита предназначены для управления передаей данных посредством формирователя 14 адресных шин и блока 16 управления передачей данных между центральным процессорным элементом 19, оперативным запо мнающим устройством 1 1 и внешними блокаКод микрофункции по четвертому выходу микропрограммной памяти 17 поступает на первый вход блока 20 микропрограммного управления и гредставляет собой условие, по которому выбирается следующий адрес микрокоманды. Блок 20 микропрограммного управления, анализируя состояние этого входа, а †:акже второго и третьего входов, подключенных соответственно к второму выходу блока 16 управления передачей данных и первому выходу центрального процессорного элемента

19, формирует адрес следующей микрокоманды. Эта операция повторяется

7 12673 при выполнении всей программы работы.

Последовательность кодов, формируемая на третьем выходе микропрограммной памяти 17, поступает на вход буферного регистра 18 микрокоманд и далее на первый вход центрального процессорного элемента 19. В соответствии с поступающими кодами центральным процессорным элементом 19 выполняется последовательность опера- 10 ций, представляющих собой программу обработки входных данных. Помимо этого центральным процессорным элементом 19 по второму и третьему выходам формируются адрес и код разрешения, поступающие на вторые входы формирователя 14 адресных шин и блока 16 управления передачей данных. В зависимости от управляющих сигналов, формируемых на первом и втором выходах 20 микропрограммной памяти 17 и поступающих на первые входы формирователя

14 адресных шин и блока 16 управления передачей данных, происходит их совместная или избирательная инициа- 25 лизация. В дальнейшем входная информация, поступающая по магистрали С в блок 16 управления передачей данных, транслируется последней либо в оперативное запоминающее устройство 30

15, либо по второму входу в центральный процессорный элемент 19. Формирование адресов записи информагии в оперативное запоминающее устройство

15 производится центральным процессорным элементом 19 совместно с формирователем 14 адресных шин. При работе микропроцессора 8 обмен данными и результатами вычислений между оперативным запоминающим устройством 15,40 центральным процессорным элементом

19 и внешними абонентами осуществляется посредством бгока 16 управления передачей данных.

Формула изобретения

1. 1 стройство для поверки ваттметров, содержащее фазозадающую цепь, источники напряжения и тока, клеммы для подключения поверяемого прибора и образцовый прибор, измерительная цепь тока которого подключена к клемме для подключения токовой цепи поверяемого прибора, о т л и ч а ю- у щ е е с я тем, что, с целью повышения точности, в него введены генератор эталонной частоты, ключ, пере12 8 страиваемый делитель частоты, прецизионные делители напряжения и тока, коммутаторы напряжения и тока и микропроцессор, а фазозадающая цепь выполнена в виде управляемой линии задержки, причем выход генератора эталонной частоты соединен с входом ключа, выход которого подключен к информационному входу перестраиваемого делителя частоты, а управляющий вход — к первому выходу микропроцессора, вторым выходом соединенного с управляющим входом управляемой линии задержки, информационный вход которой соединен с выходом перестраиваемого делителя частоты и управляющим входом коммутатора тока, а выход подключен к управляющему входу коммутатора напряжения, своими выходами подключенного к клеммам для подключения измерительных цепей напряжения поверяемого прибора и измерительным цепям напряжения образцового прибора, измерительная цепь тока которого подключена к выходу коммутатора тока, информационный вход которого соединен с выходом прецизионного делителя тока, информационный вход которого соединен с выходом источника тока, а управляющий — с пятым выходом микропроцессора, своим третьим выходом подключенного к управляющему входу прецизионного делителя напряжения, информационный вход которого соединен с выходом источника напряжения, а выход — с информационным входом коммутатора напряжения, микропроцессор по своему четвертому выходу подключен к управляющему входу перестраиваемого делителя частоты, а вторая клемма для подключения измерительной цепи тока поверяемого прибора подключена к входу коммутатора тока.

2. Устройство, по п.1, о т л и— ч а ю щ е е с я тем, что микропроцессор содержит формирователь адресных шин, оперативное запоминающее устройство, блок управления передачей данных, микропрограммную память, первый и второй буферные регистры, центральный процессорный элемент, блок микропрограммного управления, блок приоритетных прерываний и генератор тактовых импульсов, выход которого подключен к первому входу второго буферного регистра, первому

Составитель А.Заборня

Техр ед И. По по в кч

Редактор Л.Повхан

Корректор N. Пожо

Заказ 5768/42

Тираж 728

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

9 12673 входу блока приоритетных прерываний и первым входам блока микропрограммного управления и центрального процессорного элемента, первым выходом подключенного к второму входу блока 5 микропрограммного управления, по первому выходу соединенного с входом микропрограммной памяти, первый и второй выходы которой подключены соответственно к первым входам формиро- 10 вателя адресных шин и блока управления передачей данных, по первому выходу соединенного с вторым входом центрального процессорного элемента, вторым выходом подключенного к второ- 1 му входу формирователя адресных шин, выход которого соединен с первым входом оперативного запоминающего уст" ройства, своим выходом подключенного к третьему входу блока управления передачей данных, вторым выходом соединенного с третьим входом блока микропрограммного управления, четвертый .вход которого подключен к третьему выходу микропрограммной памяти, по четвертому выходу соединенной через первый буферный регистр с третьим входом центрального процессорного элемента, третьим выходом подключенного к второму входу блока управления передачей данных, соединенного по третьему выходу с вторым входом оперативного запоминающего устройства, а четвертый вход центрального процессорного элемента через второй буферный регистр подключен к выходу блока приоритетньж прерываний, по второму входу соединенного с вторым выходом блока микропрограммного управления.