Стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике , в частности к источникам вторичного электропитания. Цель изобретения - повышение надежности. Защитньй транзистор 11 заперт при нормальном режиме нагрузки. При определенном завышенном токе нагрузки напряжение на ограничительном резисторе 6 открывает транзистор 11.,Стабилитрон 9 источника 8 опорного напряжения шунтируется. Ток перегрузки начинает снижаться. 1 ил. (Л tc О5 со СХ) со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5D 4 С 05 F !/569

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2 1) 3914238/24-07 (22) 24.06.85 (46) 30.10.86. Бюл. Р 40 (71) Киевское научно-производственное объединение "Аналитприбор" (72) С.Т.Дремов, Г.М.Сычев и Л.Я.Дюкова (53) 621. 316. 722. 1 (088. 8) (56) Авторское свидетельство СССР

N- 653606, кл. G 05 F 1/58, 1979.

Электроника, 1964, т. 37, Ф 28, M.: Мир, с, ?6.

„„SU„„1267389 А 1 (54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ (57). Изобретение относится к электротехнике, в частности к источникам вторичного электропитания. Цель изобретения — повышение надежности. 3ащитный транзистор 11 заперт при нормальном режиме нагрузки. При определенном завышенном токе нагрузки напряжение на ограничительном резисторе

6 открывает транзистор 11.,Стабилитрон 9 источника 8 опорного напряжения шунтируется. Ток перегрузки начинает снижаться ° 1 ил.

1267389

Заказ 5774/46 Тираж 836 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Изобретение относится к электротехнике и может быть использовано прп проектировании источников вторичного электропитания.

Цель — повышение надежности путем снижения тока короткого замыкания и снижения обратного напряжения на переходе эмиттерного входного транзистора в режиме короткого замыкания.

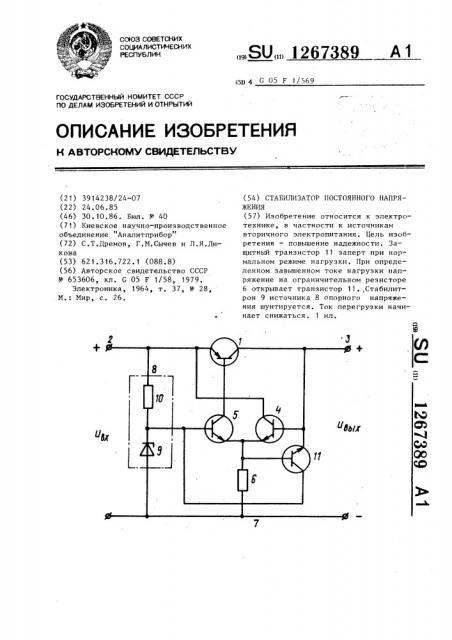

На чертеже представлена электри- 10 ческая схема стабилизатора поетоянного напряжения.

Стабилизатор постоянного напряжения содержит регулирующий транзистор 1, эмиттер которого соединен с 15 входным выводом 2 для подключения питающего напряжения, а коллектор — с выходным выводом 3 для подключения нагрузки, входной транзистор 4 дифференциального усилителя обратной 20 связи, эмиттер которого соединен с эмиттером выходного транзистора 5 дифференциального усилителя обратной связи, и через ограничительный резистор 6 они подключены к общей шине

7, опорный источник 8, выполненный на стабилитроне 9 и резисторе 10 и подключенный выходом к базе транзистора 5 и коллектору защитного транзистора 11, переход эмиттер-база которо- 30 го включен встречно-параллельно переходу эмиттер-база входного транзистора 4, Стабилизатор работает следующим образом, 35

В нормальном режиме нагрузки величины токов, протекающих по эмиттерным цепям входного 4 и выходного

5 транзисторов дифференциального усилителя обратной связи, примерно рав- 40 ны. Защитный транзистор 11 заперт напряжением межцу эмиттерам и базой входного транзистора 4 и не влияет на работу стабилизатора. С повышением тока нагрузки эмиттерный ток вы- 4 ходного транзистора 5 также увеличивается, эмиттерный ток входного транзистора 4 снижается. При снижеьии эмиттерного тока входного транзис. тора 4 до нуля, ток перегрузки начинает ограничиваться, выходное напряжение стабилизатора начинает уменьшаться.

В тот момент, когда выходное наив ряжение стабилизатора станет ниже напряжения на ограничительном резисторе 6., защитный транзистор 11 отпирается и шунтирует стабилитрон Э опорного источника 8. Ток перегрузки стабилизатора начинает снижаться.

Так как напряжение на переходе эмиттер-база защитного транзистора 11 ниже напряжения стабилитрона 9, то ток короткого замыкания значительно снижается, а обратное напряжение, прикладываемое к переходу эмиттербаза входного транзистора 4, ограничивается напряжением эмиттер-база защитного транзистора 11, которое равно (0,5-1) В. В результате повышается надежность стабилизатора постоянного напряжения, формулаизобретения

Стабилизатор постоянного напряжения, содержащий регулирующий транзистор, эмиттер которого соединен с входным выводом и коллектором входного транзистора дифференциального усилителя обратной связи, коллектор соединен с выходным выводом и базой входного транзистора, а база соединена с коллектором выходного транзистора дифференциального усилителя обратной связи, эмиттер которого подключен к эмиттеру входного транзистора и через ограничительный резистор к общей шине, а база подключена к выходу опорного источника, включенного параллельно входным выводам, о тл и ч а ю шийся тем, что, с целью повышения надежности, путем снижения тока короткого замыкания и уменьшения обратного напряжения на переходе эмиттер-база входного транзистора дифференциального усилителя обратной связи в режиме короткого замыкания, в него введен защитный транзистор, переход эмиттер-база ко-. торого включен встречно-параллельно переходу эмиттер-база входного транзистора, а коллектор подключен к базе выходного транзистора дифференциального усилителя ооратной связи.