Ограничитель

Иллюстрации

Показать всеРеферат

Изобретение относится к аналоговой вычислительной технике и радио технике и может быть использовано в различных устройствах радиоэлектроники , автоматики и вычислительной техники. Цель изобретения - повышение быстродействия. Повышение быстродействия достигается за счет подключения ключевого транзистора к входному дифференциальному каскаду операционного усилителя, что позволяет не учитывать время задержки переключения остальных каскадов операционного усилителя при переходе из ли (О нейного режима работы в режим ограничения . 2 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН дд4 G 06 G 7/25

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3831443/24-24 (22) 26.12.84 (46) 30. 10.86. Бюл. Ф 40 (71) Белорусский ордена Трудового

Красного Знамени государственный университет им. В.И.Ленина (72) А.М.Ильянок, И.А.Левко, В,Н.Чуясов и В.Е.Ямный (53) 681.3 (088.8) (56) Авторское свидетельство СССР

У 1092526, кл. G 06 G 7/25, 1982.

Авторское свидетельство СССР

11- 620988, кл. G 06 G 7/25, 1977.

„„SU 2 444 А1 (54) ОГРАНИЧИТЕЛЬ (57) Изобретение относится к аналоговой вычислительной технике и радиотехнике и может быть использовано в различных устройствах радиоэлектроники, автоматики и вычислительной техники. Цель изобретения — повышение быстродействия. Повышение быстродействия достигается за счет подключения ключевого транзистора к входному дифференциальному каскаду операционного усилителя, что позволяет не учитывать время задержки переключения остальных каскадов операционного усилителя при переходе из линейного режима работы в режим ограничения. 2 ил.

444 2 жению П„ на входе 4 задания onopt .ого напряжения, !зходной транзистор операционного усилителя открывается и на выходе 5 ограничителя отсле>кивается напряжение

i 267

1!бы Uon теле.

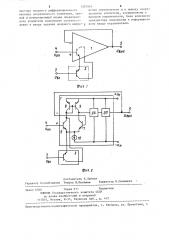

Ограничитель (фиг. 1) содержит 15 операционный усилитель 1 (ОУ),, ключевой транзистор 2, и«формационный

» IÎ, l -1 З<1ДЯНИЯ

> опорного «япряжения, выход 5 ограни>иге !и; на фиг. 2 изображенная мо, ет! -;,лук«я с«адно го оперяциott! toro уст !теля содержит УА-кас.кад усиле.»>тт!Итуды. ЭП вЂ” эмиттерный повто: и =!1,, Первый б и второй 7 транзис2с ! оры входного дифференциального каскада „гервый 8 и второй 9 транзисторы тти»амической нагрузки, гене1за— т >р 10 тока.

Огра»:!чите".I; работает следуюшим обр .. 3(>м. 30 исход!!() I oo cT оя !ие, IIpH отсутст ! (!!и сигна:тя «а входе 3 транзистор

ОУ 1 ..такрыт, ключевой транзистор 2 открыт, так как на базе входного тра»зистсра ОУ присутствует отрица- 1- tt>

-теттьное напряже::!ие входа 4 задания опоp Ho I" напряжения ir ня бале KJI!c чевого транзистора 2 — нулевой потен-! тт!ал. При этом функции входного транТаким образом "остигается . олозистора опера»ионного усилитеття вы- 40 жительный эффект за счет повышения полняет транзистор 2 и на выходе 5 быстродействия. которое в три разя ограничителя отслеживается нулевои превышает быстродействие известного потенциал. При появлении па инфор0 мационном входе 3 ограничителя сигнала U „положительной поляттнсстп (45 r>> (> любой амплитудой либо сигнала отрицательной полярности с амплитудой, меньшей чем напряжение на шине опов— ного напряжения, входной транзистор

ОУ 1 остается в закрытом состоянии„ а транзистор 2 открывает„ ограничитель работает в линейном режиме, при.— чем напряжение на выходе 5 равно! де t, — время !те!>еключения транзистора „ ь>>х ВХ

При появлении на входе 3 ограничителя входного напряжения oTpHIJà— тельной полярности, равного няпряИзобретение oTE oñèòñÿ к аналоговой вычислительной технике и радиотехнике и может быть использовано B различных устройствах радиоэлектроники, автоматики, вычислительной техники.

Цель изобретения — повышение быстродействия, На фиг. 1 предстаьлена функциональная схема ограничителя; на фиг ° 2 — 10 вариант структурной схемь! ограничителя, иллюстрируюший его выполнение на двухкаскадном операционном усилиПри дальнейшем росте входного напряжения в отрица" ельную сторо»у ключевой тр >нзистор 2 закрь!вается сграничитель переходит в режим ограничения входного напояжения на уровне, равном U При э..ом на выходе ограничителя постоянно поддерживается напряжение Ьоп

Быстродействие ограничителя опре— деляется временем задержки, необходитть!1! дпя т!ерекл!оче»-я огра»ичителя из линейного режима пропускания входного сигнала в режим ограничения или, наоборот, из режима ограничения в режим пропускания „

Как показано рянее, в данном ограничителе для коммутации в линейном режиме работы транзистор 2 подключается вместо входного транзистора

ОУ 1, который выпс>лняет свои функции в ОУ 1 в реж>!ме ограничения входного сигнала. При этом остальные каскады

ОУ не принимают участия в процессе коммутации. )1оэтому время задержки перектпочсния для данного ограни ителя ч! со -ср онный усилитель., »а первом и втором транзисторах вход .or o диффере«циальс того каскада, ба зы кот орых я вля ются

:. оот ветстве «но пря мым и и«вертирук>щим входами оп ер аттис«но го усилителя, И КЛЮЧЕВОЙ тРа«ЗИстОР, О т JI И Ч Яю шийся тем, что, с целью у»роше ния H повыше ния бь>стр одействия, эмиттер и коллектср ключевого -.pa«зистора подключены соответственно к ..>миттеру и коллектору первого тра«1267444 4 же пня ограничителя z» к выходу операционного усилителя, соединенному с выходом ограничителя, база ключевого транзистора подключена к информционному входу ограничителя. зистора входного дифференциального каскада операционного усилителя, прямой и инвертирующий входы операционного усилителя подключены соответственно к входу задания опорного напря —

/Х

Составитель Н. Зайцев

Редактор Н.Слободяник Техред Л.Олейник Корректор В.Синицкая

Заказ 6300 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4