Устройство для управления шаговым двигателем с дроблением шага

Иллюстрации

Показать всеРеферат

Изобретение относится к управлению шаговыми двигатели. Цель изобретения - упрощение и повышение надежности устройства для упра вления шаговым двигателем с дроблением шага. Устройство содержит распределитель импульсов 1, логические элементы И 2 по числу фаз двигателя, усилители мощности 3, коммутирующие фазы 4 двигателя , блок 5 дробления шага. Блок 5 включает реверсивный счетчик 6, логический элемент ИЛИ 7, двоичный счетчик 8, мультиплексор 9, логарифмический счетчик 10. Счетчик 10 содержит двоичный счетчик 11, позиционный счетчик 12, логический элемент ИЛИ 13, логические элементы И 14. Все логические узлы устройства имеют количество входов и выходов меньше коэффициента дробления шага, что позволяет реализовать устройство на нес скольких интегральных схемах распрос траньнных серий, приводя к упрощению (Л и повышению надежности. 1 з.п. ф-лы, 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (su 4 Н 02 Р 8/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР по делАм изОБРетений и ОткРытий

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3841295/24-07 (22) 07.01.85 (46) 30.10.86. Бюл. 9 40 (72) В.В.Ледерер и А.В.Мирошников (53) 621.313.525(088.8) (56) Авторское свидетельство СССР

В t037409, кл. Н 02 P 8/00, 1983.

Авторское свидетельство СССР

У 993428, кл. Н 02 Р 8/00. 1983. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОBbIM ДВИГАТЕЛЕМ С ДРОБЛЕНИЕМ ШАГА (57) Изобретение относится к управлению шаговыми двигателями. Цель изобретения — упрощение и повышение надежности устройства для управления шаговым двигателем с дроблением шага.

Устройство содержит распределитель импульсов 1, логические элементы И 2

„„SU„„1267583 А1 по числу фаз двигателя, усилители мощности 3, коммутирующие фазы 4 двигателя, блок 5 дробления шага ° Блок

5 включает реверсивный счетчик 6, логический элемент ИЛИ 7, двоичный счетчик 8, мультиплексор 9, логарифмический счетчик 10. Счетчик 10 содержит двоичный счетчик 11, позиционный счетчик 12, логический элемент

ИЛИ 13, логические элементы И 14. Все логические узлы устройства имеют количество входов и выходов меньше коэффициента дробления шага, что позволяет реализовать устройство на нескольких интегральных схемах распрос- Я тран нных серий, приводя к упрощению и повышению надежности. 1 з.п. ф-лы, 1 ил.

С:

12

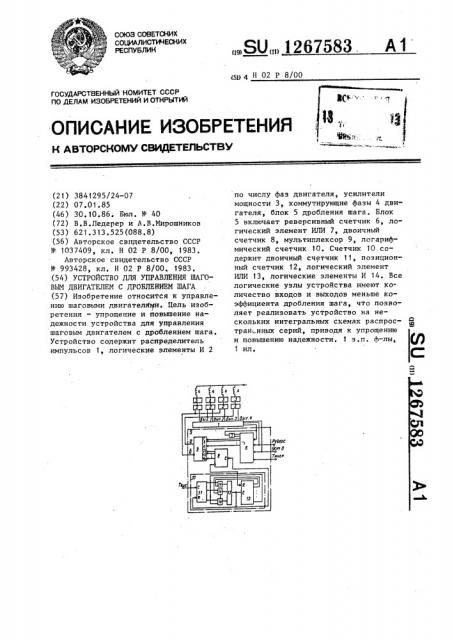

Изобретение относится к управлению электрическими машинами, а именно шаговыми двигателями, и может быть использовано на дискретном электроприводе повышенной точности, Цель изобретения — упрощение и повышение надежности, На чертеже приведена функциональная схема устройства применительно к четырехфазному шаговому двигателю.

Устройство содержит распределитель

1 импульсов, логические элементы И 2 по числу фаз двигателя, связанные выходами с входами усилителей 3 мощности, коммутирующих фазы 4 шагового двигателя, а первыми входами — с выходами распределителя 1, блок > дробления шага, подключенный прямым и инверсным выходами к вторым входам элементов И.2, Блок 5 дробления шага вклточает реверсивный счет >>>>с 6, выходы заема и переноса каторагo через логический элемент ИПИ 7 подклн>челы к его входу автореверсирования и одновременна к тактовому входу распределителя 1, а входы счетттьттт,, установки в исходное состочние и ручного ре. версиравания — к соответствующим шинам управления " 1 „„ ", "Уст. О" и Реверс", двоичный счетчик 8, мультиплексор 9п каналов IIa один, логарифмический счетчик 10. Управ.>тяющие (адресттьте) входы мультиплексора 9 подключены к выходам двоичных разрядов счетчика 8, а коммутируемые — к выходам двоичных разрядов реверсттв>того счетчика 6. Прямой О и инверсный

Я выходы мультиплексора 9 подключены к вторым входам элементов И 2, взятых через один, Счетный вход счетчика 8 подключен к выходу,ттогарифмического счетчика, вход катарага соединен с шиной "Т ы ", >Ia котоРУю иостУпают импульсы высокой частоты. Логарифмический счетчик 1 0 сод, ержит,двоичный счетчик 11, счетным входам соединенный c IIIHHoH "T. LIb, ", I>03HLlIIo>II>I >>1 cтт;а 12 и с входом установки в исходно= состояние двоичного с тетчика 1 I, лагште-. ские элементы И 14, выходы которых соединены с входами лагического эле:мента ИЛП l3 вторые входы — с выходами разрядов двоичного счетчика 11, а первые входы — с выходами паэициан67583

2 ного счетчика 12. Логарид>мический счетчик 10 подключен входом установки в исходное состояние к выходу переноса счетчика 8, Двоичный счетчик 8 и логарифмический счетчик 10 образуют формирователь адресного кода.

Устройст>зо работает следутошим образом.

В первоначальном состоянии на шину 10 "Уст, 0" падается сигнал установки в исходное состояние. При этом реверсивный счетчик 6 устанавливается в нулевое исходное состояние, а распределитель 1 — в положение, при котором

15 в единичном логическом состоянии находится первая половина его выходов, например для четырехфазнога двигателя выходы "Вых, 1" и "Вых, 2", В соответствии с требуемым направлением

2(? вращения к шине "Реверс" прикладывается единичный или нулевой уровни потенциалов. т">ультиплексор 9 поочередно коммутирует выходы двоичных разрядов ре2 версивнога счет:шка 6 на свой прямой выход О, а на инверсном выходе Т) мультиплексора 9 присутствует инверсный относительно выхода O логический уровень. При этом время, в течение

:?О которого каждый разряд реверсивного счетчика 6 каммутируется на выходы мульгиплексора 9, определяется весом этого разряда и относительно времени коммутации младшего смежного разряда увеличивается вдвое. Например, второй

3 I двоичный разряд реверсивного счетчика 6 коттмутируется мультиплексором 9 тта вреття, в два раза большее времени коммутации младшего первого разряда, а более старший третий разряд ревер4(? сивттс>го счетчика 6 коммутируется на время, в два раза большее времени коммутации второго разряда и в четь>ре раза больше времени коммутации первого разряда. Такитт образам, длитель45 пасть коммутации различных разрядов ре>ззрсивного счет-.йка 6 мультиплексо- рам 9 соотносятся между собой так же, как и веса соответствующих двоичных разрядов.

5т>

Для реа>тизации описанного закона коммутации выходов реверсивного счет"-шка 6 мультиплексором 9, праизнадяII)IIII ee согласно двоичному коду на его управляющих входах, подключенных к выходам счетчика 8, на счетный вход последнего подаются импульсы с соединенного с ниы выхода логарифмического

6?583

1О

15 счетчик 11 число два, и появившийся

30 входами с выходами элементов И 14, также появляется единичный логический уровень, который по цепи обратной связи поступает на вход установки в исходное состояние двоичного счетчика

11 и устанавливает его выходы в нулелевое состояние, что приводит к установлению нулевого логического уровня на выходах элемента ИЛИ 13. С выхода последнего импульс поступает на счетный вход двоичного счетчика 8. На вы40 ходе его до поступления импульса существовал нулевой кодовый набор, сообщаемый управляющим входам мультиплексора 9, в соответствии с которым мультиплексор 9 коммутировал на свой выход, подключенный к своему первому входу, напряжение первого выхода реверсивного счетчика 6. После поступления импульса на счетный вход двоичного счетчика 8 на его выходах и на управляющих входах мультиплексора 9 появляется единичный кодовый наббр, в соответствии с которым мультиплексор

9 коммутирует на свой выход напряжение второго выхода реверсивного счетчика 6. Импульс с выхода элемента ИЛИ

13 поступает также на счетный вход позиционного счетчика 12, который пе3 12 счетчика 10. На счетный вход двоичного счетчика 11 непрерывно поступают с шины Т„, импульсы высокой частоты, Рассмотрение работы счетчика 10 начинается с момента, когда, например, с выхода переноса счетчика 8 импульсный сигнал переполнения последнего поступает на вход установки в исходное состояние позиционного счетчика 12. Последний устанавливается в состояние, при котором единичный логический уровень присутствует только на первом позиционном выходе, соединенном с входом элемента И 14, другой вход которого подключен к первому выходу двоичного счетчика 11. Двоичный счетчик 8 самостоятельно устанавливается в нулевое исходное состояние в момент выработки им сигнала переполнения. Первый же импульс на шине

1Т „, устанавливает двоичный счетчик 11 в единичное состояние, Появившийся при этом на его первом выходе единичный логический уровень приводит к появлению единичного логического уровня на выходе элемента И 14, соединенном своими входами с первыми выходами двоичного счетчика 1 I и позиционного счетчика 12. На выходе элемента ИЛИ 13, соединенного своими реходит в свое следующее состояние, характеризующееся наличием единичного . логического уровня только на втором позиционном выходе ° Очередной импульс на шине "Т ц " устанавливает двоичный счетчик 11 в единичное состояние, однако через элемент И 14, подключенный входом к первому выходу двоичного счетчика 11, единичный логический уровень на вход элемента ИЛИ 13 не проходит из-за наличия нулевого логического уровня на другом входе этого элемента И 14. Следующий импульс на шине "Ть,1 " записывает в двоичный на его втором выходе единичный логический уровень появляется на выходе элемента И 14, один вход которого соединен с вторым выходом двоичного счетчика 11, а другой — с вторым позиционным выходом позиционного счетчика 12, имеющим единичный логический уровень. Далее единичный логический уровень появляется на выходе элемента ИЛИ 13, что влечет установку в исходное состояние двоичного счетчика

11, а с выхода элемента ИЛИ 13 импульс поступает на счетный вход счетчика 8 и записывает в него число два, в соответствии с которым мультиплексор 9 коммутирует .на свой выход напряжение третьего выхода реверсивного счетчика. 6. Импульс с выхода элемента ИЛИ 13 поступает также на счетный вход позиционного счетчика 12, который переходит в следующее состояние, характеризующееся наличием единичного логического уровня только на третьем позиционном выходе. Теперь для появления импульса на выходе элемента ИЛИ

13 и коммутации мультиплексором 9 следующего выхода реверсивного счетчика 6 необходимо появление четырех импульсов на шине "T> ". Таким образом, коммутация младшего первого выхода реверсивного счетчика 6 на выход мультиплексора 9 происходит в течение одного периода высокочастотных тактовых импульсов на шине "Т „ ", второго выхода — в течение двух периодов, третьего выхода — в течение четырех периодов, четвертого выхода — в течение восьми периодов и так далее. Длительность коммутации t каждого из двоичных выходов реверсивного счетчика 6 определяется соотношением

Т = (2 — 1 ) ьь1а

Пока на выходах реверсивного счет-25 чика 6 присутствует исходный нулевой кодовый набор, на прямом О выходе мультиплексора 9 постоянно создается нулевой, а на инверсном Ц вЂ” единичные логические уровнИ. В результате взаимодействия этих сигналов с единичными сигналами на выходах "Вых. 1" и

"Вых. 2" распределителя 1 на выходе элемента И 2 первого канала создается единичный уровень. Усилитель 3 мощно- .

35 сти первой Аазы 4 двигателя обеспечивает при этом протекание в ней номиEI BJI E9 Ho z о T QK B. I

При поступлении на Шину "Т,щ первого управляющего импульса низкой частоты в реверсивном счетчике 6 записывается единица. При этом за период Т коммутации импульсов с выходов счетчика б мультиплексором 9 на прямом выхоДе Q последнего появляется единичный логический уровень на вре45 мя

t = t = 2(ч 1 ) . к ВЫС Sb1( а на инверсном выходе 0 на это же . время t с периодом Т появляется нулевой логический уровень. Эти сигналы с выходов мультиплексора 9, проходя через элементы И 2 к усилителям 3 мощности, создают токи величиной

55

Ò T- t t(2 — 1) t b — tsbic

91 а I .Б

Т ч (21 — 1) t ì, 5 12675 где К . — весовой коэААициент двоичного выхода; — период высокочастотных такьыс товых импульсов на шине

"т

11

" ьыс ° 5

Когда на выходе счетчика 8 набирается максимальный двоичный код, эквивалентный его коэффициенту пересчета и соответствующий коммутации мультиплексором 9 на свой выход последнего старшего разряда реверсивного счетчика 6, появление очередного импульса на счетном входе счетчика 8 вызывает появление импульсного сигнала переполнения на его выходе переноса. Этот 15 сигнал подается на вход установки в исходное состояние позиционного счетчика 12, и устанавливает счетчик 11 в нулевое состояние. Описанный цикл коммутации импульса выходов реверсив- 20 ного счетчика 6 мультиплексором 9 повторяется непрерывно с периодом

83.

N-1 — --- аХ ч в первой фазе и

t 6blC

I I,Х

Т ч (2 — 1) 9. ч н во второй Аазе, В последующих тактах поступления импульсов па шину "T„ч, " происходит дальнейший пересчет импульсов в реверсивном счетчике 6 ° 3a период Т на прямом выходе Q мультиплексора 9 появляется единичный логический уровень на суммарное время

И а,:, где а — логический уровень i-го выхода реверсивного счетчика 6 (нуль или единица);

t — время коммутации i-го вьтхода9 имеющего весовой коэАфициент К.

На инверсном выходе Q мультиплексора 9 появляется нулевой логический уровень на это же суммарное время в течение периода Т. Это приводит к

° N-2 к ступенчатому уменьшению тока: †--х

М - 4 2

-- — -"I I ч ааа9 1 н9

N — 3 х I — --- IE, ц 9 N ч 9

I. — в первой Аазе и его увеличе2 3 4 N-2 нию: — Х вЂ” Х - ---I — — -х

"9 N "9 N "9 ° ° 9

N-1 х Х; — — — 1„— во второй Аазе. В

Одновременно с этим на выходе переноса реверсивного счетчика 6 формипоследнем N-м такте этого полуцикла функционирования устройства на выходах реверсивного счетчика б формируется максимальный код, соответствующий его .коэАфициевту пересчета, характеризующийся наличием единичного логического уровня на всех выходах этого счетчика. При этом на прямом

Q и инверсном О выходах мультиплексора 9 присутствук>т соответственно единичный и нулевой логический уровни, в результате на выходе элемента И

2 второго канала создается единичный . логический уровень, а усилитель 3 мощности второй фазы 4 двигателя обе спечивает протекание в ней номинального тока Х,.

Формула изобретения

7 1267583 8 руется единичный сигнал, который че- постоянной времени двигателя, чтобы рез логический .элемент ИЛИ 7 поступа- обеспечить допустимые пульсации тока ет на тактовый вход распределителя 1 при осуществляемой широтно-импульсной и изменяет его состояние так, что модуляции фазных напряжений, единичные логические уровни появляют- Разрядность реверсивного счетчика ся на выходах "Вых. 2" и "Вых. 3" 6, равная числу коммутируемых входов распределителя 1. Одновременно по це- мультиплексора 9, определяется формупи обратной связи через элемент ИЛИ лой

7 на вход автореверсирования реверсивного счетчика 6 поступает единич- п = 1ор (N + 1). ный сигнал, изменяющий первоначальное Разрядность двоичного счетчика 8, направление пересчета. равная числу управляющих входов

Этим завершается первый полуцикл мультиплексора 9, определяется формуфункционирования устройства при кото- лой m = log n, Разрядность двоичного ром эа И тактов поступления импульсов 15 счетчика 11, количество входов эле-. на шину "Т„и „ " в первых двух фазах мента ИЛИ 13 и количество позиционных

4 двигателя осуществляется линейное выходов позиционного счетчика 12 равМ ступенчатое изменение тока — умень- ны и. шение в первой фазе и одновременное В отличие от прототипа все логичеувеличение во второй. Ступенчатое из- 20 ские узлы устройства имеют количество менение тока в смежнык фазах двигате- входов и выходов, меньше коэффициента ля приводит к ступенчатому повороту дробления шага N. Например, мультипсуммарного вектора электромагнитного лексор 9 предлагаемого устройства при момента и соответственно ротора. В при N + 1 = 256 имеет всего n = результате ротор отрабатывает N ppo6- р5 = lop>(N + 1) = 8 коммутируемых и ных шагов величиной m = 1ор и = 3 управляющих входа, что позволяет реализовать его всего на

1 ос

1-ар д одной цифровой интегральной схеме средней степени интеграции, а реалигде L — величина основного шага. зация всего предлагаемого устройства

Второй по цикл ф нкционирования возможна на нескольких интегРальных устройства ан оги ен расс схемах распространенных серий 133, с той лишь разницей, что реверсивный

В то же время мультиплексор счетчик 6 работает в режиме обратного прототипа при N + 1 = 256 должен иметь также 2 6 адресных входов линейн -ступенчато еньшению ка чего необходимо применять более трех во второй фазе 4 и его линейно-ступенчатому увеличению в третьей фазе

4. В такт обнуления, реверсивного должен содержать N — 1 = 254 выхо а. д р = хода.

Этим достигается цель изобретения— счетчика б на его выходе заема выра- 40 упрощение устройства и повышение его батывается импульс, который по цепи надежности. Кроме того, без изменения обратной связи автоматически меняет конструкции легко изменять коэффициего направление счета и переключает . ент дробления от 2 до 2 где К вЂ” чираспределитель 1 в другое состояние.

У

45 сло информационнык входов у мультиНоследующие циклы работы устрой- плексора. ства происходят аналогично описанному первому циклу.

Реверсирование предлагаемого устройства осуществляется путем измене- 1. Устройство для управления шаго.ir 50 ния ранее приложенного на шине Ре- . вым двигателем с дроблением шага, соверс" логического уровня на обратный. держащее распределитель импульсов, При этом изменяются на обратные опи- элементы И по числу фаз двигателя, санные процессы изменения кодов пере- соединенные выходами с входами усилиключения в распределителе 1, реверси- телей мощности, первыми входами — с вном счетчике 6 и мультиплексоре 9. выходами распределителя импульсов, 55

Частота тактовых высокочастотных вторыми вкодами — с прямым и инверсимпульсов на шине "Т ы " выбирается ным выходами блока дробления шага, исходя из величины электромагнитной включающего элемент ИЛИ, реверсивный

Составитель Б.Алфимов

Техред Й.Попович Корректор Л.Пилипенко

Редактор А.Гулько

Заказ 5832/56 Тираж 631 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

9 126 счетчик, соединенный счетным входом с шиной низкочастотных импульсов, а выходами заема и переноса — с входами элемента ИЛИ, подключенного выходом к тактовому входу распределителя импульсов и входу автореверсирования реверсивного счетчика, мультиплексор, прямой выход которого подключен к вторым входам элементов И, взя гых через один, а инверсный выход — к вторым входам остальных элементов И, и формирователь адресного кода, подключенный выходами к адресным входам мультиплексора, о т л и ч а ю щ е ес я тем, что, с целью упрощения и повышения надежности, коммутируемые входы мультиплексора в порядке возрастания номеров соединены с разрядными выходами реверсивного счетчика в порядке возрастания разрядов, формирователь адресного кода снабжен двоичным счетчиком и Логарифмическим счетчиком, счетный вход которого сое7583 0 динен с шиной высокочастотных импульсов, выход со счетным входом двоичного счетчика„ выход которого соединен с адресными входами мультиплексора, 5 а выход переноса — с входом установки логарифмического счетчика в исходное положение °

2. Устройство по п,1, о т л и ч а1р ю щ е е с я тем, что логарифмический счетчик содержит двоичный счетчик, позиционныи счетчик, элементы И по числу разрядов двоичного счетчика и выходов позиционного счетчика, элемент ИЛИ, выход которого соединен со счетным входом позиционного счетчика, выходы элементов И соединены с входами элемента ИЛИ, первые входы— с выходами позиционного счетчика, вторые входы — с выходами разрядов двоичного счетчика, а счетный вход позиционного счетчика соединен с шиной высокочастотных импульсов.