Двухвходовое устройство приоритета

Иллюстрации

Показать всеРеферат

Изобретение предназначено для применения в вычислительных системах при организации доступа двух процессоров к общему ресурсу. Целью изобретения является повьпиение достоверности функционирования. Устройство содержит два элемента ШШ-НЕ, элемент задержки, элемент НЕ, триггер Шмидта и два блока управляемой задержки. Применение последних позволяет обеспечить устойчивую работу устройства при разрешении конфликтных ситуаций независимо от параметS ров используемых элементов. 2 ил. сл

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (!1) А3 (5))4 G 06 F

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

llO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3809122/24-24 (22) 01.09.84 (46) 07. 11,86. Бюл. № 41 (71) Ленинградский ордена Ленина политехнический институт им.М.И.Калинина (72) А.К.Березкин (53) 681.325(088.8) (56) Авторское свидетельство СССР № f091162, кл. G 06 F 9/46, 1983.

Варшавский В.И. и Кишеневский М.А

Аномальное поведение логических схем и проблема арбитража. — Автоматика и телемеханика, 1982, ¹ 1, с. 129, рис. За. (54) ДВУХВХОДОВОЕ УСТРОЙСТВО ПРИОРИТЕТА (57) Изобретение предназначено для применения в вычислительных системах при организации доступа двух процессоров к общему ресурсу. Целью изобретения является повышение достоверности функционирования. Устрой- . ство содержит два элемента ИЛИ-НЕ, элемент задержки, элемент НЕ, триггер Шмидта и два блока управляемой задержки. Применение последних позволяет обеспечить устойчивую работу устройства при разрешении конфликтных ситуаций независимо от параметров используемых элементов. 2 ил.

1269132

Изобретение отllo H7сл к вычислиге tEíîé технике и может быть использовано для управления доступом к общему ресурсу двух активных устройств вычислительной системы, например процессоров.

Цель изобретения — повышение достоверности функционирования устройства.

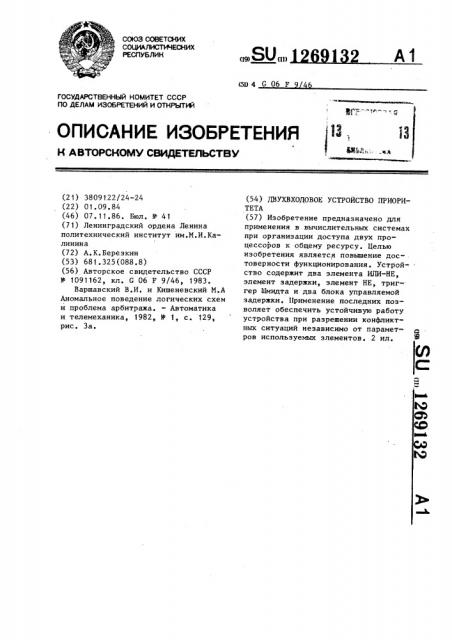

На фиг. 1 приведена функцион:альная схема устройства; на фиг, 2 схема блока управляемой задержки.

Устройство содержит элементы ИЛИНЕ 1 и 2, пороговый элемент (триггер Шмидта) 3, элемент НЕ 4, блоки

5 и 6 управляемой задержки, элемент

7 задержки, входы 8 и 9, выходы

10 и 11.Блоки 5 и 6 содержат элементы И 12, информационный вход 13, управляющий вход 14, выход 15.

Устройство работает следующим образом.

Сигналы запросов поступают на входы 8 и 9 устройства в виде уровней логической "1". Поступление ло- 25 гической "1 на вход 8 приводит к появлению на выходе элемента HE 4 логического 0", который поступает на входы элемента 7 задержки и элемента

ИЛИ-НЕ 1. На выходе последнего об- 30 разуется сигнал логической "1", вызывающий срабатывание порогового элемента 3, на инвертирующем выходе которого формируется сигнал с уровнем логического "0", далее преобра35 зуемый с помощью элемента ИЛИ-НЕ 2 в единичное значение сигнала запроса на выходе 10 устройства. Одновременно с выхода порогового элемента 3 нулевой сигнал поступает на управляющие входы блоков 5 и 6 управляемой задержки, что приводит к запрету прохождения через них сигнала запроса с входа 9 устройства на выход 11.

При поступлении запросного сигнала только на вход 9 устройства он проходит через блоки 5 и 6 управляемой задержки на выход 11, так как на их управляющие входы с выхода порогового элемента 3 поступает логическая единица. Одновременно с выхода блока 5 управляемой задержки сигнал с уровнем " 1" поступает на вход элемента ИЛИ-НЕ 2, запрещая прохождение сигнала запроса с входа 8 уст- M ройства на выход 10.

Рассмотрим режим соревнования, возникающий, когда интервал между поступлением запросов по входам Й и 9 соизмерим с временем срабатывания элементов. В этом случае возможна ситуация„ когда сигналы на входах элемента HJIH-НЕ 1 почти одновременно меняются на противоположные, в результате чего íà его выходе формируется короткий импульс с уровнем логической "1" либо с уровнем, не достигшим полного уровня "1". Если этот импульс не приводит к срабатыванию порогового элемента 3, выход элемента ИЛИ-НЕ 1 остается в состоянии "0" запросный сигнал с входа

9 через блок 6 проходит на выход

11, а прохождение сигнала с входа

8 на выход 10 блокируется уровнем

"1", поступающим на элемент ИЛИ-НЕ

1 с выхода блока 5„

В случае, если импульс на выходе элемента ИЛИ-НЕ 1 вызывает появление импульса на выходе порогового элемента 3, блоки 5 и 6 сбрасываются до того,как успеет возникнуть сигнал на выходе 11. Блок 5 снимает единичный уровень с входа элемента

ИЛИ-НЕ 1, на выходе которого формируется единичный сигнал, вызывающий появление сигнала на выходе 10 устройства. Прохождение сигнала с входа

9 на выход 11 блокируется нулевым уровнем, действующим с выхода порогового элемента 3.

Для надежной работы устройства величина задержки блоков 5 и 6 и элемента 7 должна быть не менее максимального суммарного времени срабатывания элемента ИЛИ-НЕ 1 и порогового элемента 3.

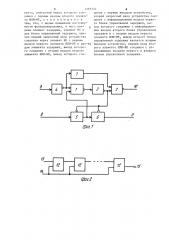

Пример реализации блоков 5 и 6 управляемой задержки в виде цепочки элементов И показан на фиг. 2. Сиг нал с информационного входа 13 проходит на выход 15 через суммарное воемя срабатывания всех элементов И 12 при наличии сигнала на управляющем входе 14. Если в процессе прохождения сигнала на управляющем входе 14 появляется нулевой сигнал, то про— хождение сигнала через элементы И 12 прекращается.

Формула изобретения двухвходовое устройство приоритета, содержащее первый и второй элементы ИЛИ-НЕ, пороговый. элемент, причем выход первого элемента ИЛИНЕ соединен с входом порогового эле1269 мента, инверсный выход которого соединен с первым входом второго элемента ИЛИ,НЕ, о т л и ч à ю ц е е с я тем, что, с целью повьпиения достоверности функционирования, в него введены элемент задержки, элемент Hll u два блока управляемой задержки, причем первый запросный вход устройства соединен через элемент НЕ с первым входом первого элемента ИЛИ-НЕ и вхо- о дом элемента задержки, выход которого соединен с вторым входом второго элемента ИЛИ-НЕ, выход которого сое1З2 4 динен с первым выходом устройства, второй запросный вход устройства соединен с информационным входом первого блока управляемой задержки, выход которого соединен с информационным входом второго блока управляемой задержки и с вторым входом первого элемента ИЛИ-НЕ, выход второго блока управляемой задержки является вторым выходом устройства, первый вход второго элемента ИЛИ-НЕ соединен с управляюцими входами первого и второго блоков управляемой задержки.