Устройство для решения дифференциальных уравнений

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники, к устройствам для обработки цифровьйс данных и может быть использовано для решения дифференциальных уравнений в частных производных. Цель изобретения - повышение быстродействия устройства . Устройство содержит блок ввода-вьтода, блок управления, первую группу блоков двунаправленной передачи данных, где N - . порядок локально-одномерной схемы, блоки 3 3|л,ц1 двунаправленной передачи данных групп с второй по L-ю,

СОЮЗ СОВЕтСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (50 4 G 06 F 15/328

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3702830/24-24 (22) 09.12.83 (46) 07.11.86. Бюп. Н- 41 (71) Институт проблем моделирования в энергетике АН УССР (72) Л.Г.Кириллова, И.И.Петров и А.Е.Степанов (53) 681.32(088.8) (56) Авторское свидетельство СССР

Ф 584314, кл. С 06 F 7/32, 1976.

Авторское свидетельство СССР

Р 1134949, кл. G 06 F 15/328, 1982. (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ

„„Я0„„1269151 А 1 (57) Изобретение относится к области цифровой вычислительной техники, к устройствам для обработки цифровых данных и может быть использовано для решения дифференциальных уравнений в частных производных. Цель изобретения — повышение быстродействия устройства. Устройство содержит блок ввода-вывода, блок управления, первую группу блоков 3 -Зн„ двунаправленной передачи данных, где N — . порядок локально-одномерной схемы, блоки 3 1 -Зп двунаправленной передачи данных групп с второй по L-ю, 1269 где L = gK, h — шаг сеточной области, блоки 4, -41 конечно-разностной модели, процессоры 5,,-5>>+> . Это позволяет разбить исходную задачу на ряд подзадач по расчету поля, вы-!

151 полняемых параллельно со смещением во времени в блоках конечно-разностной модели, что позволяет достигнуть цель изобретения. 9 ил.

Изобретение относится к цифровой вычислительной технике, к устройствам для обработки цифровых данных и может быть использовано для решения дифференциальных уравнений в частных . производных.

Цель изобретения — повышение быстродействия устройства.

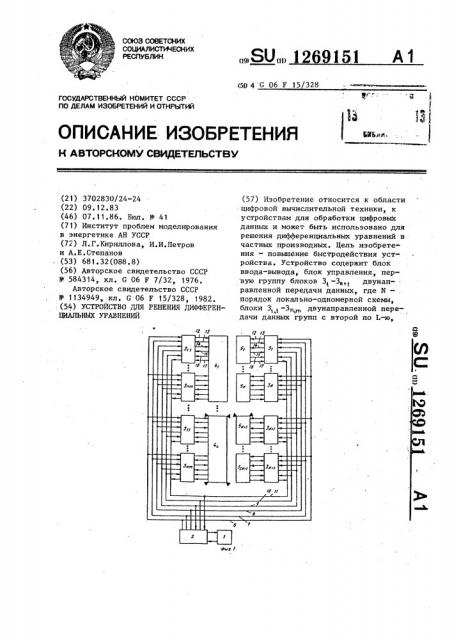

На фиг. 1 представлена структурная схема устройства, на фиг, 2— структурная схема блока конечно-разностной модели; на фиг. 3 — структурная схема узла блока конечно-разностной модели; на фиг. 4 — схема. блока управления; на фиг. 5 — схема блока двунаправленной передачи данных, на фиг„ 6 — функциональная схема процессора, на фиг. 7 - алгоритм работы процессора при вычислении по методу прогонки, на фиг. 8 — то же, при расчете суперпозиции, на фиг. 9 — то же, при вычислении инерционным методом.

Устройство для решения дифференФ циальных уравнений содержит блок 1 ввода-вывода, блок 2 управления,, блоки 3, "З,ц„ двунаправленной пере дачи данных первой группы, блоки

3,;Э„„„ двунаправленной передачи данных Ф-й группы (Р = 2, ..., Тя). .блоки 4, -4 конечно-разностной модели, процессоры 5 -5 „„, первый 6, второй 7, третий 8 выходы блока управления, информационный вход 9 блока управления, четвертый выход 10 блока управления, группу входов 11 запроса блока управления, информацион ный вход 12 процессора, первый вход

13 процессора, вход 14 запроса процессора, второй 15 третий 16 и четвертый 17 выходы процессора„

Блок 4 конечно-разностной модели содержит узлы 18 конечно-разностной модели, которые имеют процессоры 19 и блоки 20 двунаправленной передачи данных.

Блок 2 управления содержит узел

21 памяти, ключи 221 первой группы, ключи 22> второй группы, регистр 23 адреса, регистр 24 команд, счетчик

25 команд, дешифратор 26 команд, регистр 27, узел 28 синхронизации.

Блок двунаправленной передачи данных содержит регистр 29 вывода, первую группу ключей 30, элемент

10 И 31, элемент И 32, дешифратор 33 адреса, вторую группу ключей 34, регистр 35 ввода, элемент И 36, дешифратор 37 адреса, элемент И 38.

Процессор содержит регистр 39 результата, узел 40 синхронизации, регистр 41 второго операнда, регистр

42 первого операнда, дешифратор 43 . команд, счетчик 44 команд, сумматор

20 45, регистр 46 команд, регистр 47 ад, реса, регистр 48 частичного результата, первую группу ключей 49, вторую группу ключей 49, узел 50 памяти.

Устройство работает следующим образом.

В исходном состоянии устройство подготовлено к раббте, т.е. в узле

21 памяти блока 2 управления записа30 ны через блок 1 ввода-вывода 1 уп равляющие программы, массивы коэффициентов, граничные условия, а в . узлах 50 памяти процессоров 5 -5 „,., записаны управляющие программы, Рассмотрим работу устройства на примере двумерного уравнения параболического типа дU 8U 8U — — + (1) бх2 ау

40 заданного в единичном квадрате (О <

< х (1, 0 < y 1), аппроксимируемого методом конечных разностей с использованием локально-одномерных

4 схемe

1269

pht 5p g 5 + заканчивают выполнение функциональных программ в соответствии с алгоритмом, приведенным на фиг. 7.

После того, как выполнено вычисление в любом из процессоров 5 <.

-5„,„ и определено значение поля с шагом Н/2, процессор 5 сообщает об этом блоку 2 управления. Для этого процессор 5 выставляет на шинах 1р

16 адрес блока 3 двунаправленной передачи данных, на шинах 15 данные для передачи в блок 2, а на шине

17 — активный сигнал ЗАПИСЬ. По совокупности этих сигналов блок 3 дву- 15 направленной передачи данных (фиг.5) принимает информацию в регистр 35 и далее управляющим сигналом ЗАПРОС по шине 11 передает управление блоку 2.

Подпрограмма чтения включает выдачу 2р по шинам 8 адрес блока 3 двунаправленной, передачи данных, который поступает на вход дешифратора 33 ад реса, и управляющего сигнала ЧТЕНИЕ по шине 10. По активному сигналу с 25 выхода элемента И 36 информация с регистра 35 через ключи 34 поступает по информационным шинам 9 через буфер ввода-вывода в регистр 27 блока

2, а затем записывается в узел 21 gp памяти. Далее, таким образом, принимаются остальные слова полученного массива из процессора 5 в блок 2 управления.

Аналогично после завершения вычислений каждый из процессоров 5,—

-5, последовательно. передает полученные значения функций в блок 2 управления, который пересылает эти значения через блоки 3 -Зц дву40 направленной передачи данных в процессоры 5 -5N для расчета суперпозиции полученных решений с шагом

Н и Н/2 согласно алгоритму, приведенному на фиг. 8. Результат вычисле45 ния суперпозиции (используется процессорами 5, -5N psrsr расчета одномерных задач с шагом h) из процессоров 5 -5ц через блоки 3, -3 ,двунаправленной передачи данных последовательно передается в узел 21 памяти блока 2 управления, который через блоки 3 -3 д,щ двунаправленной передачи данных последовательно пересылает значения на дополнительных границах в блоки 4, -4ь конечнораэностных моделей, где осуществляется расчет поля итерационным мето151 б дом по алгоритму, приведенному на фиг, 9. Результат расчета поля из процессоров 19 пересылается в блок

2 управления для вывода в блок 1.

Формула из обретения

Устройство .для решения дифференциальных уравнений, содержащее 3N процессоров, где N — порядок локально-одномерной схемы, с первого по

3N-й блоки двунаправленной передачи данных первой группы, с второй по (L+1)-ю группы по mn блоков двунаправленной передачи данных в каждой группе, где Ь = Ь Й, и = h /г

m = h, h — шаг сеточной области, блок управления, блок ввода-вывода, первые информационные входы блока двунаправленной передачи данных с первой по (1 + 1)-ю группы подключены к первому выходу блока управления, первые входы записи блоков двунаправленной передачи данных групп с первой по (L + 1)-ю подключены к второму выходу блока управления, первые адресные входы блоков двунаправленной передачи данных групп с первой по (L + 1)-ю подключены к третьему выходу блока управления, первые входы чтения блоков двунаправленной передачи данных групп с первой по (L + 1)-ю подключены к четвертому выходу блока управления, группа информационных входов блока управления подключена к первым выходам блоков двунаправленной передачи данных групп с первой по (L + 1)-ю, группа входов запросов блока управления подключена к вторым выходам блоков двунаправленной передачи данных групп с первой по (L + 1)-ю, первый выход х-го блока двунаправленной передачи данных первой группы (i — i, ..., 3N) подключен к информационному входу i-го процессора, второй выход i-ro блока двунаправленной ,передачи данных первой группы подключен к входу запроса i-ro процессора, информационные выходы с первого по четвертый i-ro процессора подключены соответственно к второму входу чтения, к второму информационному входу, второму адресному входу и к второму входу записи i-ro блока двунаправленной передачи данных первой группы, при этом блок управления содержит узел памяти, регистр адреса, регистр команд, счетчик команд, 7 1 дешифратор, регистр и узел синхронизации, выход регистра адреса подключен к адресному входу узла памяти, к третьему и пятому выходам блока управления, первый выход узла синхронизации подключен к входу считывания регистра, счетному входу счетчика команд, входам считывания регистра команд и регистра адреса, второй выход узла синхронизации под- . ключен к второму выходу блока управ.ления,. выход регистра команд подключен к входу дешифратора, выход котоI рого подключен к входу запуска узла синхронизации, выход счетчика команд подключен к информационному входу регистра адреса, вход задания режима узла синхронизации подключен к группе входов запросов блока управления, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены L матриц размером n m каждая процессоров и

L матриц размером num каждая блоков двунаправленной передачи данных, первый информационный выход процессора j-й строки (j=1,...,ш) k-ro столбца (k = 1, ..., n) 1-й матрицы процессоров (f = 2...,, 1 + 1) подключен к вторым входам чтения блока двунаправленной передачи данных j-й строки k-ro столбца, блока двунаправленной передачи данных 1-й строки (k + 1)-го столбца, блока двунаправленной передачи данных (j-1)-й строки k-ro столбца, блока двунаправленной передачи данных (j+1)-й строки k-ro столбца Ф-й матрицы блоков двунаправленной передачи данных и к второму входу чтения (j-1)ш +

+ k-ro блока двунаправленной передачи данных t-й группы, второй информационный выкод процессора j-й строки k-ro столбца f-й матрицы процессоров подключен к вторым информационным входам блока двунаправленной передачи данных j -й строки

k-го столбца, блока двунаправленной передачи даннык j-й строки (k+1)-ro столбца, блока двунаправленной передачи данных (j — 1)-й строки k-го столбца, блока двунаправленной передачи данных (j + 1)-й строки k-го столбца -й матрицы блоков двунаправленной передачи данных и к второму информационному входу (j — 1)m +

+ k-ro блока двунаправленной передачи данных Г-й группы, третий инфор2691 51 8

1О

20

50 мационный вход процессора j-й строки

k-ro столбца (-й матрицы процессоров подключен к вторым адресным входам блока двунаправленной передачи данных j é строки k-ro столбца, блока двунаправленной передачи данных j-й строки (k + 1)-го столбца, блока двунаправленной передачи данных (j

1)-й строки k-ro столбца, блока двунаправленной передачи данных (j +

+ 1)-й строки k-го столбца (-й матрицы блоков двунаправленной передачи данных и к второму адресному входу (j — 1)m + k-ro блока двунаправленной передачи данных Е-й группы, четвертый информационный выход процессора j-й строки k ro столбца Р-й матрицы процессоров подключен к вторым входам записи блока двунаправленной передачи данных j é строки k-ro столбца, блока двунаправленной передачи данных j é строки (k + 1)-го столбца, блока двунаправленной передачи данных (j — 1)-й строки k ro столбца блока двунаправленной передачи данных (j + 1)-й строки k-го столбца

3-й матрицы блоков двунаправленной передачи данных и к второму входу записи (j — 1)m + k-го блока двунаправленной передачи даннык 1-й группы, информационный вход процессора

j-й строки k-го столбца 1-й матрицы процессоров подключен к первым выходам блока двунаправленной передачи данных j-й строки k-го столбца блока двунаправленной передачи данных j-й строки (k + 1)-ro столбца, блока двунаправленной передачи данных (j

1)-й строки k-го столбца, блока двунаправленной передачи данных (j +

+ 1)-й строки k-ro столбца 1-.й матрицы блоков двунаправленной передачи данных и к первому выходу (j

1)m + k-го блока двунаправленной передачи данных F-й группы, вход запроса процессора j-й строки k-го столбца f-й матрицы процессоров под- ключен к вторым выходам. блока двунаправленной передачи данных j é строки k-го столбца, блока двунаправленной передачи данных j-й строки (k +

+ 1)-го столбца, блока двунаправленной передачи данных (j — 1)-й строки

k-ro столбца, блока двунаправленной,передачи данных (j "1)-й строки k-го столбца f и матрицы блоков двунаправленной передачи данных и к второму выходу (j -1) m+k-ro блока двунапр авлен ной пе9 1269 редачи данных 1-й группы, третий информационный вход блока двунаправленной передачи данных j-й строки k-ro столбца 3-й матрицы блоков двунаправленной передачи данных подключен к вторым информационным выходам процессора j-й строки (k-1)-го столбца, процессора (j — 1)-й строки k-ro столбца, процессора (j + 1)-й строки

k ro столбца 3-й матрицы процессо- 1g ров, первый вход записи блока двунаправленной передачи данных j-й строки

k-ãî столбца 1-й матрицы блоков двунаправленной передачи данных подключен к четвертым информационным вы- 15 ходам процессора j-й строки (k-1)-го столбца, процессора (j -1)-й строки

k ro столбца, процессора (j + 1)-й .строки k-ro столбца (-й матрицы процессоров, первый адресный вход блока уб двунаправленной передачи данных j-й строки.k-го столбца f-й матрицы бло,ков двунаправленной передачи данных подключен к третьим информационным выходам процессора j-й строки (k — 25

1)-го столбца, процессора (j-1)-й строки k-ro столбца, процессора (j+

+ 1)-й строки k-го столбца 1;-й матри цы процессоров, первый вход чтения блока двунаправленной передачи данных j-й строки К-столбца 3-й матрицы блоков двунаправленной передачи данных подключен к первым информационным выходам процессора j-й строки (k — 1)-го столбца, процессора (j — .1).-й строки k-ro столбца, процессора (j + 1)-й строки k-ro столбца -й матрицы процессоров, третий выход блока двунаправленной передачи данных j-й строки k-го столбца 1-й мат40 рицы блоков двунаправленной передачи данных подключен к информационным

151 10 входам процессора j é строки (k—

1)-го столбца, процессора (j-1)-й строки k-ro столбца, процессора (j + 1)-й строки k-ro столбца 1-й матрицы процессоров, четвертый выход блока двунаправленной передачи данных j-й строки k-го столбца 3-й матрицы блоков двунаправленной переда" чи данных подключен к входам запроса процессора j-й строки (k — 1)-го столбца, процессора (j — 1)-й строки k-го столбца, процессора (j +

+ 1)-й строки k-ro столбца f-й матрицы процессоров,при этом шестой, седьмой и восьмой выходы блока управления подключены соответственно к первому, второму и третьему входам блока ввода-вывода, вход начальных значений блока управления подключен к выходу блока ввода-вывода, при этом в блок управления дополнительно введены первая и вторая группы ключей, информационный вход ключей первой группы подключен к выходу регистра, информационный вход ключей второй группы подключен к выходу ysла памяти, информационному входу блока управления и к входу начальных значений блока управления, выход ключей первой группы подключен к первому и восьмому выходам блока управления и к информационному входу узла памяти, выход ключей второй группы подключен к информационным входам регистра команд и регистра, управляющий вход ключей первой и второй групп подключен к первому выходу узла синхронизации, вход чтения, вход записи узла. памяти, а также второй, четвертый, шестой и седьмой выходы блока управления подключены к второму выходу узла синхронизации.

1 269l 51

Фюc

Фиа J

1 2691 51

12691 51

У гп

РР Рееистр р зу У

pv)-piiurmp чаатичпово рееупетата еd

С- оуниотор ч4

Фий.7

УспоФюмс о)означеиае:

УП-увел лапюти 4е

Гч)- реаистр частичиоао рееиоетатв

PIID- рееиитюр пербоео операп)а 41

РР- реэаетр pnyrtimama ЭУ

С- сУппатор VS

Р40- рееистр Ртвроэе юэерачФа Ф1 ч иЕ.D

1 2691 51

Составитель В.Смирнов

ТехредМ.Ходанич Корректор И.Муска

Редактор А.Ц1ишкина

Заказ 6038/52

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4