Регистр сдвига на мдп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении реверсивных регистров на МДПтранзисторах . Целью изобретения является упрощение регистра и расширение области его применения за счет возможности двунаправленной передачи информации. Для достижения этой цели выход каждого из инверторов , составляющих регистр, через коммутирующие транзисторы соединен с входами последующего и предыдущего инверторов. При этом во время первого такта работы регистра образуются триггеры, состоящие из четного и последующего нечетного инверторов , а во время второго такта работы - из четного и предыдущего нечетного инверторов . 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„Я0„„1269210 (5g 4 G 11 С 19/00

1 ф! рг г зг ю, д

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2!) 3876151/24-24 (22) 01.04.85 (46) 07.11.86. Бюл. № 41 (72) С. В. Быков, Л. Н. Корягин и О. И. Гусаков (53) 681.327.66(088.8) (56) Титце У., Шенк К. Полупроводниковая схемотехника.— М.: Мир, 1982, с. 362, рис. 20.33.

Часы-будильник «Электроника 2-06».

Схема электрическая принципиальная И6МЗ.

495.087ЭЗ. (54) РЕГИСТР СДВИГА НА МДПTPAH3ИСТОРАХ (57) Изобретение относится к вычислительной технике и может быть использовано при построении реверсивных регистров на МДПтранзисторах. Целью изобретения является упрощение регистра и расширение области

его применения за счет возможности двунаправленной передачи информации. Для достижения этой цели выход каждого из инверторов, составляюгциx регистр, через коммутирующие транзисторы соединен с входами последующего и предыдущего инверторов.

При этом во время первого такта работы регистра образуются триггеры, состоящие из четного и последующего нечетного инверторов, а во время второго такта работы-из четного и предыдущего нечетного инверторов. 3 ил.

1269210

Изобретение относится к вычислительной те.хиике.

1се!(ь изобретения — — упрощение регистра сдвига и расширение области его Вримеиеиия путем двуиаправ.н tlHQH передачи информации.

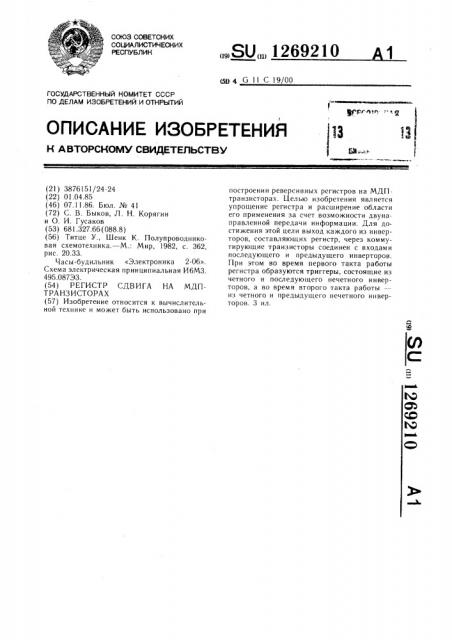

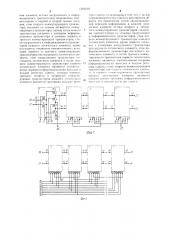

Н 3 ф и . 1 !! р (., ) с т 3 B,l с ! 3 с x (. м с! с д В и Г 3; и 3 фиг.2 — схема одного из вариантов тактироваиия регистра сдвига; В3 фиг.3 — временные диаграммы работы регистра сдвига, нр ивсдеи ного иа фиг.2. so

Регистр сдвига иа МДГ(-транзисторах (фиг.1) содержит логические элементы 1, каждый из которых с<хстоит из нагрузочиого 2 и !(ервого 3 и второго 4 коммутирующих МД11-транзисторов р-типа, информационного 5 и третьего 6 и четвертого 7 коммутирующих МЛ,П-транзисторов п-тина.

Н3 фи;.1 показаны также первая 8 и вторая 9 шины IIHT3IIHH, первый 10, второй 11 и третий 12 входы логического элемента, первый 13, второй 14 и третий 15 выходы логического элемента, первый 16, ьторой 17, третий 18 и четвертый 19 тактовые входы логического элемента. первый 20, второй 21 и третий 22 информационные входы и первый

23, второй 24 и третий 25 ииформаниоиllt>lc Выходы реГистра сдвиГ3. 25

11а фиг.2 приведена схема одного из вариантов тактироваиия регистра сдвига, на которой ((оказаны Восемь тактовых шин 2633, ири этс)м тактовые входы 16 — 19 нечетных

Л О Г И Ч (> С К И Х Э Л (. М С ! Т О В С О(Д H t I (. H bl С Н И ! 3 М И

26 29, а тактовые Входы 16- 19 четных Q логических эледментов — с шинами 30--33

СООТВЕТСТВ H IIO.

11а фиг.3а приведена временная диаграмма работы p(. гистра llpH сдвиге вправо. Здесь

34, 35 сигналы иа входах 20, 2! регистра, 36--43 -- сигналы иа тактовых шинах

26 33 соответственно, а 44, 45 и 46- -48 сигналы на выходах 13, 14 первого и Ва выходах 13 — 15 второго логических элементов соответс твенно.

На фиг.36 приведена временная диаграмма работы регистра Ври сдви "е влево.

Здесь 49 -- сигнал на Входе 22 регистра, 50 — -57 сигналы Ва тактовых шинах 26—

33 соотв TcTBCHHo, а 58 — -60 сигналы Ва выходах !4, 15 и 13 последнего и иредвоследиего логических элементов соответствеHHo. 45

В каждом логическом элементе транзисторы 2 и 5 функционально образуют иивертор, 3 царь! транзисторов 3, 6 и 4, 7 — клю(и. Контакт,8 подключен к шине питания

+Е, а контакт 9 — к шине нулевого tloтеициала. Логическая единица соответствует нанряжеишо +Е, а логический ноль - нулевому потенциалу.

Регистр сдвига работает следую(цим ооразом.

В режиме сдвига вправо (фиг.3а) Ва интервале времени Т! открываются транзисторы 3, 6 нечетных логических элементов.

Если иа входы 20, 21 иостувает логическая единица, то открывается транзистор 5 первого логического элемента и на выходе 14 первого логического элемента устанавливается логический ноль. На интервале времени

Т4 открыты транзисторы 3, 6 четных логических элементов, ири этом открывается транзистор 2 второго логического элемента и на выходе 3 устанавливается логическая единица. На интервале времени Т5 открываются транзисторы 4, 7 четных логических элементов, иа выходе 15 второго логического элемента устанавливается логическая едииица, которая поступает иа затворы транзисторов 2, 5 первого логического элемента. Таким образом инверторы второго и первого логических элементов Ва интервале Т5 образуют триггер. На интервале Т6 так же, как и на интервале ТЗ, закрыты транзисторы ключей всех логических элементов. Г1ри этом за счет сохранения заряда иа затворах транзисторов 2 и 5 ииформация Ве теряется. В следующем периоде Ва интервале Тl открыты транзисторы 3, 4, 6, 5 третьего логического элемента, а иа интервале Т2 открыты транзисторы 2, 4 и 7 данноlo логического элемента. При этом иа интервале Т2 ииверторы третьего и второго логических элементов образуют триггер. На интервалах Tl и Т2 данного периода с входов

20, 21 в первый логический элемент записывается следующий двоичный рязряд входиой информации.

Таким образом, Ва интервалах Тl, Т2 информация записывается в нечетные логические элементы, иа интервале Т2 образуются триггеры иа нечетных и предыдущих четных логических элементах, иа интервалах

Т4, Т5 информация записывается в четные логические элементы, а иа интервале Т5 образуются TpHI ãåðû иа четных и предыдущих нечетных логических элементах.

При сдвиге влево регистр работает аналоги шо режиму сдвига вправо, с той лишь разницей, что иа интервалах Т1, Т2 информация записывается в четные логические элементы, иа интервале Т2 образуются три((еры на четных и последую(цих нечетных 10гических элементах, а иа интервалах Т4, Т5 информация записывается в нечетные логические элементы и на интервале Т5 образуются триггеры на нечетных и на последующих четных логических элементах.

Предлагаемый регистр (фиг.l) может работать также в других режимах тактирования, например Tðåõôàçíîì.

Формула изобретения

Регистр сдвига иа М.(сП-транзисторах, содержащий логические элементы, каждый из которых состоит из нагрузочиого и Вервого и второго коммутирующих транзисторов р-типа и информационного и третьего и четвертого коммутирующих транзисторов Г(-типа, причем в каждом логичес1269210

Щ/Г 1

Д 77

Фаг 2 ком элементе истоки нагрузочного и информационного транзисторов подключены сооТветственно к первой и второй шинам питания, сток второго коммутирующего транзистора соединен со стоком четвертого коммутирую(цего транзистора, затвор нагрузочного транзистора соединен с затвором информационного транзистора и стоками первого и третьего коммутирующих транзисторов, стоки нагрузочного и информационного транзисторов каждого логического элемента, кроме последнего, соединены соответственно с истоками первого и третьего коммутирующих транзисторов последую(цего логического элемента, сток нагрузочного транзистора последнего логического элемента и исток первого коммутирующего транзистора первого логического элемента являются соответственно первыми информационными Выходом и

ВхОдОЧ реГистр а cät)è Га, зс1творы II(t) ВОГО, третьего, второго и четвертого коммутирующих транзисторов каждо(х> логи !Вского элемента являются тактовь(ми Входамп регистра сдвига, от.)ичающш сч тем, что, с целью упрощения реп!стра сдвига и расширения of)ласти его применения путем двунаправленной передачи информации, в каждом логическом элементе истоки второго и четвертого коммутирующих транзисторов соединены соответственно со стоками нагрузочного и информационного транзисторов, сток Второго ком мутиру!О(цего транзистора ка ждого логического элемента, кроме первого, со tlttнен с затворами нагрузочного транзистора предыдущегo логического элемента, сток информационного транзистора последнего логического элемента и исток третьего коммутирующего транзистора первого логического элемента являк>гся соответственно вторыми информационными Выходом и Входом регистра сдвига, стоки второго коммутирующего транзистора llo(. . !Одного логического элем(нT;I и II(рно1 ) к(>х(х(тнрлощеl о тпанзпстора первого логического элемента являк)тся соот Ветсгв 1! II 0 T p(Т ЬН хl И It tip() /1(I;i II IIOI I Ill>1 х> lt

ВЫ Х() l()(I Ii ВХОДО ъ! (>С! ПСTI)<1 (.,Д:ВИ (1.! 2692! 0

+Err

i!

-eu nepal

1-цц перцад Г-Ю периса д

5uz У

Редактор С. Пекарь

Заказ 6043/55

Сос. авитель A. Дерюгин

Гехред И Верес Корректор Е Рошко

Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4