Преобразователь двоичного кода в код системы остаточных классов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Целью изобретения является сокращение количества оборудования. Поставленная цель достигается тем, что в преобразователе двоичного кода в код системы остаточных классов, содержащем вхоДной регистр, блок умножения на два по модулю, сумматор по модулю,первый и второй коммутаторы, первый и второй регистры, первый регист;. используется для приема старших разрядов преобразуемого числа. Это позволяет уменьшить разрядность входного регистра. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН

9271 А1 (19) (11) (51) 4 Н 03 М 7/18

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ И

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3879745/24-24 (22) 08.04.85 (46) 07,11,86. Бюл. № 41 (72) В.А.Иванченко и П.Л.Прокопьев (53) 681.3(088.8) (56) Авторское свидетельство СССР

¹- 9837013 кл. G 06 F 5/02, 1981.

Авторское свидетельство СССР

¹ 1001079, кл. G 06 F 5/02, 1981. (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ (57) Изобретение относится к вычислительной технике. Целью изобретения является сокращение количества оборудования. Поставленная цель достигается тем, что в преобразователе двоичного кода в код системы остаточных классов, содержащем входной регистр, блок умножения на два по модулю, сумматор по модулю,первый и второй коммутаторы, первый и второй регистры, первый регист . используется для приема старших разрядов преобразуемого числа. Это позволяет уменьшить разрядность вход. ного регистра". 1 ил.

126927!

5 !

1S

2S

SO

Иэ обре 1ч ние относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для переводя чисел из двоичнот о кода в код системы оста— точных классов, Цель изобретения — сокращение количества оборудования.

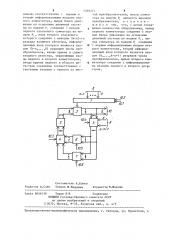

На чертеже представлена схема преобразователя двоичного кода в код системы остаточных классов.

Преобразователь двоичного кода в код системы остаточных классов содержит входной регистр 1, блок 2 умножения на основание двоичной системы по модулю Р,, сумматор 3 по модулю Р;, первый и второй коммутаторы 4 и 5, первый и второй регистры

6 и 7, входы 8 и 9 (k-n,...,0) и (k,,,...,k-п+1) разрядов числа преобразователя, выход 10 преобразовав теля, тактовые входы 10 ° 1 †.6 пре— образователя.

Работа преобразователя основана на том, что выбранный модуль имеет разрядность и+! > log Ð;. При этом любое число В, имеющее разрядность

n„ будет всегдя меньше модуля P

Процесс преобразования двоичного числа х можно представить н виде г х= х modP; = ... L(8,2 modP;,A„„)x 2mod1 . -. „. -А ) 2modP А 1Jmodd

Преобразователь двоичного кода в код системы остаточных классов работает следующим образом, В исходном состоянии коммутатор

5 подключает к входам регистра 6 (k, „,k-n+1) разряды преобразуемоI го числа х, поступающие на вход 9 преобразователя коммутатор 4 подключает к входам блока 2 умножения выходы регистра 6, регистры 6 и 7 обнулены, на входной регистр 1 через информационный вход 8 подаются разряды (k — n...,,0) преобразуемого числа.

В первом такте по сигналам, поступающим на входы 10.1, 10.5 тактовой шины, осуществляется прием преобразуемого числа на входной регистр 6. С регистра 6 разряды преобразуемого числа через коммутатор 4 поступают на вход блока 2 умножения, где они умножаются на дна по модулю и поступают на вход первого слагаемого сумматора 3, на вход второго слагаемого которого поступает разряд (k-и) преобразуемого числа, По окончании переходных процессов на тактовый вход !0.4 поступает сигнал, по которому коммутатор 5 подключает выход сумматора 3 к входам регистров 6 и 7 и в этом состоянии остается до конца преобразования, на вход 10.6. поступает тактовый сигнал, по которому результат х= ((А„ ? +...+А„ 2 ) 2modP +

+А „„шос1Р с сумматора 3 принимается на регистр 7.

В начале второго такта по сигналу, поступающему на вход 10.2 осуществляется сдвиг на один разряд влево содержимого входного регистра

1, Зятем по тактовому сигналу,поступающему на вход 10.3, коммутатор

4 подключает второй информационный вход к блоку 2 умножения. При этом содержимое регистра 7 поступает через коммутатор 4 на блок умножения.

Результат умножения суммируется по модулю на сумматоре 3 со значением (k-n-1)-го разряда преобразуемого числа, поступающего с входного регистра 1. По окончании переходных процессов на вход 10.5 поступает тактоныи сигнал, по которому результат х = ((x, 2)modP;+À,. „,)тос1Р с сумматора 3 принимается и регистр 6, и т.д °

В начале последнего такта осуществляется сдвиг на входном регистре

1 по сигналу, поступающему на вход

10.2, Результат предыдущего такта умножается на блоке 2 умножения и суммируется с А на сумматоре 3.

Окончательный результат снимается с выходов сумматора 3 по модулю.

Формула изобретения

Преобразователь двоичного кода в код системы остаточных классов, содержащий входной регистр разрядностью (k-n+1), блок умножения на основание двоичной системы по модулю

Р; (i=1,2,,„.,1, где 1 — количество оснований системы остаточных классов n+1 > log Р, ),.сумматор по модулю P, первый и второй коммутаторы, первый и второй регистры, причем выходы первого и второго регистров сое12

Составитель А,Клюев

Редактор А,Сабо Техред М.Ходанич Корректор М.Шароши

Заказ 6046/58 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий.

113035, Москва, R-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 динены соответственно с первым и вторым информационными входами пер— вого коммутатора, выход блока умножения на основание двоичной системы по модулю Р; соединен с входом первого слагаемого сумматора по моцулю Р,, вход второго слагаемого которого соединен с выходом (k-и)-го разряда входного регистра, информационный вход которого является входом (k-n,...,0) разрядов числа преобразователя, входы приема и сдвига входного регистра, управляющие входы первого и второго коммутаторов, :Ъ входы приема первого и второго регистров соединены соответственно с тактовыми входами с первого по mec69271 4 той преобразователей, выход сумматора по модулю Р. является выходом

1 преобразователя, о т л и ч а ю шийся тем, что, с целью сокращения количества оборудования, выход первого коммутатора соединен с входом блока умножения на основание двоичной системы по модулю Р;, выход сумматора по модулю Р соединен !

10 с первым информационным входом второго коммутатора, второй информационный вход которого является входом (k,...,k-п+1) разрядов числа преобразователя, выход второго ком15 мутатора соединен с информационными входами первого и второго регистров.