Устройство для измерения коэффициента нелинейности пилообразного напряжения

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„,, 1270728 А1 (51 ) 4 G О! R 29/02 у(»р»г» «у . »

ОПИСАНИЕ ИЗОБРЕТЕНИЯ к лвторСкоЬ У СвидатепьСтву

13, (21) 3905295/24-21 (22) 04.06.85 (46) 15.11.86. Бюл. Ф 42 (71) Научно-исследовательский институт автоматики и элентромеханики при

Томском институте автоматизированных систем управления и радиоэлектроники (72) В.А.Бондарь и А.В.Топор (53) 621.317.351(088.8) (56) Авторское свидетельство СССР

М 805207, кл. G 01 R 29/02, 1979, Авторское свидетельство СССР

Ф 1029105, кл. G 01 R 29/02, 1981. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА НЕЛИНЕЙНОСТИ ПИЛООБРАЗНОГО

НАПРЯЖЕНИЯ (57) Изобретение относится к радиоизмерительной технике. Цель изобретения — повышение точности измерения. Входной сигнал поступает на дифференцирующий каскад 1. Измерение проводится в два этапа. На первом этапе с помощью генератора 2 ступенчатого напряжения производится компенсация составляющей тока конденсатора, пропорциональной максимальной скорости нарастания входного напряжения. Момент полной компенCDc Р!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ сации определяется с помощью компаратора 3 напряжения и компаратора 14 длительности. На втором этапе цифроаналоговый преобразователь 13 меняет режим токового повторителя таким образом, что компенсируется составляющая тока конденсатора, пропорциональная изменению скорости нарастания пилообразного напряжения. В качестве опорного напряжения на вход цифроаналогового преобразователя 13 подается напряжение с выхода генератора

Э

2 ступенчатого напряжения, пропорциональное максимальной скорости нарастания входного сигнала. Момент полC ной компенсации фиксируется вторым ® компаратором 4 напряжения. По окончании второго этапа код на входе циф- ФФФ роаналогового преобразователя 13 пропорционален. коэффициенту нелиней.ности пилообразного напряжения, который определяется как отношение изменения скорости нарастания входного напряжения к максимальной скорос- Я ти нарастания этого напряжения. На а 1 чертеже даны элементы И 5, 6 и 7, счетчик 8, индикатор 9, генератор 10 импульсов блок 11 управления, инвертор 12. 2 з н. ф лы, 2 ил. Об!

270728

Изобретение относится к радиоизмерительной технике и может быть использовано для контроля нелинейности импульсов развертки в телевидении, а также пилообразного напряжения, применяемого в других областях радиоэлектроники.

Цель изобретения — повышение точности измерения путем компенсации погрешности дифференцирования входного сигнала.

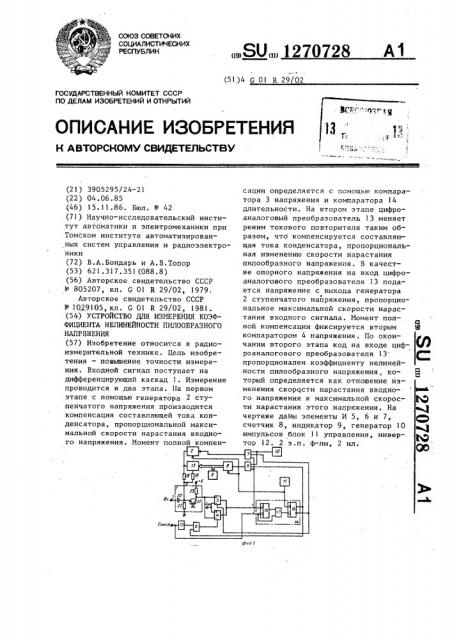

На фиг.l приведена функциональная схема предлагаемого устройства," на фиг.2 — временные диаграммы, поясняющие принцип его работы.

Устройство содержит дифференцирующий каскад 1, первый вход которого образует вход устройства, генератор 2 ступенчатого напряжения, компараторы 3 и 4 напряжения, элемент 5 И, подключенный к объециненным выходам компараторов 3 и 4 напряжения, подключенный к входу стробирования компаратора 4 напряжения элемент 6 И и подключенный к входу генератора 2 ступенчатого напряжения . элемент 7 И, подключенную к вьгходу элемента 5 И цепь из последовательно соединенных счетчика 8 и индикатора 9, а также генератор 10 импульсов, выход которого подключен к объединенным второму и третьему входам элементов 5 и 7 И, блок ll управления, инвертор 12, цифроаналоговый преобразователь 13 и компаратор 14 длительности, состоящий из RS-триггеров 15 и 16, между которыми включен элемент 17 И, вьгходы триггера 16 являются прямым и инверсным выходами компаратора 14 длительности, a Rвход триггера 16 образует установочный вход кампаратора 14 длительности, R-вход триггера 15 образует первый вход компаратора 14 длительности, а S-вход триггера 15 соединен с вторым входом элемента 17 И, образу. ет второй вход компаратора 14 длительности и является входом сиггхронизации устройства, к которому через инвертор 12 подключен элемент б И, выходы компараторов 3 и 4 напряжения подключены к первому:входу элемента 7 И и первому входу компаратора 14 длительности, установоч= ный вход которого объединен с установочными входами генератора 2 ступенчатого напряжения, счетчика 8 и соединен с выходом блока 11 управления, прямой выход подключен к третьему входу элемента 5 И и второму входу элемента б И, а инверсный выход соединен с вгорым входом элемента 7 И и с входом стробиравания компаратора 3 напряжения, причем выход генератора 2 ступенчатого напряжения через резистор 18 соединен с вторым входом дифференцирующего каскада 1 и с входом опорного напряжения цифроаналогового преобразователя 13, информационный вход которого подключен.к выходу счетчика 8, а выход через резистор 19 соединен с вторым входом дифференцирующего каскада 1, выход которого подключен к объединенным неинвертирующему и инвертирующему входам компараторов

3 и 4. Дифференцирующий каскад 1 со о держит конденсатор 20 и токовый повторитель на транзисторе 21, эмиттер которого через резистор 22 подключен к минусу источника питания, база соединена с общей шиной источника питания, а коллектор через резистор

23 подключен к плюсу источника питания и образует выход дифференцирующего каскада 1, первый вывод конденсатора 20 образует первый вход

ЗО дифференцирующего каскада 1, а второй вывод соединен с эмиттером транзистора 2! и образ гет второй вход дифференцирующего каскада 1.

На фиг.2 приведены следующие диаграммы напряжений: 24 — напряжение, поступающее на вход синхронизации устройства; 25 — входное пилообразное напряжение; 26.- выходное напряжение блока 1! управления; 27 — выходное напряжение дифференцирующего каскада 1, 28 — выходное напряжение компараторов 3 и 4 напряжения; 29 напряжение на выходе элемента И 7;

30 — чапряжение на выходе RS-триггера !5; 31 — напряжение на прямом выходе компаратора 14 длительности;

32 — напряжение на выходе элемента

И 5.

Генератор 2 ступенчатого напряжения и цифроаналоговый преобразователь выполнены на микросхемах 153, 155, 572 серий. Коипараторы 3 и 4 напряжения представляют собой микросхему 521 серии, элементы 5 — 7 И, счетчик 8, генератор 10 импульсов, блок !I управления, инвертор 12 и компаратор 14 длительности могут!

270728

Р, Рг Р l0

dUьх

I = С вЂ” —— с

Пгсн р П" т

50 где d— к

3 быть выполнены на микросхемах 155 серии.

Принцип работы устройства основан на том, что информация об изменении скорости нарастания пилообразного напряжения содержится в вершине продифференцированного входного импульса амплитуда которого несег информацию о максимальной скорости нарастания. Ток через конденсатор 20 дифференцирующего каскада 1, определяемый как 5 можно условно разделить на две составляющие: I — ток, пропорциональный максимальной скорости нарастания входного сигнала, и DI — ток, пропорциональный изменению, скорости нарастания входного напряжения. В со20 соответствии с этим можно записать

I = Im AI.

Измерение коэффициента нелинейности производится в два этапа. На

25 первом этапе с помощью генератора

2 ступенчатого напряжения производится компенсация составляющей тока конденсатора I, а на втором этапе с помощью цифроаналогового.преобразователя 13 компенсируется составляющая тока Я.

Устройство работает следующим образом.

В исходном состоянии генератор

2 ступенчатого напряжения, счетчик

8, цифроаналоговый преобразователь

13 и RS-триггер 16 находятся в нулевом состоянии, элементы 5 и 6 И заперты, компаратор 3 напряжения открыт логическим уровнем на его

40 стробирующем входе, а компаратор

4 напряжения заперт. Напряжение 27 на выходе дифференцирующего каскада 1 определяется величинами резисторов 18, 19, 22, 23 и конденсато— ра 20 и может быть рассчитано из выражения

U = Е-I iii Š— e I ° R

21 э коэффициент передачи по току транзистора 21; напряжение источника питания; токи коллектора и эмиттера транзистора 21.

В свою очередь I определяется э формулой где U — напряжение эмиттер-база м. транзистора 21.

Величины резисторов выбраны таким образом, что в исходном состоянии

Uîï э где П„„ — напряжение источника опорного напряжения, подключенного к входам компараторав Зи4.

При подаче на вход устройства пилообразного напряжения 25 через конденсатор 20 начинает протекать ток, под действием которого транзистор 21 запирается и на выходе компаратора 3 появляется напряжение U логической единицы, разрешакщее прохождение импульсов от генератора 10 импульсов через элемент 7 И к генератору

2 ступенчатого напряжения, который, в свою очередь, начинает формировать отрицательное ступенчатое напряжение U „, создающее в цепи эмиттера ток, компенсирующий составляющую тока конденсатора ?„„ причем ступенчатое напряжение формируется только тогда, когда выходное напряжение 27 дифференцирующего каскада 1 больше, чем U „,,т.е. пока на выходе компаратора 3 есть импульсы. Формирование ступенчатого напряжения заканчивается, когда

Момент полной компенсации тока

I< определяется с помощью компаратора 14 длительности, который сравнивает длительность прямого хода пилообразного напряжения 25 (длительность паузы между импульсами синхронизации U ) с длительностью пауз на выходе компаратора 3 напряжения.

Компаратор длительности работает следующим образам.

На входы RS-триггера 15 поочередно поступают импульсы напряжения 28 и 24 с выхода компаратора 3 напряжения и с входа синхронизации устройства. Под действием этих сигналов триггер 15 меняет свое состояние (диаграмма напряжения 30). В момент полной компенсации тока I, т.е. когда Ц,„ > Б на всем прямом ходе исследуемого напряжения, на S-вход

RS-триггера 15 приходят подряд два

5 12707.28 б импульса синхронизации, первый из Р. gI которых устанавливает триггер 15 в N=-„- . — -=К.g, единичное состояние, а второй через элемент 17 И устанавливает в ециничное состояние RS-триггер 16 (диаI, грамма напряжения 31), меняя тем самым состояние выходов компаратора 14 длительности на противоположное. При этом запирается элемент 7 И, отключается компаратор 3 напряжения и под" ключается компаратор 4 напряжения, формирующий на выходе сигнал, разрешающий прохождение импульсов через элемент 5 И на счетчик 8 (диаграмма напряжения 32). Цифроаналоговый пре- !5 Ф î р м у л а и з î б р е т е н и я образователь 13 преобразует коц счетчика 8 в напряжение U+» которое соз- !. Устройство для измерения коэфдает в цепи эмиттера транзистора 21 фициента нелинейности пилообразнодополнительный ток

ro нап яжения со е жа ее и е енR где К=- n — коэффициент нропорциоRq нальности; — коэффициент нелинейности исследуемого пилообразного напряжения.

Код М индицируется индикатором 9. !

0 Необходимое время индикации определяется блоком управления, который формирует сигнал сброса, после которого измерения повторяется.

U n

МАП ь (2) Используя выражения (1), (2) и (3) можно получить

Импульсы напряжения 27 на выходе дифференцирующего каскада 1 начинают . смещаться вверх, Этот процесс процол- 25 жается до тех пор, пока ток полностью не скомпенсирует составляющую тока конденсатора лХ, после чего на выходе компаратора 4 напряжения импульсы не формируются, так как в течение З0 всего прямого хода выполняется условие U „ > 11,,„, а в момент обратного хода импульс синхронизации через инвертор и элемент 6 И, поступая на вход стробирования компаратора 4 наl пряжения, запрещает сравнение входных сигналов, поддерживая выходное напряжение U< на уровне логического нуля. Окончание процесса компснсации nI определяется условием 40 с точностью до одного дискрета цифроаналогового преобразователя 13, а 45 напряжение на выходе цифроаналогового преобразователя 13, с учетом того, что в качестве опорного на него подается напряжение U „, определяется выражением 50

U = — — --- ° N

1 п спп ппвп . (3) где и. — разрядность цифроаналогового преобразователя 13;

N — код на выходе счетчика 8. др щ дффр цирующий каскад, первый вход которого образует вход устройства, генератор ступенчатого напряжения, последовательно соединенные первый компаратор напряжения, первый элемент И, счетчик и индикатор, а также генератор импульсов, выход которого подключен к второму входу первого элемента И, и блок управления, выход которого соединен с установочными входами генератора ступенчато-о напряжения и счетчика, о т л и— ч а ю щ е е с я тем, что, с целью повышения точности измерения, в него введены первый и второй резисторы, источник опорного напряжения, инвертор, второй и третий элементы И,, второй компаратор напряжения, цифроаналоговый преобразователь и компаратор длительности, при этом к входу синхронизации устройства через инвертор подключен второй элемент И, выход которого соединен с входом . стробирования второго компаратора напряжения, выход которого подключен к выходу первого комиаратора напряжения, к первому входу третьего элемента И и первому входу компаратора длительности, второй вход которого подключен к входу синхрониза -. ции устройства, установочный вход соединен с выходом блока управления, прямой выход подключен к третьему входу первого элемента И и второму входу второго элемента И, а инверсный выход соединен с вторым входом третьего элемента И и с входом стробирования первого компаратора напряжения, .причем выход генератора сту1270

728

Составитель Н.Михалев

Редактор Н.Киштулинец Техред И.Попович Корректор А.Обручар

Заказ 6240/49 Тираж 728 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическ е предприятие, г.Ужгород, ул.Проектная, 4

7 пенчатого напряжения через первый резистор соединен с вторым, входом дифференцирующего каскада и с входом опорного напряжения цифроаналогового преобразователя, информационный вход кот рого подключен к выходу счетчика, а выход через второй резистор соединен с вторым входом дифференцирующего каскада, выход которого подключен к объединенным неинвертирующему входу первого и инвертирующему входу второго .компараторов напряжения, а инвертирующий вход первого компаратора напряжения и неинвертирующий вход второго компаратора напряжения также объединены и подключены к источнику опорного напряжения, кроме того, выход генератора импуль— сов соединен с третьим входом второго элемента И, выход которого под- щ ключен к входу генератора ступенчатого напряжения.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что дифференцирующий каскад содержит конденсатор 25 и токовый повторитель на транзисторе, эмиттер которого через резистор подключен к минусу источника питания, база соединена с общей шиной источника питания, а коллектор через резистор подключен к плюсу источника питания и образует выход дифференцирующего каскада, первый вывод конденсатора образует первый вход дифференцирующего каскада, а второй вывод соединен с эмиттером транзистора и образует второй вход дифференцирующего каскада.

3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что компаратор длительности выполнен в виде последовательно соединенных первого

RS-триггера, элемента И и второго

RS-триггера, выходы которого являются прямым и инверсным выходами компаратора длительности, à R-вход этого триггера образует установочный вход компаратора длительности, Rвход первого RS-триггера образует первый вход компаратора длительности, а S-вход этого триггера, соединенный с вторым входом элемента И, является вторым входом компаратора длительности.