Устройство для вывода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано для вывода данных из электронных клавишных вычислительных машин во внешние блоки памяти. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается введением в устройство второго элемента И, преобразователя кода, распределителя импульсов , формирователя пачки импульсов. Преобразователь кода содержит элемент НЕ, шифратор, первую и вторую группы элементов И и элементы ИЛИ. Введенные блоки позволяют выводить информацию с естественной в клавишных ЭВМ формой представления чисел с учетом плавающей запятой, с учетом того, что информация динамически изменяется, а синхросигналы представлены в фазоим (Л пульсном коде. 1 з.п. ф-лы, 3 ип.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (594 С 06 F 13 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

°

ЮЮ

\Ю

Ф

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3900066/24-24 (22) 22.05.85 (46) 15.11.86. Вюл. У 42 (72) К.М.Ценных и В.П.Кучеренко (53) 681.327.8(088.8) (56) Кофрон Дж. Технические средства микропроцессорных систем. М.: Мир, 1983, с. 155.

Патент Японии Р 57-31173, кл. G 06 F 3/00, 1982,,(54) УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники и может быть использовано для вывода данных из

„„SU„r,1270762 А1 электронных клавишных вычислительных машин во внешние блоки памяти. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается введением в устройство второго элемента И, преобразователя кода, распределителя импульсов, формирователя пачки импульсов.

Преобразователь кода содеркит элемент

НЕ, шифратор, первую и вторую группы элементов И и элементы ИЛИ. Введенные блоки позволяют выводить информацяо с естественной в клавишных ЭВМ формой представления чисел с учетом плавающей запятой, с учетом того, что + информация динамически изменяется, а Е синхросигналы представлены в фазоимпульсном коде. 1 з.п. ф-лы. 3 ил.

Изобретение относится к вычислительной технике и может быть использовано для вывода данных из электронных клавишных вычислительных машин .во внешние блоки памяти.

Целью изобретения является повышение быстродействия.

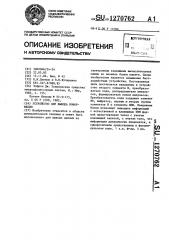

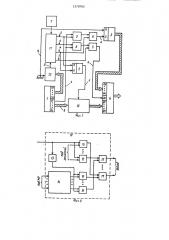

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2— блок-схема преобразователя кодов; на фиг. 3 — диаграммы работы устройства.

Устройство с6держит (фиг. 1) микропроцессор 1, с которого выводится .информация, триггер 2, счетчик 3, блок 4 памяти, первый и второй элементы ИЛИ 5 и 6, генератор 7, первый и второй элементы И 8 и 9, преобразователь 10 кода, распределитель 11 импульсов, формирователь 12 пачек импульсов. Кроме того, устройство содержит (фиг. 2) элемент НЕ 13, шифратор 14, первую и вторую группы элементов И 15 и 16, элементы ИЛИ 17.

Устройство для вывода информации работает следующим образом.

В исходном состоянии счетчик 3 и формирователь 12 пачки импульсов заблокированы сигналом логической

"1", по шине "Вывод". Выходная информация микропроцессора 1 появляется поразрядно на его выходах и поступает на преобразователь 10 кода, а фазоимпульсно-кодированные разрядные сигналы микропроцессора 1 поступают .на входы формирователя 12 пачки импульсов.

С приходом сигнала "Вывод" (фиг.

3 а) снимается блокировка со счетчика 3, а формирователь 12 формирует пачку импульсов (фиг. 3 б), числа которых соответствуют числу разрядов выводимой информации. Причем первый импульс в пачке совпадает по Фазе с разрядным сигналом, соответствующим младшему (старшему) разряду выводимой информации, второй импульс совпадает со следующим разрядным сигналом и т.,д.

Передним фронтом каждого импульса из пачки запускается распределитель

11 импульсов, который вырабатывает четыре импульса, сдвинутых относительно один другого на один такт выходной частоты генератора 7 (фиг. Зд, е, ж, з), Первым из этих импульсов триггер 2 устанавливается в единичное состояние, третьим сбрасывается в нулевое состояние (фиг. 3 л),, а

270762 преобразователь 10 кода в первом случае выдает код запятой, во втором — преобразованный код разряда выходной информации микропроцессора 1.

Сигналы (фиг. 3 к), поступающие на счетный вход" счетчика 3 с выхода элемента ИЛИ 6 устанавливают адрес блока 4 памяти, а сигналы (фиг. 3 к)

10 с элемента ИЛИ 5 осуществляют запись информации в блок 4 памяти. Однако запись кода запятой возможна лишь в том случае, когда с выхода запятой микропроцессора 1 на входы элементов И 8

15 и 9 поступит разрешение (сигнал запятой). В этом случае за время действия разрядного сигнала адрес блока 4 памяти изменяется дважды, и дважды поступит сигнал записи

20 (фиг. 3 и, к). Первым сигналом осуществляется запись кода запятой, а вторым — запись информации, соответствующей данному разрядному сигналу.

По окончании последнего импульса

25 формирователя 12 и сигнала "Вывод" устройство переходит в исходное состояние.

Для нормального функционирования устройства сигнал "Вывод" должен

30 быть длительностью не менее двух периодов частоты разрядных сигналов, в противном случае возможен вывод не всех разрядов информации.

Код знака выводится аналогично разряду числовой информации. При использовании устройства для вывода такой информации, код запятой

v которой выводится в отдельном такте, а синхросигналы представлены число-импульсным кодом, необходимо обеспечить подачу на входы элеменИ 1т тов И 8 и 9 сигнала логического 0

В этом случае код запятой будет выводиться аналогично разряду числовой информации.

Преобразователь кода 10 (фиг. 2) содержит шифратор 14, элемент НЕ 13, первую и вторую группу элементов

И 15 и 16 и элементы ИЛИ 17. Шифратор

14 предназначен для преобразования выходного кода микропроцессора 1.

Так при использовании микропроцессоров К145 серии необходимо преобразовать выходной семисегментный код в более удобный для дальнейшей обработки, например 2/10 код. Шифратор в этом случае может гредставлять собой

1270762 о

2 =А-Е ° В ° E G;

2 = А F В Е;

2 = А ° В ° F ° G; комбинационную схему, реализующую следующие зависимости: г

2 =В F А ° Е Г А-Gгде2,2

2, 2 — разряды 2/10 кода; г

ABEFG — переменные сегментного кода °

В зазисимости от сигнала триггера

2, поступающего на первые входы первой группы элементов И 15 и через элемент НЕ 13 — на первые входы второй группы И 16 элементов на выходе преобразователя 10 кода присутствует преобразованный код микропроцессора 1, либо код запятой, который предварительно устанавливается на вторых входах первой группы элементов И 15.

Положительный эффект от введения в предлагаемое устройство новых узлов и блоков заключается в возможности вывода с микропроцессоров во внешние блоки памяти информации с естественной формой представления чисел, у которой код запятой появляется в соФ отв етст в ующем т акте одн о в р ем ен н о с разрядом выводимой информации и информации, представленной в динамическом виде, а синхросигналов — в фазоимпульсном коде °

Формула изобретения

1. Устройство для вывода информации, содержащее триггер, счетчик, блок памяти, первый и второй элементы ИЛИ, генератор и первый элемент

И, выход которого соединен с первым входом1 первого элемента ИЛИ, выходы счетчика соединены с входами первой группы блока памяти, выходы которого являются выходами устройства, выход второго элемента ИЛИ соединен с вторым входом счетчика, второй вход второго элемента ИЛИ соединен с вторым .входом триггера, 5

50 о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены второй элемент И, преобразователь кода, распределитель импульсов, формирователь пачки импульсов, входы группы и вход которого являются соответственно входами первой группы и первым входом устройства, первый вход счетчика соединен с входом формирователя пачки импульсов, выход которого соединен с первым входом распределителя импульсов, первый выходкоторого соединен с первым входом триггера и вторым входом второго элемента И, первый вход которого соединен с вторым входом первого элемента И и является вторым входом устройства, выход генератора импульсов соединен с вторым входом распределителя импульсов, второй, третий и четвертый выходы которого соединены соответственно с первым входом первого элемента И, вторым входом триггера и вторым входом первого элемента ИЛИ, выход последнего соединен с входом блока памяти, входы второй группы которого соединены с выходами преобразователя кода, входы группы которого являются входами второй группы устройства, выход триггера соединен с входом преобразователя кода, выход второго элемента И соединен с первым входом второ го элемента ИЛИ.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что преобразователь кода содержит шифратор, элемент НЕ, первую и вторую группу элементов И, элементы ИЛИ, выходы которых являются выходами преобразователя кода, входы шифратора и вторые входы элементов И первой группы являются входами группы преобразователя кода, вход элемента НЕ соединен с первыми входами элементов И первой группы и является входом преобразователя кода, выходы шифратора соединены соответственно с вторыми входами элементов И второй группы, первые входы которых соединены с выходом элемента НЕ, выходы элемента И пер- вой и второй групп соединены соответственно с входами элементов ИЛИ.

1270762

Фиг.2

1270762

Составитель И. Дубинина

Редактор Ю. Середа Техред Л.Сердюкова Корректор В. Синицкая

Подписное

Тираж 671

Заказ 6244/51

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул.. Проектная. 4