Функциональный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в управляющих системах и гибридных вычислительных устройствах . Изобретение позволяет расширить функциональные возможности устройства , содержащего реверсивный счетчик, два блока суммирования, четыре элемента И, цифроаналоговый преобразователь , блок сравнения, за счет введения в него триггера знака, регистра показателя степени, дешифратора, пересчетного блока и генератора тактос (О вых импульсов. 2 з.п. ф-лы. 2 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (5D 4

ОПИСАНИЕ ИЗОБРЕТ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 2097554/24-24 (22) 21.01,75 (46) 15.11.86. Бюл. У 42 (71) Ордена Ленина институт кибернетики АН УССР (72) В.П, Боюн, Л.Г. Козлов .. и А.В. Писарский (53) 681.325(088.8) (56) Авторское свидетельство СССР

11 503260, кл. G 06 J 3/00, 1974.

„„SU„„1270776

r 54) ФУНКЦИОНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к области вычислительной техники и может быть использовано в управляющих системах и гибридных вычислительных устройствах. Изобретение позволяет расширить функциональные возможности устройст-. ва, содержащего реверсивный счетчик, два блока суммирования, четыре злемента И, цифроаналоговый преобразователь, блок сравнения, за счет введения в него триггера знака, регистра показателя степени, дешифратора, пересчетного блока и генератора такто— вых импульсов. 2 з.п. ф-лы. 2 ил.

1270776

Изобретение относит ся к вычислительной технике и может бьп ь исполь— зовано в управляющих системах и гиб— ридных вычислительных устройствах.

Целью изобретения является расширение функциональных возможностей за счет получения одновременно кода непрерывной величины Х, кода функции

lпх и кода функции х, где z - целое положительное или отрицательное

1О число.

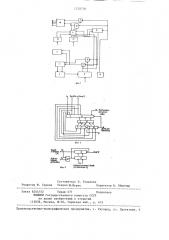

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 — функциональная схема блока суммирования; на фиг. 3 — функ15 циональная схема пересчетного блока.

Устройство содержит первый блок

l суммирования, цифроаналоговый преобразователь 2, блок 3 сравнения„ генератора 4 тактовых импульсов, первый 5 и второй 6 элементы И, реверсивный счетчик 7, пересчетный блок 8, четвертый 9 и третий 10 эле— менты И, дешифратор 11, регистр 12 показателя степени, триггер 13 зна25 ка, второй блок 14 суммирования .

Блоки 1 и 14 суммирования (фиг. 2) содержат сумматор 15, состоящий из и разрядов младшей, и разрядов старшей и двух разрядов целой частей, группу ИЛИ 16, первую !7 и вторую

l8 группы элементов И.

Выходы прямого кода целой и старшей частей сумматора 15 являются выходами блока 14 суммирования и инфор-- 35 мационными входами первой группы элементов И 17 прямого кода, выходы которой подключены к первым входам группы элементов ИЛИ 16, выходы которой соединены с входами двух младших разрядов старшей части и и-разрядами младшей части сумматора 15 . Выходы обратного кода целой и старшей частей сумматора 15 соединены с информационными входами второй группы элементов И 18 обратного кода, выходы которой подключены к вторым входам группы элементов ИЛИ 16.

Пересчетный блок 8 содержит счетчик 19, элемент ИЛИ 20, группу зле в 50 ментов И 21.

По сигналу начальной установки и по каждому импульсу переполнения счетчика 19 производится занесение дополнительного кода показателя сте- 55 пени z в счетчик 19 с регистра 12 заносится обратный код числа х и добавляется единица в младший разряд счетчика 19. При поступлении на первый вход пересчетного блока 8

N-тактовых импульсов, на выхоце формируется N/z импульсов переполнения, т.е, на входы блока суммирования 1 управляющие импульсы поступают в раз чаще, чем на входы блока суммирования 14, Предлагаемое устройство работает в соответствии с формулами х;, =х, „2 х;;

1 (1)

y(Уп где х, — текуг ее значение аргумента в первом блоке 1 суммирования;

g„=sign(х-х; ) - знак разности между аналоговым значением входной величины х и текущим цифровым значением х„„ вырабатываемый блоком 3 сравнения;

P,==sign(z) — знак показателя степени записываемый в триггер 13 знака; у, — текущее значение функции

t.

1n х в реверсивном счетчике

7 у." — текущее значение функции

z 1n х, которая реализуется в устройстве с помощью пересчетного блока 8, но значение которой в устройстве не представлено; у, — текупее значение функции х z в блоке 14 суммирования.

Выражение у„,, =у:,1 ° e.kz2 ) реализуется в устройстве на основании того, что блок 14 работает в z раз чаще„ чем блок 1, что соответствует возведению х в степень z. Суперпозиция знаков С„ и Е реализуется дешифратором !1, при этом учитывается, что к значению функпии с .z ln х на каждом такте работы должно прибавляться или вычитаться z единиц младшего разряда со знаком Е . Ez.что соответствует приближению функции

p,- z 1n,1+ F„2 " ) первым членом ее разложения в ряд Тейлора. Синхронно с этой неявной операцией и выполняется операция у, =у (1w < с 2 ) ь 1 1 что достигается применением пере— счетного блока 8, регистра 12 показателя степени и триггера 13 знака.

При этом оценка методической погрешности по аргументу на один такт работы блока 1 составляет: у .- — 2 " а по функции

127077б венно, выходы которого являются первыми выходными шинами, а третий вход объединен с третьим входом первого

fzgj t — 2

Работа предлагаемого устройства может быть проиллюстрирована на примере вычисления, например, функции у=х в следящем режиме, при разряд2 1О ности в устройстве n=4.

Формула изобретения

1. Функциональный аналого-цифровой преобразователь, содержащий реверсивный счетчик, два блока суммирования, четыре элемента И, цифроаналоговый преобразователь и блок сравнения, первый вход которого является входной шиной, второй вход соединен с выходом цифроаналогового преобразователя, а первый и второй выходы соединены с первыми входами первого и второго элементов И соответственно, выходы которых соединены с первым и вторым входами реверсивного счетчика соот— ветственно, отличающийся тем, что, с целью расширения функциональных возможностей, в преобразо- З0 ватель введены триггер знака, ре гистр показателя степени, дешифратор, пересчетный блок, генератор тактовых импульсов, выход которого соединен с первыми входами третьего и четвер- З того элементов И и через пересчетный блок со вторыми входами первого и второго элементов И, выходы которых соединены с первым и вторым входами первого блока суммирования соответст-40 венно, а первые входы объединены с первым и вторым входами дешифратора соответственно, третьи входы которо— го соединены с выходами триггера знака, вход которого является второй 45 входной шиной, первый и второй выходы дешифратора соединены со вторыми ,входами третьего и четвертого элементов И соответственно, выходы которых подключены к первому и второму входам50 второго блока суммирования соответстблока суммирования и является третьей входной шиной, выходы первого блока суммирования соединены с выходами цифроаналогового преобразователя, вход регистра показателя степени является четвертой входной шиной, а выходы соединены со вторыми входами пересчетного блока.

2. Преобразователь по п. 1, о тл и ч а ю шийся тем, что блоки суммирования выполнены íà (2n+2)-разрядном сумматоре, группе элементов

ИЛИ, двух группах элементов И, первая группа выходов сумматора является выходами блока суммирования и соединена с первыми входами первой группы элементов И, выходы которой подключены к первым входам группы элементов ИЛИ, выходы которой соединены с группой входов сумматора, вторая группа выходов сумматора соединена с первыми входами второй группы элементов И, выходы которой подключены ко вторым входам группы элементов ИЛИ, первым и вторым входами блока суммирования являются вторые входы первой и второй групп элементов И соответственно, второй вход второй группы элементов И объединен со вторым входом сумматора, третий вход которого является третьим входом блока суммирования.

3. Преобразователь по п. 2, о т л и ч а ю шийся тем, что пере— в счетный блок выполнен на счетчике импульсов, группе элементов И и элементе ИЛИ, первый вход которого соединен с выходом счетчика импульсов и является выходом пересчетного блока, второй вход является входом начальной установки, а выход соединен с первыми в входами счетчика и группы элементов

И, вторые входы последней являются вторыми входами пересчетного блока, а выходы соединены со вторыми вхрдами счетчика импульсов, третий вход которого является первым входом пересчетного блока.

1270776

8ыхюби (кблаку5) фее Я

ДЬааи

r,в)

8adguvwvrnd уамм8 мнрарнпционкые ЬиЬ (стражди П)

Составитель И. Романова

Редактор Ю. Середа Техред И.Верес Корректор А. Обручар

Заказ 6245/52 Тираж 671 Подписное BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул . Проектная, 4