Преобразователь параллельного кода в последовательный

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при автоматизированном программируемом обмене массивами данных между устройствами, одно из которых работает в параллельном , а другое в последовательном коде. Цель изобретения - расширение класса решаемых задач за счет возможности преобразования наперед запрограммированного массива данных, состоящего из m слов с переменным как по числу слов, так и по числу разрядов в слове, форматом. Цель достигается благодаря -введению в устройство блока памяти, первого и второго счетчиков импульсов, схемы сравнения, коммутатора кода адреса, триггера режима, элемента И-НЕ с соответствующими связями. 1 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5D 4 Н 03 М 9 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3721812/24-24 (22) 05.04.84 (46) 15. 11.86. Бюл. У 42 (72) В.Г.Киясов, В.В.Кузнецов и Н.Г.Руфина (53) 681.325(088.8) (56) Авторское свидетельство СССР

Ф 1119002, кл. G 06 F 5/04, 1983.

Авторское свидетельство СССР

Ф 860056, кл. G 06 F 5/04, 1979, (54) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО

КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ (57) Изобретение относится к автоматике и вычислительной технике и может быть испальэовано при автома— тизированном программируемом обмене

„„SU f270897 А 1 массивами данных между устройствами, одно из которых работает в параллельном,а другое — в последовательном коде Цель изобретения — расширение класса решаемых задач за счет возможности преобразования наперед запрограммированного массива данных, состоящего из m слов с переменным как по числу слов, так и по числу разрядов в слове, форматом. Цель достигается благодаря введению в устройства блока памяти, первого и второго счетчиков импульсов, схемы сравнения, коммутатора кода адреса, триггера режима, элемента И-НЕ с соответствующими связями. 1 ил.

1270897

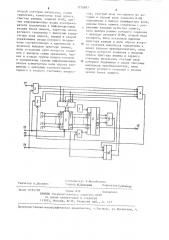

На чертеже представлена функциональная схема преобразователя.

Схема сод ерх<и т r е нерат ор 1 импульсов, первый 2 и второй 3 счетчики импульсов, схему 4 сравнения,коммутатор 5 кода адреса, блок 6 памяти, элемент И-НЕ 7, регистр 8 сдвига дешифратор 9 нуля, триггер 10 режима, входы 11 — 14, выход 15 преобразователя.

Прецлагаемый преобразователь кода обеспечивает обработку массива,цанных, состоящего из числа от 1 до ш, каждое из которых содержит от 1 до и двоичных разрядов. Максимальное число, устанавливаемое на выходе счетчиков 2 и 3, составляет m-1.

Преобразователь кода имеет два режима работы: первый режим — программирование, т.е. запись в блок памяти 6 массива данных", второй режим — автономный режим преобразования параллельного кода в последовательный.

Переключение режимов производится триггером 10 режима работы, Регистр 8 сдвига в зависимости от уровня сигнала, подаваемого на его вход выбора режима, работает в двух режи 4ах: при уровне логической "1" — запись, при уровне логического "0"— сдвиг.

Преобразователь работает следуюmHì образом.

Перед программированием на вход

14 сброса преобразователя подается сигнал сброса на первый счетчик 2 и триггер 10 режима работы, заставляя последний переключиться на режим программирования, при котором сигнал с его единичного выхода, подаваемый на первый управляющий вход коммута20

Изобретение относится к автоматике и вычислительной технике и может быть использовано при автоматизироf ванном программируемом обмене масси" вами данных между устройствами, одно из которых работает в параллельном, а другое — в последовательном коде.

Цель изобретения — расширение класса решаемых задач за счет возможности преобразования наперед запро1О граммированного массива данных, состоящего из m слов с переменным как по числу слов, так и по числу разрядов в слове, форматом.

l 15 тора 5, заставляет последний подключить выходы первого счетчика 2 ко входам выборки адресов блока 6 памяти, а сигнал с нулевого выхода триггера 10 режима работы, подаваемый на второй управляющий вход коммутатора 5, отключает выходы второго счетчика 3 от входов выборки адресов блока 6. Программирование заключается в том, что на входы преобразователя кода подается п-разрядное слово в параллельном коде, которое при подаче на вход 13 записи блока 6 сигнала записи записывается в ячейку блока 6 с нулевым адресом, В нулевой разряд блока 6 записывается логический "0", При подаче в процессе программирования на вход первого счетчика 2 импульса последний увеличивает свой выходной код на единицу, который через коммутатор 5 подается на входы выборки адресов блока 6.

Таким образом, блок 6 подготавливается для записи второго слова в ячейку с адресом, равным единице. Запись второго слова в блок 6 производится описанным выше методом, причем в нулевой разряд блока 6 снова записывается логический "0". Таким образом, массив данных в параллельном коде, состоящий из заданного числа слов, I записывается в ячей-.<и блока 6, причем в нулевые разряды последнего. всегда записывается логический "0", независимо от кодовой комбинации, составляющей информационное слово. После записи в блок 6 последнего слова массива данных на вход первого счетчика 2 подается импульс, и преобразователь кода оказывается готовым к преобразованию записанного массива дан-! ных.

Для запуска режима преобразования на вход 12 запуска преобразователя подается отрицательный импульс на

О второй вход элемента 7 И-НЕ, на сброс второго счетчика 3 и на вход установки единицы триггера 10 режима работы, логические сигналы на выходах которого, подаваемые на управляющие входы коммутатора 5,, изменяются на противоположные, отключая входы выборки адресов блока 6 от выходов первого счетчика 2 и подключая их к выходам второго счетчика 3. Поскольку второй счетчик 3 импульсом сброса обнуляется по выходам, на входы выборки адресов через блок 6 поступает

1270

3 нулевой код, соответствующий адресу нулевой ячейки блока памяти 6. Таким образом, на вход регистра 8 сдвига с блока 6 будет подаваться параллельный код, соответствующий первому слову, а также логический 0" в нулевом разряде. Поступивший на второй вход элемента 7 И-HE пусковой импульс на время его действия переведет регистр 8 сдвига в режим записи, и на выходе последнего появится параллельный код, соответствующий первому слову, а также логический "0" в нулевом разряде, старший разряд и слова будет присутствовать на выходе 15 15 преобразователя кода. Снимаемый с нулевого разряда регистра 8 сдвига логический "0 независимо от кода слова поддерживает на выходе дешифратора 9 нуля сигнал логической "1", который, будучи поданным на первый вход элемента 7 И-НЕ, совместно с восстановившейся после пускового импульса логической "1" на втором его входе, устанавливает на его выходе, а, следовательно, на входе выбора режима регистра 8 сдвига сигнал лоI гического "0", переводящий регистр 8 сдвига в режим сдвига ° Поступающие с генератора 1 импульсы продвигают записанную в регистре сдвига информа. цию к выходу 15 преобразователя кода, осуществляя, таким образом, преобразование параллельного кода в последовательный, снимающийся с выхода 15 преобразователя кода. Пос3S ле каждого такого. импульса записанный в нулевом разряде регистра 8 сдвига сигнал логического "0" при этом также перемещается к выходу 15, 40 поддерживая на выходе дешифратора 9 нуля сигнал логической "1", При этом разряды регистра 8 сдвига заполняются логической "1", После пре— образования первого (последнего по счету) разряда слова на всех входах дешифратора 9 нуля оказываются сигналы логической "1", а на выходе — сигнал логического "0". Перепад с уровня логической 1 на уровень логический "0", подающийся на вход второго счетчика 3, заставляет его увеличить номер ячейки блока 6 на 1, т,е. выставить на выходах блока 6 параллельный код, соответствующий второму слову, при этом в нулевом разряде сохраняется сигнал логического "01, Появившийся на выходе дешифратора 9 нуля перепад, пройдя че897 ф рез элемент 7 И-НЕ, перево,",ит регистр 8 сдвига в режим записи. На выходах регистра 8 сдвига появляется второе слово, а сигнал 0" в нулевом разряде обеспечивает на выходе дешифратора 9 нуля появление перепада с уровня логического "0" на уровень логической "1", На обоих входах элемента 7 И-НЕ оказываются уровни логической "1", а на выходе — уровень логического "0", переводящий регистр

8 сдвига в режим сдвига. Начинается преобразование второго слова, и описанный процесс повторяется. После окончания преобразования последнего слова выходной код второго счетчика

3 оказывается одинаковым с выходным кодом первого счетчика 2, т.е. число преобразованных слов становится равным числу слов, записанных в блок

6 при программировании. На выходе схемы 4 сравнения, сравнивающей выходные коды первого и второго счетчиков, появляется сигнал, устанавливающий триггер 10 режима работы в исходное состояние, соответствующее режиму программирования, т.е. преоб- . разователь кода устанавливается в исходное состояние. Перед программированием следующего массива данных нет необходимости в подаче сигнала сброса на вход 14 сброса. Если требуется повторно преобразовать какой-либо массив данных, то на вход

12 пуска преобразователя необходимо подать только пусковой им— пульс.

Ф о р м у л а и з о б р е т е и и я

Преобразователь параллельного кода в последовательный, содержащий регистр сдвига, дешифратор нуля, põàäû которого соединены с выходами разрядов, за исключением старшего, р егистра сдвига, г енера тор импул ьсов, выход которого соединен со входом сдвига регистра сдвига, выход старшего разряда которого является информационным выходом преобразователя, о т л и чающий с я тем, что, с целью расширения класса решаемьгх задач за счет возможности преобразования наперед запрограммированного массива данных, состоящего из m слов с переменным как по числу слов, так и по числу разрядов в слове, форматом, введены блок памяти, первый и

1270897

Составитель Н. (!!елобанова

- ехред N.Попович Корректор С.йекмар

Редактор А.Долинич

Заказ 6254/58 1 и 3cl!K 8 1 6 Подписное

БНИИПИ Государственно -o комитета СССР по делам изобретений и открытий

113035,.Москва, Н(-35, Раушская наб., д, 4/5

Производственно-полиграфическсе предприятие, г,ужгород, ул,1!роектная, второй счетчики импульсов, схема сравнения, коммутатор кода адреса, триггер режима, элемент И-НЕ, причем информационные входы преобразователя подключены к информационным входам блока памяти, адресные входы которого соединены с выходами коммутатора кода адреса, первый и второй управляющие входы которого подключены соответственно к единичному и нулевому выходам триггера режима, вход установки нуля которого соединен с выходом схемы сравнения., первая и вторая группы входов которой и одноименные группы информационных входов коммутатора кода адреса соединены с выходами соответственно первого и второго счетчиков импульсов, счетный вход последнего из которых и первый вход элемента И-НЕ подключены к выходу дешифратора нуля, выходы блока памяти соединены с раэ— ряд ными входами регистра сдвига, вход выбора режима которого соединен с выходом элемента И-HF., второй вход которого, вход установки единицы триггера режима и вход сброса второго счетчика импульсов подключены к входу запуска преобразователя, вход сброса которого соединен с входами сброса триггера режима и первого счетчика импульсов, счетный вход которого подключен к входу тактовых импульсов преобразователя, вход записи которого соединен с входом записи блока памяти.