Цифровой анализатор спектра

Иллюстрации

Показать всеРеферат

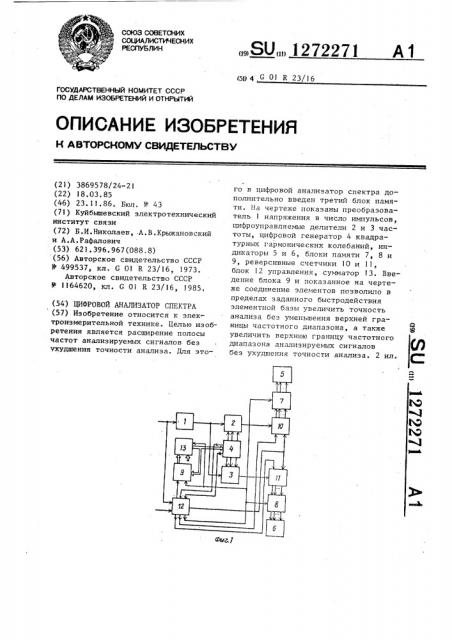

Изобретение относится к электроизмерительной технике. Целью изобретения является расширение полосы частот анализируемых сигналов без ухудшения точности анализа. Для этого в цифровой анализатор спектра дополнительно введен третий блок памяти . На чертеже показаны преобразователь 1 напряжения в число импульсов, дифроуправляемые делители 2 и 3 частоты , цифровой генератор 4 квадратурных гармонических колебаний, индикаторы 5 и 6, блоки памяти 7, 8 и 9, реверсивные счетчики 10 и II, блок 12 управления, сумматор 13. Введение блока 9 и показанное на чертеже соединение элементов позволило в пределах заданного быстродействия элементной базы увеличить точность анализа без уменьшения верхней грас ницы частотного диапазона, а также увеличить верхнюю границу частотного (Л диапазона а.нализируемых сигналов без ухудшения точности анализа. 2 ил. to lN3 ю

(ЩОЭ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУ6ЛИН (50 4,С 01 К 23/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3869578/24-21 (22) 18.03.85 (46) 23.11.86. Бюл. 11- 43 (7I) Куйбьппевский электротехнический институт связи (72) Б.И.Николаев, .А.В.Крыжановский и А.А,Рафалович (53) 621.396.967(088.8) (56) Авторское свидетельство СССР

У 499537, кл, G 01 R 23/16, 1973.

Авторское свидетельство СССР

Р 1164620, кл. G Ol R 23/16, 1985. (54) ЦИФРОВОЙ АНАЛИЗАТОР СПЕКТРА (57) Изобретение относится к электроиэмерительной технике. Целью изобретения является расширение полосы частот анализируемых сигналов беэ ухудшения точности анализа. Для это„„SU„„1272271 А 1 го в цифровой анализатор спектра дополнительно введен третий блок памяти. На чертеже показаны преобразователь 1 напряжения в число импульсов, цифроуправляемые делители 2 и 3 частоты, цифровой генератор 4 квадратурных гармонических колебаний, индикаторы 5 и 6, блоки памяти 7, 8 и

9, реверсивные счетчики 10 и 11, блок 12 управления, сумматор 13. Введение блока 9 и показанное на чертеже соединение элементов позволило в пределах заданного быстродействия элементной базы увеличить точность анализа без уменьшения верхней границы частотного диапазона, а также увеличить верхнюю границу частотного диапазона анализируемых сигналов без ухудшения точности анализа. 2 ил.

1 127

Изобретение относится к электроизмерительной технике, и может найти применение в радиотехнике, акустике и технике связи.

Целью изобретения является расширение полосы частот исследуемых сигналов беэ ухудшения точности анализа.

На фиг.l приведена функциональная схема цифрового анализатора спектра, на фиг.2 — временные диаграммы, поясняющие работу анализатора спектра.

Устройство состоит из преобразователя I напряжения в число импульсов, цифроуправляемых делителей 2 и 3 частоты, цифрового генератора 4 квадратурных гармонических колебаний, индикаторов 5 и б, блоков памяти 7 — 9, реверсивных счетчиков 10 и 11, блока

12 управления и .сумматора 13, m-разрядные выходы гeíåðàòoðà 4 соединены с установочными т-разрядными входами цифроуправляемых делителей 2 и 3 частоты, выходы которых соединены с информационными входами реверсивных счетчиков 10 и II соответственно, а частотные входы делителей соединены между собой и с выходом преобразователя 1 напряжения в число импульсов.

Выходы счетчиков 10 и 11 соединены с входами блоков 7 и 8 памяти, выходы которых в свою очередь подключаются к индикаторам 5 и б соответственно. Первый вход блока 12 управления соединен с входом преобразователя 1 напряжения в число импульсов, второй и третий входы — со знаковыми выходами генератора 4, а четвертый вход является синхронизирующим входом анализатора. Первый выход блока

12 управления соединен с объединенпли управляющими входами блоков 7

8 памяти, третьим входом блока 9 памяти и вторым входом сумматора 13, второй выход — с вторым входом блока 9 памяти, третий выход — с обнуляющими входами реверсивных счетчиков 10 и 11, а четвертый и пятый выходы — с входами управления направлением счета реверсивных счетчиков 10 и 11 соответственно. Выход блока 9 памяти через сумматор 13 соединен с первым входом блока 9 памяти и с адресным входом генератора 4.

Третий вход сумматора. 13 является управляющим входом анализатора.

2271 лизируемого сигнала средствами аналого-цифровой техники.

Устройство работает следующим образом.

Анализируемый сигнал S(t) преобразователем 1 преобразуется в пачки импульсов. Число импульсов в пачках пропорционально дискретным значениям исследуеМого сигнала в последователь10 ные моменты времени t;. Полученные выборки исследуемого сигнала S(t;), представленные в виде числа импульсов, поступают на первые входы цифроуправляемых делителей 2 и 3 частоты.

15 На установочные входы этих делителей от генератора 4 поступают коды отсчетов квадратурных гармонических колебаний в последовательные моменты времени sin КяС; и cos КуТ; (где К—

20 номер измеряемой гармоники). На выходе каждого цифроуправляемого делителя образуются новые пачки импульсов, число импульсов в которых И,(t,.) и

Nz(t;) для каждого момента времени

25 1„ с точностью до постоянного множителя равно произведению числа входных импульсов и входного кода: !

N,(t;) = — Б() 81п Ку е

11 (t ) = --„-, S(t;) cos K t;, где m - -число разрядов цифроуправляемого делителя частоты.

З5 Реверсивные счетчики 10 и 11, направление счета которых определяется блоком 12 управления в зависимости от знаков исследуемого сигнала и генерируемых опорных напряжений, осу40 ществляют алгебраическое суммирование пачек импульсов с выходов делителей 2 и 3. Опорные напряжения, генерируемые генератором 4, подаются на второй и третий входы блока управления, а на первый вход поступает исследуемый сигнал. Сигналы управления реверсивными счетчиками 10 и 11 снимаются соответственно с четвертого и пятого выходов блока управления.

В конце периода исследуемого сигнала 5(6) на выходах счетчиков формируются коды спектральных коэффициентов анализируемого сигнала.

Работа устройства основана на реализации преобразования Фурье ана1

a„= --- . S(t;) cos Кы t;

? 72271

После этого коротким импульсом блока управления, снимаемым с первого выхода, осуществляется запись содержимого счетчиков !О и 11 в блоки

7 и 8 памяти. Этим же импульсом обну- 5 ! ляются блок 9 памяти и сумматор 13 °

После этого задержанным импульсом, снимаемым с третьего выхода блока управления, счетчики 10 и II обнуляются. Задержка необходима для то!

О

ro чтобы до обнуления счетчиков информация с их выходов была переписана в блоки памяти. В то же время задержка не должна быть значительной, чтобы не внести погрешность в измерение спектральных коэффициентов.

После обнуления счетчиков процесс определения спектральных коэффициентов повторяется.

На четвертый вход блока 12 управления подается синхросигнал с частотой, равной частоте первой гармоники анализируемого сигнала. У большинства исследуемых объектов (например, в виброметрии) такой синхросигнал имеется. В противном случае его можно выделить из самого исследуемого сигнала известными методами, например с помощью управляемых фильтров.

Формирование опорных колебаний генератором 4 происходит следующим образом.

На адресный вход генератора 4 поступает код с выхода сумматора 13. На один вход этого сумматора поступает код с выхода блока 9 памяти, а на другой вход — код номера анализируемой гармоники. В блок 9 памяти записывается код с выхода сумматора 13 4!! при поступлении очередного тактового импульса с второго выхода блока управления. Таким образом, если исходные состояния блока 9 памяти и сумматора 13 нулевые, то выходной 45 код сумматора последовательно возрастает от нулевого состояния до полного заполнения сумматора, причем шаг возрастания равен коду номера измеряемой гармоники. Генератор 4 квад-50 ратурных колебаний представляет собой постоянное запоминающее устройство (ПЗУ), на адресные входы которого поступает выходной код сумматора 13, а с выходов снимаются коды отсчетов 55 квадратурных гармонических колебаний.

Номер отсчета задается адресным кодом (выходным кодом сумматора 13).

Процесс формирования опорных синусоидальных колебаний 3-х кратных частот иллюстрируется временными диаграммами на фиг ° 2. Косинусоидальные колебания формируются аналогичным образом. По оси абсцисс отложены коды на адресных входах генератора 4. Из фиг.2 видно, что при формировании опорного .колебания самой низкой частоты (1-й гармоники) шаг адресного кода равен 1, при формировании 2-й гармоники равен 2, при формировании 3-й гармоники равен 3 и т.д. Под шагом адресного кода здесь понимается разность между номерами соседних отсчетов. Таким образом, mar адресного кода совпадает с номером измеряемой гармоники. Благодаря этому обстоятельству возможно простое цифровое управление частотой опорных колебаний, обеспечивающее измерение гармоник определенных кратностей исследуемого сигнала. Для измерения К-й гармоники достаточно лишь на третий вход сумматора 13 подать код числа К. В конце периода исследуемого сигнала, когда сформированы коды спектральных коэффициентов а, и bK, блок 9 памяти и сумматор 13 обнуляются импульсом с первого выхода блока управления.

В предлагаемом устройстве в отличие от известного число дискретных отсчетов на одном периоде опорного колебания при кратном изменении его частоты не остается постоянным, а уменьшается пропорционально номеру измеряемой гармоники. Поэтому частота тактовых импульсов, снимаемых с второго выхода блока управления, не меняется при измерении гармоник различных кратностей, которое сопровождается формированием опорных колебаний с частотами тех же кратностей.

Это обстоятельство позволяет увеличить число отсчетов опорного колебания самой низкой частоты до максимальпого значения, возможного при заданном быстродействии элементной базы. Поскольку в этом случае число отсчетов достаточно велико, то методическая погрешность измерения 1 — и гармоники мала. При измерении всех последующих гармоник методическая погрешность остается неизменной и равной погрешности измерения l é гармоники.

71 б дикаторов через соответствующие блоки памяти, вторые входы которых связаны с первым выходом блока управления, а третий и четвертый выходы цифрового генератора квадратурных гармонических колебаний соединены с вторым и третьим входами блока управления, третий выход которого соединен с вторыми входами реверсивных счетчиков, а четвертый и пятый выходы блока управления — с третьими входами соответствующих реверсивных счетчиков, отличающийся тем, что, с целью расширения полосы частот анализируемых сигналов без ухудшения точности анализа, в него введен третий блок памяти, выход которого через сумматор соединен с первым входом этого блока памяти и с входом цифрового генератора квадратурных гармонических колебаний, причем второй вход третьего блока памяти соединен с вторым выходом блока управления, объединенные второй вход сумматора и третий вход третьего блока памяти соединены с первым выходом блока управления, а третий вход сумматора является управляющим входом .анализатора спектра.

% 12722

Таким образом, указанное соединение элементов позволяет в пределах заданного быстродействия элементной базы увеличивать точность анализа без уменьшения верхней границы частотного диапазона и, наоборот, увеличивать верхнюЮ границу частотного диапазона анализируемых сигналов без ухудшения точности анализа.

1О

Формула из обретения

Цифровой анализатор спектра, содержащий соединенные с входом блок управления и преобразователь напряже- 15 ния в число импульсов, а также два цифроуправляемых делителя частоты, два реверсивных счетчика, два блока памяти, два индикатора и цифровой генератор квадратурных гармонических 211 колебаний, первый и второй m-разрядные выходы которого связаны с первымн m-разрядными входами цифроуправ,ляемых делителей частоты, вторые вхо2S ды которых соединены между собои и с выходом преобразователя напряжения в число импульсов, а выход — с первыми входами реверсивных счетчиков, выходы которых связаны с входами инВ!2

Составитель И.Янушевский

Редактор Н.Гунько. Техред А.Кравчук

Корректор Е.Сирохман

Заказ 6335/45 Тираж 728

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4